电工电子基础实验 (计数与分频电路) PPT

- 格式:ppt

- 大小:658.00 KB

- 文档页数:30

电工电子实验报告课程名称:电工电子基础实验B实验名称:计数与分频电路学院:计算机学院班级:学号:姓名:指导教师:学期:2019-2020 学年第2 学期电工电子实验教学中心一、实验目的1.掌握中规模集成电路计数器的逻辑功能及应用。

2.掌握用74LS161构成任意进制计数器的方法。

3.掌握数字电路多个输出波形相位关系的正确测试方法。

4.了解不均匀周期信号波形的测试方法。

二、主要仪器设备及软件软件:Multisim软件硬件:电脑三、实验原理(或设计过程)3.1 计数器工作原理计数器的基本功能是记忆加在输入端上的时钟脉冲个数。

但它的用途很广,不仅可以用来统计输入脉冲的数目,对输入脉冲进行分频,而且还可以用它来完成定时操作、数字运算、代码转换以及产生脉冲波形等特定任务。

3.2 用74LSl61设计M=7的计数器,测试并记录CP、QA、QB、QC、QD各点波形用模N的计数器构成模M的计数器(N>M),一般采用同步置数的方法。

可采用置最小数法、置“0”法和置最大数法。

基本思想是使计数器从预置状态开始计数,当计到满足模值为M的终止状态时产生置数控制信号,下一CP周期进行置数,重复计数过程,从而实现模M的计数。

3.3 设计一个分频比N=5的整数分频电路,观察并记录时钟和输出波形。

可考虑使用74LS161构成一个M=5的计数器,从M=5计数器的最高位获得N=5分频后的输出波形。

此波形的占空比是非对称的。

如下图:FinFout为了获得对称占空比的N=奇整数分频波形(N=5),可先设计一个M=|N/2|(取整)的计数器,再添加一个异或门和一个D触发器。

电路及波形如下FinF(N/2)Fout3.4 设计一个1110010的序列信号发生器,观察并记录时钟和输出波形考虑使用74LS161构成一个M=7的计数器,将计数器的输出送给数据选择器74153作为地址信号,在74153的数据输入端接入相应的序列信号码值,则74153的输出端就可以产生连续变化的序列信号。

计数与分频电路一、 实验目的1、用74LS161设计M=7的计数器,测试并记录CP ,QA ,QB ,QC ,QD 各点波形。

2、设计一个分频比为N=5的整数分频电路,观察并记录时钟和输出波形。

3、用MUX 产生“1110010010”序列信号,用示波器双踪观察并记录时钟和序列信号波形。

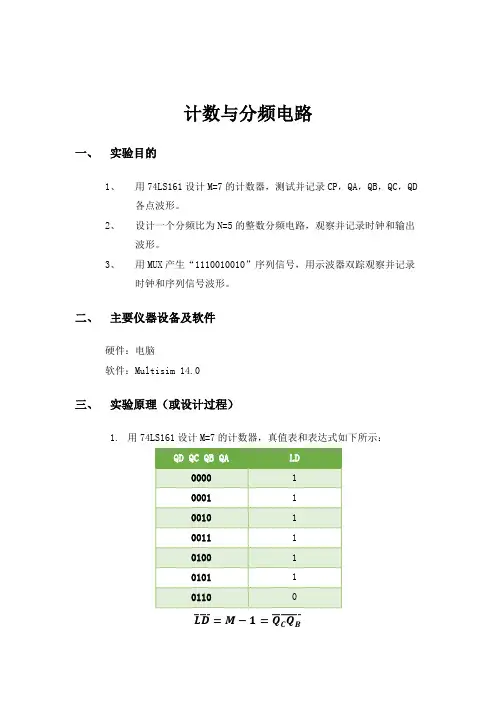

二、 主要仪器设备及软件硬件:电脑软件:Multisim 14.0三、 实验原理(或设计过程)1. 用74LS161设计M=7的计数器,真值表和表达式如下所示:LD ̅̅̅̅=M −1=Q C Q B ̅̅̅̅̅̅̅̅2. 设计一个分频比为N=5的整数分频电路,真值表和表达式如下所示:LD̅̅̅̅=Q ̅C 3. 用MUX 产生“1110010010”序列信号,首先设计一个M=10的计数器,真值表如下所示:有真值表可得公式:LD ̅̅̅̅=Q D Q A ̅̅̅̅̅̅̅̅由此,计数器部分设计好了,能够产生M=10的循环地址,但是要用数据选择器74151来进行序列输出,地址输入端不够用,于是要用降维来实现功能:降维后的卡诺图(降D)得到降维后的卡诺图,就可以根据它连接电路图以实现序列输出功能了。

四、实验电路图1.用74LS161设计M=7的计数器电路图如图所示:2.设计一个分频比为N=5的整数分频电路,电路图如下所示:3.用MUX产生“1110010010”序列信号,电路图如下所示:五、实验数据分析和实验结果1.用74LS161设计M=7的计数器,测试并记录CP,QA,QB,QC,QD各点波形如下所示:如上图可知,实验数据符合理论值。

2.设计一个分频比为N=5的整数分频电路,观察并记录时钟和输出波形如图所示:如上图所示,实验数据符合五分频电路理论值。

3.用MUX产生“1110010010”序列信号,用示波器双踪观察并记录时钟和序列信号波形如下图所示:如上图可知,实验数据符合理论值。

六、实验小结通过本次实验,我学习到了更多计数器,分频器和序列发生器的原理和使用方法,以及“清0法”和“置0法”的原理。