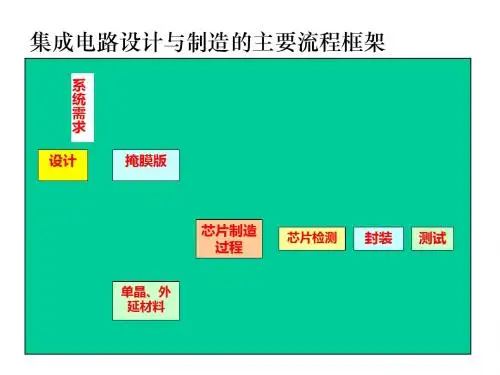

第四阶段:时序验证与版图设计 任务:静态时序分析从整个电路中提取出所有 时序路径,然后通过计算信号沿在路径上的延 迟传播,找出违背时序约束的错误(主要是 SetupTime 和 HoldTime),与激励无关。在深亚 微米工艺中,因为电路连线延迟大于单元延迟, 通常预布局布线反复较多,要多次调整布局方 案,对布局布线有指导意义。 流程:预布局布线(SDF文件)--网表仿真(带延时 文件)--静态时序分析--布局布线--参数提取-SDF文件--后仿真--静态时序分析--测试向量生 成。

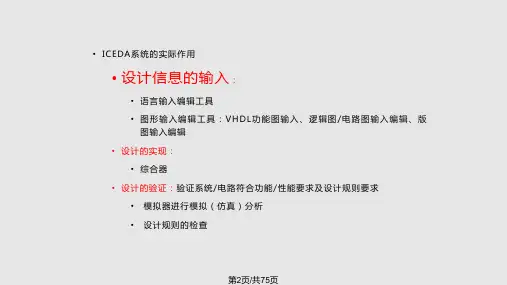

第一阶段:项目策划 任务:形成项目任务书 (项目进度,周期管理等)。流 程:市场需求--调研--可行性研究--论证--决策--任务 书。 第二阶段:总体设计 任务:确定设计对象和目标,进一步明确芯片功能、 内外部性能要求,参数指标,论证各种可行方案,选 择最佳方式,加工厂家,工艺水准。 流程:需求分析--系统方案--系统设计--系统仿真。 输出:系统规范化说明(System Specification):包括系 统功能,性能,物理尺寸,设计模式,制造工艺,设计周期, 设计费用等等.

流程:逻辑设计--子功能分解--详细时序框图--分块 逻辑仿真--电路设计(算法的行为级,RTL级描述)-功能仿真--综合(加时序约束和设计库)--电路网表-网表仿真。 输出: 功能设计(Function Design):将系统功能的实现方案 设计出来.通常是给出系统的时序图及各子模块之 间的数据流图。 逻辑设计(Logic Design):这一步是将系统功能结构 化.通常以文本(Verilog HDL 或VHDL),原理图,逻辑 图表示设计结果,有时也采用布尔表达式来表示设 计结果。 电路设计(Circuit Design):电路设计是将逻辑设计表 达式转换成电路实现。