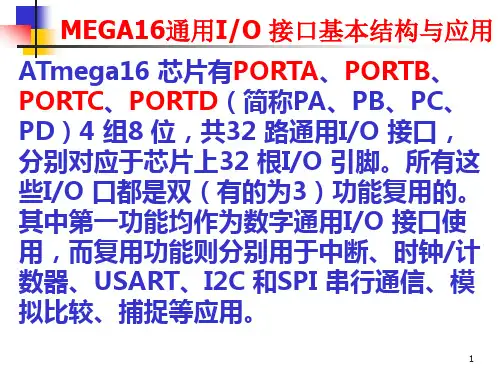

ATMEGA16的IO端口

- 格式:doc

- 大小:60.50 KB

- 文档页数:3

ATMEGAL16二、寄存器(1)I: 全局中断使能I=1:允许全局中断C=0:禁止全局中断(2)T:位复制存储将寄存器某一位复制到T,或将T复制到寄存器某一位(3)H:半进位标志位H=1:低4位向高4位有进位H=0:低4位向高4位无进位(4)S:符号位S=N异或V(5)V:2进制补码溢出标志V=1:2进制补码有溢出V=0:2进制补码无溢出(6)N:负数标志位N=1:结果是负数N=0:结果是正数(7)Z:零标志Z=1:结果是零Z=0:结果不是零(二、三)SPH,SPL:堆栈指针堆栈区的初地址,SPL是低8位,SPH是高8位(1)SE:睡眠使能SE=1:使能睡眠模式SE=0:禁止睡眠模式SRE:外部扩展使能(2)SM2,SM1,SM0:睡眠模式选择JTD=1:JTAG测试使能JTD=0:禁止JTAG测试(2)ISC2:外中断2触发方式ISC2=1:上升沿中断ISC2=0:下降沿中断(3)JTRF:JTAG测试复位标志JTRF=1:JTAG复位JTRF=0:JTAG没复位(4)WDRF:看门狗复位标志WDRF=1:看门狗复位WDRF=0:看门狗没复位(5)BORF:掉电检测复位标志BORF=1:掉电检测复位BORF=0:没掉电(6)EXTRF:外部引脚复位标志EXTRF=1:外部引脚复位EXTRF=0:外部引脚没复位(7)PORF:上电复位标志PORF=1:上电复位PORF=0:没上电复位(六)SFIOR:特殊功能(2)ACME:模拟比较器多路复用器使用标志ACME=1:ADC多路复用器为模拟比较器选择负极输入ACME=0:AN1连接到比较器负极(3)PUD:禁止上拉电阻PUT=1:禁止上拉电阻PUT=0:允许上拉电阻(4)PSR2:T/C2预分频复位PSR2=1:T/C0预分频复位PSR2=0:不操作(5)PSR10:T/C1或0预分频复位PSR10=1:T/C1或0预分频复位PSR10=0:不操作(七、八)EEARH ,EEARL:EEPROM地址EEARH是高地址,EEARL是低地址(九)EEDR:EEPROM读写的数据EERIE=1:允许EEPROM中断EERIE=0:禁止EEPROM中断(2)EEMWE:EEPROM写使能EEMWE=1:允许EEPROM写EEMWE=0:禁止EEPROM写(3)EEWE:写EEPROMEEWE=1:写EEPROMEEWE=0:无操作(4)EERE:读EEPROMEERE=1:读EEPROMEERE=0:无操作当PORTnn置位时是高电平。

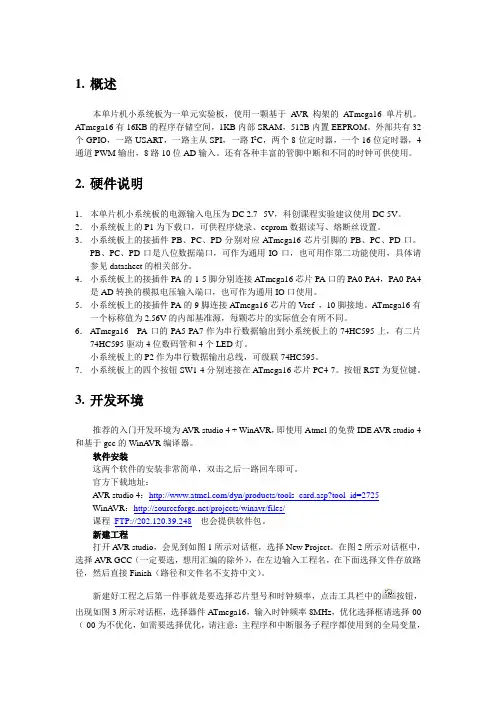

1.概述本单片机小系统板为一单元实验板,使用一颗基于A VR构架的A Tmega16单片机。

A Tmega16有16KB的程序存储空间,1KB内部SRAM,512B内置EEPROM。

外部共有32个GPIO,一路USART,一路主从SPI,一路I2C,两个8位定时器,一个16位定时器,4通道PWM输出,8路10位AD输入。

还有各种丰富的管脚中断和不同的时钟可供使用。

2.硬件说明1.本单片机小系统板的电源输入电压为DC 2.7--5V,科创课程实验建议使用DC 5V。

2.小系统板上的P1为下载口,可供程序烧录、eeprom数据读写、熔断丝设置。

3.小系统板上的接插件PB、PC、PD分别对应A Tmega16芯片引脚的PB、PC、PD口。

PB、PC、PD口是八位数据端口,可作为通用IO口,也可用作第二功能使用,具体请参见datasheet的相关部分。

4.小系统板上的接插件PA的1-5脚分别连接A Tmega16芯片PA口的PA0-PA4,PA0-PA4是AD转换的模拟电压输入端口,也可作为通用IO口使用。

5.小系统板上的接插件PA的9脚连接A Tmega16芯片的V ref ,10脚接地。

A Tmega16有一个标称值为2.56V的内部基准源,每颗芯片的实际值会有所不同。

6.A Tmega16 PA口的PA5-PA7作为串行数据输出到小系统板上的74HC595上,有二片74HC595驱动4位数码管和4个LED灯。

小系统板上的P2作为串行数据输出总线,可级联74HC595。

7.小系统板上的四个按钮SW1-4分别连接在A Tmega16芯片PC4-7。

按钮RST为复位键。

3.开发环境推荐的入门开发环境为A VR studio 4 + WinA VR,即使用Atmel的免费IDE A VR studio 4和基于gcc的WinA VR编译器。

软件安装这两个软件的安装非常简单,双击之后一路回车即可。

官方下载地址:A VR studio 4:/dyn/products/tools_card.asp?tool_id=2725WinA VR:/projects/winavr/files/课程FTP://202.120.39.248也会提供软件包。

串口寄存器介绍USART I/O 数据寄存器- UDRUSART 发送数据缓冲寄存器和USART 接收数据缓冲寄存器共享相同的I/O 地址,称为USART 数据寄存器或UDR。

将数据写入UDR 时实际操作的是发送数据缓冲器存器(TXB),读UDR 时实际返回的是接收数据缓冲寄存器(RXB) 的内容。

在5、6、7 比特字长模式下,未使用的高位被发送器忽略,而接收器则将它们设置为0。

只有当UCSRA寄存器的UDRE标志置位后才可以对发送缓冲器进行写操作。

如果UDRE没有置位,那么写入UDR 的数据会被USART 发送器忽略。

当数据写入发送缓冲器后,若移位寄存器为空,发送器将把数据加载到发送移位寄存器。

然后数据串行地从TxD 引脚输出。

接收缓冲器包括一个两级FIFO,一旦接收缓冲器被寻址FIFO 就会改变它的状态。

因此不要对这一存储单元使用读- 修改- 写指令(SBI 和CBI)。

使用位查询指令(SBIC 和SBIS)时也要小心,因为这也有可能改变FIFO 的状态。

USART 控制和状态寄存器A -UCSRA• Bit 7 – RXC: USART 接收结束标志(中断)接收缓冲器中有未读出的数据时RXC 置位,否则清零。

接收器禁止时,接收缓冲器被刷新,导致RXC 清零。

RXC 标志可用来产生接收结束中断( 见对RXCIE 位的描述)。

• Bit 6 – TXC: USART 发送结束发送移位缓冲器中的数据被送出,且当发送缓冲器 (UDR) 为空时TXC 置位。

执行发送结束中断时TXC 标志自动清零,也可以通过写1 进行清除操作。

TXC 标志可用来产生发送结束中断( 见对TXCIE 位的描述)。

• Bit 5 – UDRE: USART 数据寄存器空UDRE标志指出发送缓冲器(UDR)是否准备好接收新数据。

UDRE为1说明缓冲器为空,已准备好进行数据接收。

UDRE标志可用来产生数据寄存器空中断(见对UDRIE位的描述)。

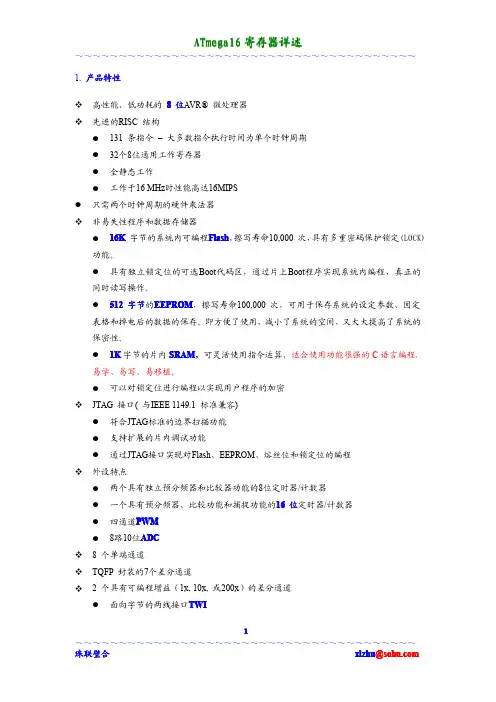

ATmega16 简介ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态; ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声; Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

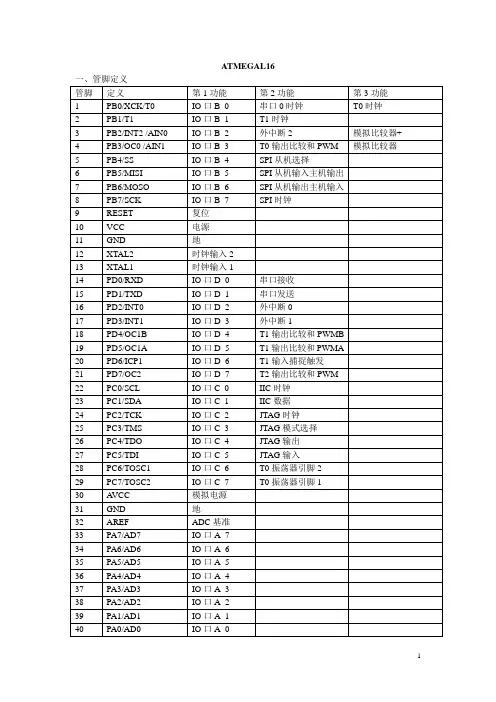

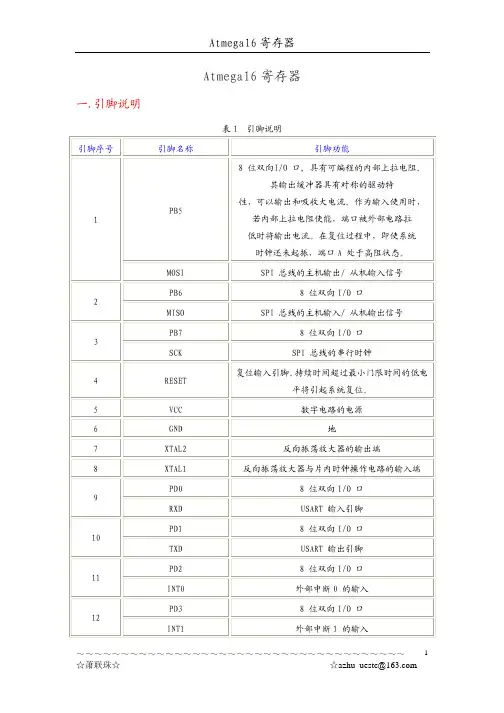

引脚功能说明:

VCC 数字电路的电源

GND地

端口A(PA7..PA0) 端口A 做为A/D 转换器的模拟输入端

端口B(PB7..PB0) 端口B 为8 位双向I/O 口,具有可编程的内部上拉电阻

端口C(PC7..PC0)端口C 为8 位双向I/O 口,具有可编程的内部上拉电阻。

端口D(PD7..PD0)端口D 为8 位双向I/O 口,具有可编程的内部上拉电阻RESET复位输入引脚。

持续时间超过最小门限时间的低电平将引起系统复位

XTAL1反向振荡放大器与片内时钟操作电路的输入端。

XTAL2反向振荡放大器的输出端。

AVCC AVCC是端口A与A/D转换器的电源。

不使用ADC时,该引脚应直接与VCC连接。

使用ADC

时应通过一个低通滤波器与VCC 连接。

AREF A/D 的模拟基准输入引脚。

A VR学习笔记(基于LT_Mini_M16)一、点亮发光二极管一、实验内容和目的本实验通过硬件电路和软件程序,利用ATMega16单片机来控制发光二极管的点亮和熄灭。

通过此实验初步掌握单片机的I/O口功能。

二、硬件电路1、电路分析(对照LT_Mini_M16原理图)1)电源电路:外接稳压直流电源(最好是DC9V)加到电路的U1处,经过电容C16稳压滤波后加到稳压模块AMS1117-5.0上,然后连接到电源开关按钮S1,从开关按钮出来后经过发光二极管D9和电阻R7,再经过电容C1、C2、C3、C4、C5、C7稳压滤波后加到单片机以及各个模块的电源端。

分析:a) 电容的作用是稳压滤波,其中C1、C2、C3、C4、C5这5电容为0.1PF (俗称104电容,一般为瓷片电容)。

主要作用为滤出电源电路中的高频成分;而C16、C7是电解电容,主要作用是稳压,即把电源电路中的尖峰电压拉低到正常电压水平;C16是稳定外接直流电源的电压(9V),C7是稳定AMS1117-5.0输出的5V电压。

b)稳压芯片采用ASM1117-5.0,该稳压芯片输入电压范围为6.5V-15V,输出电压稳定在5.0+0.1V,最大输出电流可达1A,可以满足一般电路需要。

c) 电源开关按钮S1的作用当然是接通和断开电源了。

在此电路中S1采用的是单刀双掷开关,一旦断开电源,则电源的正负极都断开了。

d)发光二极管D9的作用是指示电源是否连接成功,如果外部电源成功的连接上,则发光二极管发光指示电源连接成功;电阻R7的作用是对发光二极管进行限流,一般发光二极管只能通过10mA左右的电流,且发光二极管上面的压降只需要1.5V左右,加到发光二极管上面的电流如果超出额定值,则会烧毁。

而系统工作的电压是5V,如果全部加在发光二极管上,则发光二极管很容易就会被烧毁。

所以要在电源和发光二极管之间串接一个限流电阻。

该限流电阻阻值的计算:(VCC-发光二极管上的电压)/流过发光二极管的电流。

端口A端口B引脚配置如下:•SCK –端口B, Bit 7SCK:SPI 通道的主机时钟输出,从机时钟输入端口。

工作于从机模式时,不论 DDB7 设置如何,这个引脚都将设置为输入。

工作于主机模式时,这个引脚的数据方向由DDB7 控制。

设置为输入后,上拉电阻由PORTB7控制。

•MISO –端口 B, Bit 6MISO:SPI 通道的主机数据输入,从机数据输出端口。

工作于主机模式时,不论DDB6 设置如何,这个引脚都将设置为输入。

工作于从机模式时,这个引脚的数据方向由DDB6 控制。

设置为输入后,上拉电阻由PORTB6控制。

•MOSI –端口 B, Bit 5MOSI: SPI 通道的主机数据输出,从机数据输入端口。

工作于从机模式时,不论DDB5 设置如何,这个引脚都将设置为输入。

当工作于主机模式时,这个引脚的数据方向由 DDB5控制。

设置为输入后,上拉电阻由PORTB5控制。

•SS –端口 B, Bit 4SS: 从机选择输入。

工作于从机模式时,不论DDB4 设置如何,这个引脚都将设置为输入。

当此引脚为低时SPI 被激活。

工作于主机模式时,这个引脚的数据方向由DDB4 控制。

设置为输入后,上拉电阻由PORTB4控制。

• AIN1/OC0 –端口 B, Bit 3AIN1,模拟比较负输入。

配置该引脚为输入时,切断内部上拉电阻,防止数字端口功能与模拟比较器功能相冲突。

OC0,输出比较匹配输出:PB3 引脚可作为T/C0比较匹配的外部输出。

实现该功能时,PB3 引脚必须配置为输出( 设DDB3 为1) 。

在 PWM模式的定时功能中, OC0 引脚作为输出。

• AIN0/INT2 –端口 B, Bit 2AIN0,模拟比较正输入。

配置该引脚为输入时,切断内部上拉电阻,防止数字端口功能与模拟比较器功能相冲突。

INT2,外部中断源 2 : PB2 引脚作为MCU的外部中断源。

• T1 –端口B, Bit 1T1, T/C1 计数器源。

ATmega16寄存器状态寄存器——SREGI:全局中断触发禁⽌位,为中断总控制开关。

T:通⽤标志位,⽤户⾃定义。

H:半进位标志位。

S:符号标志位。

V:溢出标志位。

N:负数标志位。

Z:零标志位。

C:进/借位标志位。

通⽤中断控制寄存器——GICRINT1:外部中断1使能。

INT0:外部中断0使能。

INT2:外部中断2使能。

IVSEL:中断向量表选择。

当IVSEL=0时,中断向量区的位置定义在FLASH的开始处;当IVSEL=1时,定义在引导程序载⼊区的起始处。

IVCE:中断向量表转移允许位。

必须在IVCE位被写⼊1后的4个时钟周期内,修改IVSEL。

4个时钟周期后,或IVSEL位写⼊后,IVCE位由硬件⾃动清零。

OCIE2:T/C2输出⽐较匹配中断使能位。

TOIE2:T/C2溢出中断使能位。

TICIE1:T/C1输⼊捕获中断使能位。

OCIE1A:T/C1输出⽐较A中断使能位。

OCIE1B:T/C1输出⽐较B匹配中断使能位;TOIE1:T/C1溢出中断使能位。

OCIE0:T/C0输出⽐较中断使能位。

TOIE0:T/C0溢出中断使能位。

TIFR寄存器中的各个中断标志是与TIMSK中的使能位⼀⼀对应。

当SPMIE位被置位,若状态寄存器中的I位也被置位时,SPM完成中断即被使能。

只要SPMCSR寄存器中的SPMEN位被清零(程序存储器操作完成),SPM中断服务将被执⾏(避免轮询占⽤较多机时)。

RWWSB:RWW区忙标志当开始对RWW区进⾏⾃编程(页擦除或页写⼊)操作时,RWWSB位将被硬件置位,RWWSB ⼀旦被置位,对RWW区的读操作将被禁⽌。

在⾃编程操作完成后,向RWWSRE位写⼊1,会将RWWSB位清除。

此外,如果开始⼀个页读取操作,也会将RWWSB位清零。

RWWSRE:读RWW区允许当启动对RWW区⾃我编程(页擦除或页写⼊)操作时,RWWSB位被硬件置1,禁⽌对RWW区的读操作。

在⾃我编程操作完成后(SPMEN=0),同时将RWWSRE位和SPMEN 位置为1,在其后的4个时钟周期内的SPM指令将使RWW区重新开放。

AVR单片机i/o(输入/输出)端口详解通过前面示例的讲解,已基本知道了单片机I/O 端口的用法。

为了更好、更深入地运用好I/O 端口,下面再来详细讨论一下AVR 单片机ATMega16 的端口结构。

输入/输出端口(I/O 端口)是单片机所能依赖进行控制的唯一通道,如果把单片机内核比作人的大脑,那I/O 端口就相当于人的五官和四肢,负责着信息的获取和动作的执行,如果没有I/O 端口单片机本身就变得毫无意义,因此很有必要来详细了解它们的内部结构。

ATMega16 的端口为具有可选上拉电阻的双向I/O 端口,下面是其中某一位I/O 口的内部结构图(来自于Datasheet)。

在上图中,Pxn 就是这一位的输入/输出端口,也就是单片机的某个外部引脚。

它通过PORTxn 寄存器和数据总线(DATA BUS)相连。

前面示例中对PORTxn 的赋值其实就是通过数据总线来写这个寄存器实现的。

在图中还可以看到,在Pxn 和PORTxn 之间实际上还串有一个门控位,如果要让PORTxn 的结果输出至Pxn,那这个门控位必须得打开,而该门控位的受控信号来自于DDxn(DDRx 中的一位)寄存器。

通过数据总线对该寄存器位写1,就可打开门控位,让输出信号直接输出至引脚Pxn。

这也正是为什么单片机引脚要处于输出状态就必须要给DDRx 方向寄存器赋值1 的原因所在。

如果给DDxn 赋值0,则门控位断开,引脚Pxn 不能做为输出,只能做为输入。

但输入信号可以取自两个地方,一个是直接从外部引脚Pxn 来取(图中的下半部分),实际上是把外部引脚的信号锁存到PINxn 寄存器中来读取;另一个则是从输出寄存器PORTxn 来取(图中门控位控制信号为RRx 的地方)。

一般称从外部引脚(PINxn)来取为读引脚,称从寄存器PORTxn 来取为读端口寄存器。

从图中还可以看出,在引脚Pxn 的上方,有一个受控于MOS 管的上拉电阻。

而MOS 管又同时受到PUD 位、DDxn 位和PORTxn 位的共同控制。

第九课A Tmega16(L)的IO端口

本教程节选自周兴华老师《手把手教你学A VR单片机C程序设计》教程,如需转载,请注明出处!读者可通过当当网、淘宝网等网站购买本教程,如需购买配书实验器材,可登陆周兴华单片机培训中心网购部自助购买!

ATmega16(L)单片机有32个通用I/O口,分为PA、PB、PC和PD四组,每组都是8位。

这些I/O 口都可以通过各自的端口寄存器设置成输入和输出(即作为普通端口使用),有些I/O口还具有第二功能(我们在后面使用到这些第二功能时再介绍)。

ATmega16(L)单片机的I/O口在不考虑第二功能时,其基本输入输出功能都是相同的。

如图7-1所示为ATmega16(L)单片机I/O口的结构图。

每个端口对应3个寄存器,即方向寄存器DDRX(X=A、B、C、D)、端口寄存器PORTX(X=A、B、C、D)、输入引脚PINX(X=A、B、C、D),各个端口的工作状况都可以通过对DDRX、PORTX和PINX的操作来完成。

所有的A VR单片机的I/O端口都具有读、写和修改功能。

表7-1列出了A Tmega16(L)的I/O端口的组合控制设置。

ATmega16(L)单片机每一组I/O口的所有管脚都可以单独选择上拉电阻。

引脚缓冲器可以吸收20mA 的电流,能够直接驱动LED显示。

如果设置了弱上拉电阻,当管脚被拉低时,引脚会输出电流。

1.DDRX

DDRX为端口方向寄存器。

当DDRX的某一位置1时相应引脚作为输出使用。

反之,当DDRX的某一位置0时,对应的引脚单片机培训作为输入使用。

例如:

DDRB=0xF0;//此语句将PB端口的PB0~PB3位设为输入,而PB4~PB7位设为输出。

2.PORTX

PORTX为端口数据寄存器。

如果引脚设为输出,则对PORTX进行写操作即改变引脚的输出值。

图7-1A Tmega16(L)的I/O端口

表7-1A Tmega16(L)的I/O端口的组合控制设置

DDRxn(n=0~7)PORTxn(n=0~

7)

I/O 上拉备注

0 0 输入关闭三态(高阻)

0 1 输入打开提供弱上拉,被外部电路拉低时输

出电流

1 0 输出关闭输出0

1 1 输出关闭输出1

例如:

DDRB=0xFF; //此语句将PB端口的PB0~PB7位设为输出。

PORTB=0x55; //PB端口输出01010101。

例如:

DDRB=0x00; //此语句将PB端口的PB0~PB7位设为输入。

PORTB=0xF0; // PB0~PB3位不设上拉,无信号输入时处高阻态。

PB4~PB7位设为上拉,无信号输入时处高电平。

上海周兴华单片机提供单片机培训、FPGA培训、protel培训、PCB设计培训等各种课程,是单片机工程师的要摇篮;

3.PINX

PINX是相应端口的输入引脚地址,如果希望读取引脚的逻辑电平值,一定要读取PINX,而不是PORTX。

注意:PINX是只读的,不能对其赋值。

例如:

DDRB=0x00; //此语句将PB端口的PB0~PB7位设为输入。

PORTB=0xFF; //PB0~PB7位设为上拉,无信号输入时处高电平。

temp=PINB; //将PB口引脚信号读入变量temp中。