基于quartus2的mealy机类型控制adc0809采样的状态机

- 格式:docx

- 大小:28.08 KB

- 文档页数:2

绪论单元测试1.电子设计自动化的英文缩写是EDA。

A:错B:对答案:B2.EDA课程学习要求的五个一是指A:一种技术——EDAB:一种语言——HDLC:一套软件——QuartusIID:一套实验系统E:一个设计目标——数字系统F:一种器件——FPGA/CPLD答案:ABCEF3.学好EDA技术课程的标志是最后可以利用EDA方法设计出一个复杂的数字电子系统。

A:对B:错答案:A4.小组合作学习的目的包括A:相互激励克服困难B:通过交流锻炼表达能力C:分工协作以完成复杂任务D:独立工作展现个人魅力E:互帮互学答案:ABCE5.混合式学习的内涵包括A:独立学习与合作学习的混合B:线上线下学习的混合C:老师讲授与学生自学的混合D:理论学习与实践学习的混合答案:ABCD第一章测试1.基于硬件描述语言的数字系统设计目前不太常用的设计方法是()设计法。

A:自顶向下B:层次化C:自底向上D:顶层设计答案:C2.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程。

下面关于综合的描述错误的是A:综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;B:为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;C:综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是不唯一的。

D:综合是纯软件的转换过程,与器件硬件结构无关。

答案:D3.所列哪个流程是基于EDA软件的正确的FPGA / CPLD设计流程A:原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试B:原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试C:原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试D:原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试答案:C4.IP核在EDA技术和开发中具有十分重要的地位,以版图文件方式提供的IP被称为()。

E D A/S O P C技术实验讲义陕西科技大学电气与信息工程学院目录4第一章 EDA_VHDL实验/设计与电子设计竞赛4 1-1、应用QuartusII完成基本组合电路设计5 1-2. 应用QuartusII完成基本时序电路的设计6 1-3. 设计含异步清0和同步时钟使能的加法计数器7 1-4. 7段数码显示译码器设计8 1-5. 8位数码扫描显示电路设计9 1-6. 数控分频器的设计10 1-7. 32位并进/并出移位寄存器设计10 1-8. 在QuartusII中用原理图输入法设计8位全加器11 1-9. 在QuartusII中用原理图输入法设计较复杂数字系统11 1-10. 用QuartusII设计正弦信号发生器13 1-11. 8位16进制频率计设计16 1-12. 序列检测器设计16 1-13. VHDL状态机A/D采样控制电路实现18 1-14. 数据采集电路和简易存储示波器设计19 1-15. 比较器和D/A器件实现A/D转换功能的电路设计20 1-16 移位相加硬件乘法器设计24 1-17 采用流水线技术设计高速数字相关器24 1-18 线性反馈移位寄存器设计25 1-19 乐曲硬件演奏电路设计28 1-20 乒乓球游戏电路设计32 1-21 循环冗余校验(CRC)模块设计33 1-22. FPGA步进电机细分驱动控制设计(电子设计竞赛赛题)34 1-23. FPGA直流电机PWM控制实验35 1-24. VGA彩条信号显示控制器设计37 1-25. VGA图像显示控制器设计37 1-26. 清华大学学生基于GW48PK2系统VGA图像显示控制器设计示例5则38 1-27. 直接数字式频率合成器(DDS)设计实验(电子设计竞赛赛题)39 1-28. 嵌入式锁相环PLL应用实验41 1-29. 使用嵌入式锁相环的DDS设计实验(200MHz超高速DAC的PLL测试42 1-30. 基于DDS的数字移相信号发生器设计(电子设计竞赛赛题)45 1-31. 采用超高速A/D的存储示波器设计(含PLL,电子设计竞赛赛题)46 1-32. 信号采集与频谱分析电路设计(电子设计竞赛赛题)46 1-33. 等精度数字频率/相位测试仪设计实验(电子设计竞赛赛题)48 1-34. FPGA与单片机联合开发之isp单片机编程方法49 1-35. 测相仪设计(电子设计竞赛赛题)50 1-36. PS/2键盘鼠标控制电子琴模块设计50 1-37. PS/2鼠标与VGA控制显示游戏模块设计50 1-38. FPGA_单片机_PC机双向通信测频模块设计50 1-39. 10路逻辑分析仪设计(电子设计竞赛赛题)51 1-40. IP核:数控振荡器NCO应用设计52 1-41. IP核:FIR数字滤波器应用设计53 1-42. IP核:FFT应用设计53 1-43. IP核:CSC VGA至电视色制互转模块应用设计54 1-44. IP核:嵌入式逻辑分析仪SignalTapII调用55 1-45. USB与FPGA通信实验56第二章 SOPC/EDA设计实验I56 2-1 用逻辑锁定优化技术设计流水线乘法器实验57 2-2 用逻辑锁定优化技术设计16阶数字滤波器实验59 2-3 基于DSP Builder的FIR数字滤波器设计实验60 2-4 基于DSP Builder的IIR数字滤波器设计实验60 2-5 基于DSP Builder的DDS与数字移相信号发生器设计实验62 2-6 m序列伪随机序列发生器设计实验63 2-7 巴克码检出器设计实验65 2-8 RS码编码器设计实验65 2-9 正交幅度调制与解调模型设计实验67 第三章 SOPC/EDA设计实验II67 3-1 基于MATLAB/DSP Builder DSP可控正弦信号发生器设计72 3-2 32位软核嵌入式处理器系统Nios开发实验73 3-3 设计一个简单的SOPC系统74 3-4 简单测控系统串口接收程序设计74 3-5 GSM短信模块程序设计75 3-6 基于SOPC的秒表程序设计77 3-7 Nios Avalon Slave外设(PWM模块)设计78 3-8 Nios Avalon Slave外设(数码管动态扫描显示模块)设计79 3-15 DMA应用和俄罗斯方块游戏设计79第四章 SOPC/EDA设计实验III ( NiosII系统设计 ) 79 4-1、建立NIOSII嵌入式处理器硬件系统87 4-2、NIOSII软件设计与运行流程94 4-3、加入用户自定义组件设计100 4-4、加入用户自定义指令设计103 4-5、FLASH编程下载104 4-6、设计DSP处理器功能系统104 4-7、AM调制电路设计105第五章液晶接口实验105 5-1 GDM12864A液晶显示模块接口开发111 5-2 HS162-4液晶显示模块与单片机的接口114 5-3 G240-128A液晶显示模块的接口115第六章 CPU及其结构组件设计实验115 6-1 复杂指令CPU设计122 6-2 8051/89C51单片机核于FPGA中实现实验124第七章模拟EDA实验124 7-1 模拟EDA实验及其设计软件使用向导(PAC _Designer使用)124 7-2 基于ispPAC80的5阶精密低通滤波器设计126 7-3 基于ispPAC10的直流增益为9的放大器设计129附录:GW48 EDA/SOPC主系统使用说明129 第一节:GW48教学系统原理与使用介绍,132 第二节:实验电路结构图137 第三节:超高速A/D、D/A板GW-ADDA说明138 第四节:步进电机和直流电机使用说明138 第五节:SOPC适配板使用说明139 第六节:GWDVPB电子设计竞赛应用板使用说明141 第七节:GWCK/PK2/PK3系统万能接插口与结构图信号/与芯片引脚对照表第一章EDA_VHDL实验/设计与电子设计竞赛1-1. 应用QuartusII完成基本组合电路设计(1) 实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

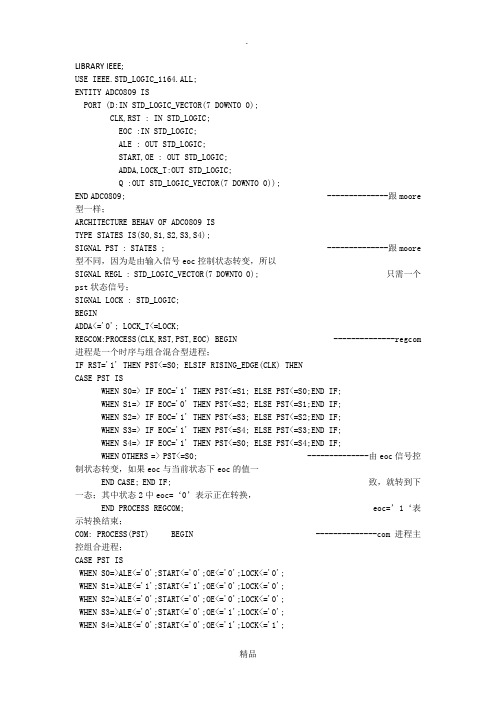

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADC0809 ISPORT (D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);CLK,RST : IN STD_LOGIC;EOC :IN STD_LOGIC;ALE : OUT STD_LOGIC;START,OE : OUT STD_LOGIC;ADDA,LOCK_T:OUT STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ADC0809; --------------跟moore 型一样;ARCHITECTURE BEHAV OF ADC0809 ISTYPE STATES IS(S0,S1,S2,S3,S4);SIGNAL PST : STATES ; --------------跟moore 型不同,因为是由输入信号eoc控制状态转变,所以SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0); 只需一个pst状态信号;SIGNAL LOCK : STD_LOGIC;BEGINADDA<='0'; LOCK_T<=LOCK;REGCOM:PROCESS(CLK,RST,PST,EOC) BEGIN --------------regcom 进程是一个时序与组合混合型进程;IF RST='1' THEN PST<=S0; ELSIF RISING_EDGE(CLK) THENCASE PST ISWHEN S0=> IF EOC='1' THEN PST<=S1; ELSE PST<=S0;END IF;WHEN S1=> IF EOC='0' THEN PST<=S2; ELSE PST<=S1;END IF;WHEN S2=> IF EOC='1' THEN PST<=S3; ELSE PST<=S2;END IF;WHEN S3=> IF EOC='1' THEN PST<=S4; ELSE PST<=S3;END IF;WHEN S4=> IF EOC='1' THEN PST<=S0; ELSE PST<=S4;END IF;WHEN OTHERS => PST<=S0; --------------由eoc信号控制状态转变,如果eoc与当前状态下eoc的值一END CASE; END IF; 致,就转到下一态;其中状态2中eoc=‘0’表示正在转换,END PROCESS REGCOM; eoc=’1‘表示转换结束;COM: PROCESS(PST) BEGIN --------------com进程主控组合进程;CASE PST ISWHEN S0=>ALE<='0';START<='0';OE<='0';LOCK<='0';WHEN S1=>ALE<='1';START<='1';OE<='0';LOCK<='0';WHEN S2=>ALE<='0';START<='0';OE<='0';LOCK<='0';WHEN S3=>ALE<='0';START<='0';OE<='1';LOCK<='0';WHEN S4=>ALE<='0';START<='0';OE<='1';LOCK<='1';WHEN OTHERS=>ALE<='0';START<='0';OE<='0';LOCK<='0';END CASE;END PROCESS COM;LATCH1: PROCESS (LOCK) BEGIN --------------锁存器进程latch1;IF LOCK='1' AND LOCK'EVENT THEN REGL<=D;END IF;END PROCESS LATCH1;Q<=REGL;END BEHAV; --------------编译成功;------------------------------------------------------------------------------------------------------附仿真截图如有侵权请联系告知删除,感谢你们的配合!。

实验三ADC0809模数转换实验一、实验目的1、掌握ADC0809模/数转换芯片与单片机的连接方法及ADC0809的典型应用。

2、掌握用查询方式、中断方式完成模/数转换程序的编写方法。

二、实验说明本实验使用ADC0809模数转换器,ADC0809是8通道8位CMOS逐次逼近式A/D转换芯片,片内有模拟量通道选择开关及相应的通道锁存、译码电路,A/D转换后的数据由三态锁存器输出,由于片内没有时钟需外接时钟信号。

下图为该芯片的引脚图。

各引脚功能如下:IN0~IN7:八路模拟信号输入端。

ADD-A、ADD-B、ADD-C:三位地址码输入端。

八路模拟信号转换选择由这三个端口控制。

CLOCK:外部时钟输入端(小于1MHz)。

D0~D7:数字量输出端。

OE:A/D转换结果输出允许控制端。

当OE为高电平时,允许A/D转换结果从D0~D7端输出。

ALE:地址锁存允许信号输入端。

八路模拟通道地址由A、B、C输入,在ALE信号有效时将该八路地址锁存。

START:启动A/D转换信号输入端。

当START端输入一个正脉冲时,将进行A/D转换。

EOC:A/D转换结束信号输出端。

当A/D转换结束后,EOC输出高电平。

Vref(+)、Vref(-):正负基准电压输入端。

基准正电压的典型值为+5V。

VCC和GND:芯片的电源端和地端。

三、实验步骤1、单片机最小应用系统1的P0口接A/D转换的D0~D7口,单片机最小应用系统1的Q0~Q7口接0809的A0~A7口,单片机最小应用系统1的WR、RD、P2.0、ALE、INT1分别接A/D转换的WR、RD、P2.0、CLOCK、INT1,A/D转换的IN接入+5V,单片机最小应用系统1的RXD、TXD连接到串行静态显示实验模块的DIN、CLK。

2、基于KEIL建立A/D转换程序。

要求将采集到的电压等间隔分为0~9共10级,并用一位共阴级数码管显示出来。

四、流程图及源程序1.流程图如图2所示。

adc0809的工作原理

ADC0809是一种8位串行模数转换器(Analog-to-Digital Converter,简称ADC),其工作原理如下:

1. 输出控制信号:当待转换的模拟信号准备好后,控制信号线将置为高电平,通知ADC开始转换过程。

2. 选择输入通道:通过输入通道选择信号来选择要进行转换的模拟信号源。

ADC0809有8个输入通道,因此需要使用3个输入引脚来选择通道。

3. 启动时钟信号:通过发送时钟信号来控制转换过程。

ADC0809需要一个时钟源来同步转换过程。

时钟信号的频率决定了转换速度。

4. 采样保持电路:在转换期间,输入信号将被采样并保持在一个样本保持电容中。

这个采样保持电路保证了转换期间输入信号的稳定性。

5. 双斜率积分器:ADC0809采用了双斜率积分器技术来进行模拟信号的转换。

在转换开始后,ADC开始对采样保持电容的电压进行积分,直到电压上升到参考电压。

6. 输出数据:一旦积分电压达到参考电压,ADC会将其状态固定,并将其转换为二进制数字输出。

输出数据以8位二进制形式呈现。

7. 转换结束信号:当转换完成后,ADC会通过标志信号线发出转换完成的信号。

这个信号可以被连接到微控制器或其他数字设备,以通知它们可以读取新的转换结果了。

通过以上步骤,ADC0809可以将模拟信号转换为数字信号,实现模拟到数字的转换功能。

使用ADC0809的A/D转换实验一、实验目的加深理解逐次逼近法模数转换器的特征和工作原理,掌握ADC0809的接口方法以及A/D 输入程序的设计和调试方法。

二、预备知识逐次逼近法A/D也称逐次比较法A/D。

它由结果寄存器、D/A、比较器和置位控制逻辑等部件组成,如图6-1所示。

图6-1 逐次逼近法三、实验内容1、实验原理本实验采用 ADC0809 做 A/D 转换实验。

ADC0809 是一种8路模拟输入、8位数字输出的逐次逼近法A/D器件,转换时间约100us,转换精度为±1/512,适用于多路数据采集系统。

ADC0809片内有三态输出的数据锁存器,故可以与8088微机总线直接接口。

图中ADC0809的CLK信号接CLK=2.385MHZ,基准电压Vref(+)接Vcc。

一般在实际应用系统中应该接精确+5V,以提高转换精度,ADC0809片选信号0809CS和/IOW、/IOR经逻辑组合后,去控制ADC0809的ALE、START、ENABLE信号。

ADC0809的转换结束信号EOC未接,如果以中断方式实现数据采集,需将EOC信号线接至中断控制器8259A的中断源输入通道。

本实验以延时方式等待A/D转换结束,ADC0809的通道号选择线ADD-A、ADD-B、ADD-C 接系统数据线的低3位,因此ADC0809的8个通道值地址分别为00H、01H、02H、03H、04H、05H 、06H、07H。

启动本A/D转换只需如下三条命令:MOV DX,ADPORT ;ADPORT为ADC0809端口地址。

MOV AL,DATA ;DATA为通道值。

MOV DX, AL ;通道值送端口。

读取A/D转换结果用下面二条指令:MOV DX,ADPORTIN AL,DX2、实验线路的连接在原理图6-2中,粗黑线是学生需要连接的线,粗黑线两端是需连接的信号名称。

1)IN0插孔连W1的输出V1插孔。

2)0809CS连译码输出060H~06FH插孔。

由于数字电子技术的迅速发展,尤其是计算机在自动控制、自动检测以及许多其他领域中的广泛应用,数字电路处理模拟信号的情况也越来越普遍。

数字电路处理模拟信号就是把模拟信号转换成相应的数字信号输出。

我们把这种从模拟信号到数字信号的转换称为模-数转换,或简称为A/D(Analog to Digital)转换。

同时把实现A/D转换的电路成为A/D转换器,简写为ADC(Analog-Digital Converter)。

在A/D转换器中因为输入的模拟信号在时间上是连续的,而输出的数字信号是离散的,所以转换只能在一系列选定的瞬间对输入的模拟信号取样,然后再把这些取样值转换成输出的数字量。

因此,A/D转换的过程是首先对输入的模拟电压信号取样,取样结束后进入保持时间,在这段时间内将取样的电压量化为数字量,并按一定的编码形式给出转换结果。

然后,再开始下一次取样。

1.2取样定理为了能正确无误地用取样信号Vs表示模拟信号Vi,取样信号必须有足够高的频率。

可以证明,为了保证能从取样信号将原来的被取样信号恢复,必须满足ƒs≥2ƒi(max)上式就是取样定理,其中,ƒs为取样频率,ƒi(max)为输入模拟信号Vi的最高频率分量的频率。

在满足上式的条件下,可以用低通滤波器将Vs还原为Vi。

这个低通滤波器的电压传输系数在低于ƒi(max)的范围内应保持不变,而在ƒs-ƒi(max)以前应迅速下降为0,因此,A/D转换器工作时的取样频率必须高于最大频率,取样频率提高也就意味着留给每次转换的时间相应的缩短,这就要求转换电路必须具备更快的工作速度。

因此,为了满足要求,通常取ƒs=(3-5)ƒi(max)。

1.3取样-保持电路取样-保持电路的基本形式如图所示,所谓的保持,就是将采样的模拟量值保持下来。

图中,当s(t)=1时,T导通,Vi向Cb充电,V o和Vc跟踪Vi变化,既对Vi采样。

当s(t)=0时,T截止,V o将保持前一瞬间采样的数值不变。

A D C0808功能及简介11.2.4 典型的集成ADC 芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC 芯片。

仅美国AD 公司的ADC 产品就有几十个系列、近百种型号之多。

从性能上讲,它们有的精度高、速度快,有的则价格低廉。

从功能上讲,有的不仅具有A/D 转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC 芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。

选用ADC 芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC 芯片允许输出线与微机系统的数据总线直接相连,并在转换结束后利用读数信号RD 选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC 芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O 接口与MPU 交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。

对脉冲启动转换的ADC 芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

一般能和MPU 配套使用的芯片,MPU 的I/O 写脉冲都能满足ADC 芯片对启动脉冲的要求。

对电平启动转换的ADC 芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。

为此,必须用D 触发器或可编程并行I/O 接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY ADC0809 IS

PORT (D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CLK,RST : IN STD_LOGIC;

EOC :IN STD_LOGIC;

ALE : OUT STD_LOGIC;

START,OE : OUT STD_LOGIC;

ADDA,LOCK_T:OUT STD_LOGIC;

Q :OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ADC0809; --------------跟moore型一样;

ARCHITECTURE BEHAV OF ADC0809 IS

TYPE STATES IS(S0,S1,S2,S3,S4);

SIGNAL PST : STATES ; --------------跟moore型不同,因为是由输入信号eoc控制状态转变,所以

SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0); 只需一个pst状态信号;

SIGNAL LOCK : STD_LOGIC;

BEGIN

ADDA<='0'; LOCK_T<=LOCK;

REGCOM:PROCESS(CLK,RST,PST,EOC) BEGIN --------------regcom进程是一个时序与组合混合型进程;

IF RST='1' THEN PST<=S0; ELSIF RISING_EDGE(CLK) THEN

CASE PST IS

WHEN S0=> IF EOC='1' THEN PST<=S1; ELSE PST<=S0;END IF;

WHEN S1=> IF EOC='0' THEN PST<=S2; ELSE PST<=S1;END IF;

WHEN S2=> IF EOC='1' THEN PST<=S3; ELSE PST<=S2;END IF;

WHEN S3=> IF EOC='1' THEN PST<=S4; ELSE PST<=S3;END IF;

WHEN S4=> IF EOC='1' THEN PST<=S0; ELSE PST<=S4;END IF;

WHEN OTHERS => PST<=S0; --------------由eoc信号控制状态转变,如果eoc与当前状态下eoc的值一

END CASE; END IF; 致,就转到下一态;其中状态2中eoc=‘0’表示正在转换,

END PROCESS REGCOM; eoc=’1‘表示转换结束;

COM: PROCESS(PST) BEGIN --------------com进程主控组合进程;

CASE PST IS

WHEN S0=>ALE<='0';START<='0';OE<='0';LOCK<='0';

WHEN S1=>ALE<='1';START<='1';OE<='0';LOCK<='0';

WHEN S2=>ALE<='0';START<='0';OE<='0';LOCK<='0';

WHEN S3=>ALE<='0';START<='0';OE<='1';LOCK<='0';

WHEN S4=>ALE<='0';START<='0';OE<='1';LOCK<='1';

WHEN OTHERS=>ALE<='0';START<='0';OE<='0';LOCK<='0';

END CASE;

END PROCESS COM;

LATCH1: PROCESS (LOCK) BEGIN --------------锁存器进程latch1;

IF LOCK='1' AND LOCK'EVENT THEN REGL<=D;END IF;

END PROCESS LATCH1;

Q<=REGL;

END BEHAV; --------------编译成功;

------------------------------------------------------------------------------------------------------附仿真截图。