状态机设计总结

- 格式:doc

- 大小:65.50 KB

- 文档页数:11

状态机学习报告1.状态机概念状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法,是由寄存器组和组合逻辑构成的硬件时序电路。

所有具有逻辑顺序和时序规律的事情都适合用状态机来描述。

状态机有三要素:状态(状态变量),在逻辑设计中,使用状态划分逻辑顺序时序规律。

输出,在某一个状态时特定发生的时间。

输入,状态机进入每个状态的条件。

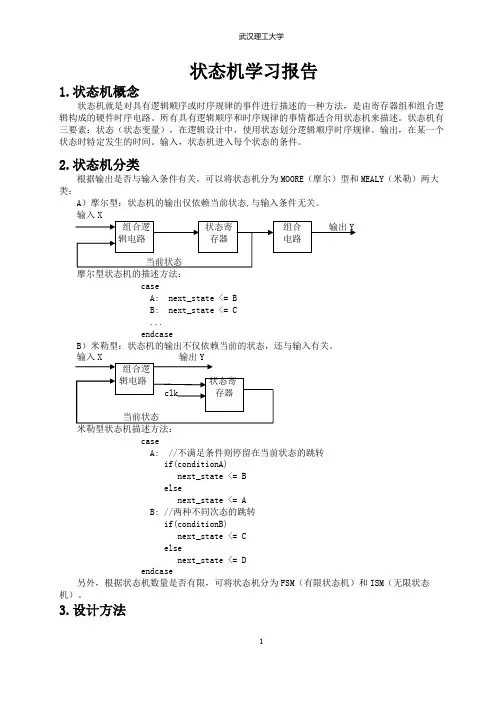

2.状态机分类根据输出是否与输入条件有关,可以将状态机分为MOORE(摩尔)型和MEALY(米勒)两大类:A)摩尔型:状态机的输出仅依赖当前状态,与输入条件无关。

摩尔型状态机的描述方法:caseA: next_state <= BB: next_state <= C...endcaseB)米勒型:状态机的输出不仅依赖当前的状态,还与输入有关。

caseA: //不满足条件则停留在当前状态的跳转if(conditionA)next_state <= Belsenext_state <= AB: //两种不同次态的跳转if(conditionB)next_state <= Celsenext_state <= Dendcase另外,根据状态机数量是否有限,可将状态机分为FSM(有限状态机)和ISM(无限状态机)。

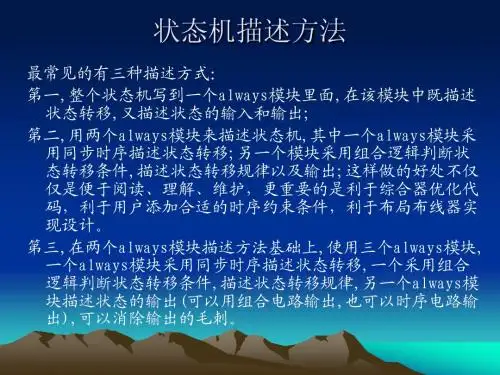

3.设计方法状态机的描述方式有:状态转移图、状态转移列表和HDL语言描述。

状态转移图经常在设计规划阶段定义逻辑功能时使用,也可以在分析已有源代码中的状态机时使用,这种图形化的描述方式有助于理解设计意图。

状态转移列表是用列表的方式描述状态机,是数字逻辑电路常用的设计方法之一,经常被用于状态化简,对于可编程逻辑设计而言,由于可用逻辑资源比较丰富,而且状态编码要考虑设计的稳定性、安全性等因素,所以并不经常使用状态转移列表优化状态。

使用HDL语言描述状态机应具有一定的灵活性,通过使用一些规范的描述方法,可以使HDL语言描述状态机更安全、更稳定、更高效、更易于维护。

实验一 Xilinx软件及状态机设计一实验目的:学习FPGA设计软件, 掌握软件流程, 掌握状态机编程。

二实验内容:设计一个状态机三实验说明:状态机设计是数字电路中使用非常广泛和方便的时序设计工具。

由于硬件是并行的触发, 相对软件是串行执行, 那么让硬件电路按照节拍执行串行操作指令就成为一个问题, 这就是状态机的主要功能。

相应的, 软件指令中的几十条简单顺序执行代码可能需要硬件的几十上百个触发器去实现其功能。

所以, 软件与硬件的设计思路有相当大的区别。

当然, 随着FPGA规模的不断扩大, 这些问题也越来越容易解决了。

我们可以用软件的思路去描述自己的设计, 可能最终实现的电路是几十万门级的器件, 但是你只要花费几美元就能买到。

状态机是数字电路的基础, 因此, VHDL的学习也从这个实验开始。

四实验过程:1.在进行实验之前, 我先自学了VHDL语言。

2.熟悉Xilinx软件环境。

3.通过仿真, 读懂了states这段代码所实现的功能及其出现的问题。

五思考题:1.通过仿真, 这段代码实现相应功能时出了什么问题?请修正代码。

答:这段程序完成的是对红绿灯的控制功能。

通过仿真发现所有的灯都比预期的多亮了2秒, 比如东西方向绿灯亮62秒(应该是60秒), 黄灯是5秒(应该是3秒)。

出现此问题的原因是没有考虑到硬件的延时问题。

所以只要把程序中的59改为57, 39改为37, 3改为1, 再进行仿真, 结果就正确了。

2.状态机输出分成同步输出和异步输出, 状态机异步输出直接用状态机的某个状态进行组合逻辑运算来得到一个输出, 同步输出是在该状态的时钟上跳沿控制输出变化。

请问同步输出和异步输出利弊各在哪里?答: 同步输出的优点是: 时钟脉冲的间距解决了组合逻辑电路中的延时和竞争问题。

只要时钟脉冲的宽度合适, 输出就不会存在竞争与现象。

缺点是: 外部输入信号的变化应满足触发器正常工作所需的建立和保持时间。

因为上述特点使得同步时序输出的工作速度的提高受到限制, 且对时钟脉冲到达个触发器的时间及外部信号的变化有较严格的要求。

简述状态机组合逻辑设计原理-回复状态机组合逻辑设计原理是一种常用的数字电路设计方法,通过将多个状态机模块进行组合和联结,实现复杂数字系统的设计。

该方法在计算机硬件、通信系统、嵌入式系统等领域得到广泛应用。

本文将详细介绍状态机组合逻辑设计原理的基本概念和步骤,以帮助读者深入了解和掌握该设计方法。

首先,让我们从状态机的基本概念开始。

状态机是一种数学模型,用于描述和控制系统在不同状态下的行为。

在数字电路设计中,状态机通常包括输入、输出和状态寄存器三个主要部分。

输入是外界输入信号,输出是系统生成的输出信号,状态寄存器用于存储当前状态。

状态机通过接收输入信号、执行状态转移和输出控制等操作,完成对系统行为的控制。

在状态机组合逻辑设计中,我们会将多个状态机模块进行组合和联结,以实现复杂系统的设计。

这种组合和联结的方式可以通过层次化、串行和并行等方式进行,具体方式取决于设计需求和电路复杂度。

下面,让我们一步一步地回答中括号内的内容,详细介绍状态机组合逻辑设计原理。

首先,我们需要确定复杂系统的功能需求和设计规格。

这一步骤非常重要,它决定了我们后续的设计方案。

在这一步骤中,我们需要明确系统的输入输出信号,各个子系统的功能和相互之间的关系等。

通过对需求和规格的分析,我们可以确定系统的功能分块,以及各个分块之间的关系。

接下来,我们需要将功能需求和规格转化为状态机模型。

这一步骤主要包括状态的确定和状态转移的定义。

首先,我们需要根据每个子系统的功能,确定状态机的各个状态。

状态的确定应尽量满足功能需求和规格,同时尽可能简化和精简状态机模型。

其次,我们需要定义状态转移条件和状态转移动作。

状态转移条件是指状态之间的转移触发条件,状态转移动作是指在状态转移过程中需要执行的操作。

状态转移条件和状态转移动作的定义应与功能需求和规格一致,并尽可能明确和简洁。

然后,我们需要设计状态机的控制逻辑。

状态机的控制逻辑用于根据输入信号、当前状态和状态转移条件,决定下一个状态和输出信号。

状态机在ic设计中的作用和意义摘要:1.引言2.状态机的基本概念和原理3.状态机在IC 设计中的应用4.状态机在IC 设计中的重要性5.总结正文:【引言】在现代电子技术中,集成电路(IC)的设计和应用已经越来越广泛。

状态机作为控制电子设备状态的核心部分,对于IC 设计有着重要的作用和意义。

本文将从状态机的基本概念和原理入手,分析其在IC 设计中的应用和重要性。

【状态机的基本概念和原理】状态机,又称有限状态自动机(FSM),是一种用来表示和控制设备状态的数学模型。

它由一组状态、一组事件和一组动作构成。

状态机根据输入事件,从一个状态转移到另一个状态,同时执行相应的动作。

这种状态转移和动作执行的过程,可以用来描述和控制设备的运行状态。

【状态机在IC 设计中的应用】在IC 设计中,状态机的应用非常广泛。

它被用来控制各种设备的状态,如处理器、存储器、传感器等。

例如,在处理器设计中,状态机被用来控制指令的执行顺序和操作,确保处理器能够正确地处理各种指令。

在存储器设计中,状态机被用来控制存储器的读写操作,确保数据能够正确地被读取和写入。

在传感器设计中,状态机被用来控制传感器的工作状态,确保传感器能够准确地检测到各种物理量。

【状态机在IC 设计中的重要性】状态机在IC 设计中的重要性不言而喻。

首先,状态机能够精确地控制设备的状态,确保设备能够正确地运行。

其次,状态机能够简化设备的控制逻辑,提高设备的运行效率。

最后,状态机能够提高设备的可靠性,延长设备的使用寿命。

【总结】总的来说,状态机在IC 设计中起着重要的作用,不仅能够精确地控制设备的状态,提高设备的运行效率,还能够提高设备的可靠性,延长设备的使用寿命。

编程思想总结状态机状态机(State Machine)是一种常见的编程思想,它将程序的运行过程分解为一系列离散的状态,并定义了状态之间的转换条件。

状态机的核心思想是在不同的状态下执行不同的操作,根据输入或者事件将程序的状态从一个状态转换为另一个状态。

状态机通常包含以下几个要素:1. 状态(State):程序运行时所处的特定状态。

每个状态都有固定的行为和特性。

2. 事件(Event):触发状态转换的输入或者条件。

当某个事件发生时,状态机将根据当前状态以及事件的类型执行相应的动作。

3. 转换条件(Transition):决定状态机从一个状态转换到另一个状态的条件。

当满足转换条件时,状态机将执行相应的状态转换操作。

4. 动作(Action):状态转换时执行的操作或者行为。

动作可以是一段代码逻辑,也可以是调用其他函数或者方法。

根据状态机的特点和应用场景,可以将状态机分为以下几种类型:1. 简单状态机(Simple State Machine):也称为有限状态机,只有有限个状态和转换条件。

每次只在一个状态之间转换,不涉及并发和并行操作。

2. 层次状态机(Hierarchical State Machine):状态之间可以存在层次关系,一个状态可以包含多个子状态。

状态之间的转换可能涉及到多层次的状态切换。

3. 并发状态机(Concurrent State Machine):多个状态之间可以并行执行,相互之间没有依赖关系。

每个状态可能独立地进行状态转换。

状态机的优点有:1. 结构清晰:将复杂的程序逻辑分解成多个离散的状态,易于理解和维护。

2. 灵活性强:可以根据实际需求定义不同的状态和状态转换条件,适应不同的应用场景。

3. 可扩展性好:可以随时添加新的状态或者修改已有的状态转换条件,不影响其他部分的代码。

4. 并发执行:并发状态机可以实现多个状态的并行执行,提高程序的处理效率和响应速度。

状态机的缺点有:1. 复杂度高:状态机需要定义多个状态和状态转换条件,可能会增加代码的复杂度和工作量。

数字电路设计中的时序逻辑与状态机设计时序逻辑与状态机设计是数字电路设计中的重要概念。

在数字电路中,时序逻辑指的是电路的输出是根据输入信号的时序关系而变化的,而状态机则是通过状态转换来实现特定功能的电路。

本文将详细介绍时序逻辑与状态机设计的原理、方法和实践经验。

一、时序逻辑设计的基础原理时序逻辑设计是指在数字电路中,通过引入时钟信号来控制电路的行为。

时钟信号可以被理解为一个周期性的信号,它将整个电路的工作分为不同的阶段。

在每个时钟周期内,时序逻辑根据输入信号的状态进行计算,并且在下一个时钟边沿产生输出信号。

时序逻辑设计的基础原理包括以下几个关键要点:1. 时钟信号:时钟信号的频率决定了电路的最大工作速度,而时钟边沿决定了电路的状态更新时机。

2. 触发器:触发器是实现时序逻辑的基本元件,它可以存储和传递信息,并在时钟边沿触发状态更新。

常见的触发器有D触发器、JK触发器和T触发器等。

3. 时序逻辑电路的设计方法:时序逻辑电路的设计方法包括状态转移图、状态转移方程和状态表等。

这些设计方法可以帮助设计师理清输入、输出和状态之间的关系,便于电路功能的实现。

二、状态机设计的基本概念与方法状态机是一种抽象的数学模型,常用于描述具有确定性行为的系统。

在数字电路设计中,状态机通常用于实现序列逻辑电路的控制部分,如计数器、序列检测器等。

状态机设计的基本概念与方法包括以下几个关键要点:1. 状态:状态是指系统在某个时刻的特定条件。

在状态机设计中,状态通常用离散的值来表示,比如二进制编码。

2. 状态转换:状态转换表示系统从一个状态切换到另一个状态的过程。

状态转换可以通过组合逻辑电路来实现,也可以通过时序逻辑电路实现。

3. 输出函数:输出函数定义了每个状态下的输出值。

它可以通过组合逻辑电路来实现,也可以通过状态寄存器的输出来实现。

4. 状态机设计流程:状态机设计的一般流程包括确定系统的输入、输出和状态集合,绘制状态转移图,推导状态转移方程,实现状态转移电路等。

第五讲状态机设计及其指导原则1/ 38第五讲状态机设计及其指导原则1/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则1 状态机是一种设计思想方法2状态机结构3状态机设计的其他技巧4状态机设计步骤第五讲状态机设计及其指导原则2/ 38第五讲状态机设计及其指导原则2/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学z 状态机是一种设计思想方法第五讲状态机设计及其指导原则3/ 38第五讲状态机设计及其指导原则3/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学原语描述module noconditional (clk,nrst,state,event);input clk,nrst input state;output event;reg event;reg [2:0] CS; //CurrentState reg[2:0] NS; //NextStateparameter [2:0] //one hot with zero idleidle = 3’b000,dorm = 3'b001,diningroom = 3'b010,classroom = 3'b100;第五讲状态机设计及其指导原则4/ 38第五讲状态机设计及其指导原则4/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学//sequential state transitionalways @ (posedge clk or negedge nrst)if (!nrst) CS <= idle; else CS <= NS; //combinational condition judgment always @ (nrst or CS)begincase (CS)idle:idle_task;NS = dorm;dorm:dorm_task;NS = diningroom;diningroom:diningroom_task;NS = classroom;classroom:classroom_task;NS = dorm;default:idle_task;NS = dorm;endcase end endmodule第五讲状态机设计及其指导原则5/ 38第五讲状态机设计及其指导原则5/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则6/ 38第五讲状态机设计及其指导原则6/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学 状态机的本质--对具有逻辑顺序或时序规律事件的一种描述方法 状态机的两个应用思路:-从状态变量入手-明确电路的输出的关系第五讲状态机设计及其指导原则7/ 38第五讲状态机设计及其指导原则7/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学对于逻辑电路而言,小到一个简单的时序逻辑,大到复杂的微处理器,都适合用状态机方法进行描述。

java statemachine设计原理状态机(StateMachine)是一种基本的设计模式,用于模拟对象的行为,包括描述该对象的所有可能状态,以及状态之间的转移条件和行为响应。

它通过定义状态和状态之间的转换来描述一个系统的行为,并通过触发事件或条件来改变状态。

在Java中,可以使用不同的方式来实现状态机,包括使用面向对象的方法、使用条件语句等。

下面将详细介绍Java状态机的设计原理和实现方式。

一、状态机设计原理1.状态(State):状态是状态机的基本元素,它定义了一个对象可能存在的所有状态。

在Java中,可以通过定义一个状态接口或者一个状态类来表示状态,并在其中定义该状态下的行为。

2.事件(Event):事件是触发状态转换的条件或者动作,它可以是内部事件(例如定时器事件、自定义事件)或者外部事件(例如用户输入)。

3.转换(Transition):转换表示状态之间的转移关系,它定义了从一个状态到另一个状态的条件和行为。

在Java中,可以使用条件语句、状态模式等方式来实现转换。

4.动作(Action):动作是在状态转换过程中执行的一系列操作,它可以包括状态切换、数据处理等。

在Java中,可以通过定义一个动作接口或者一个动作类来表示动作,并在其中实现具体的操作逻辑。

5.触发器(Trigger):触发器是用于触发状态转换的条件或者事件,它可以是一个方法调用、一个信号、一个计时器等。

在Java中,可以使用回调机制、观察者模式等方式来实现触发器。

二、状态机的实现方式在Java中,可以使用面向对象的方法来实现状态机,包括使用接口和类的方式。

下面将分别介绍这两种实现方式。

1.使用接口实现状态机使用接口来实现状态机时,可以定义一个状态接口,其中包含该状态下的行为方法,并在每个状态类中实现对应的行为逻辑。

同时,在状态类中也可以定义一个转换方法,用于根据条件或事件触发状态转换。

```java//定义状态接口public interface State {void behavior();void transition();}//实现状态类public class StateA implements State {public void behavior() {//实现状态A的行为逻辑System.out.println("State A behavior");}public void transition() {//根据条件或事件触发状态转换if (condition) {context.setState(new StateB());}}}public class StateB implements State { public void behavior() {//实现状态B的行为逻辑System.out.println("State B behavior"); }public void transition() {//根据条件或事件触发状态转换if (condition) {context.setState(new StateA());}}}//定义上下文类public class Context {private State state;public void setState(State state) { this.state = state;}public void behavior() {state.behavior();}public void transition() {state.transition();}}```使用接口实现状态机的优点是灵活性高,可以通过定义不同的状态类来扩展状态机的功能。

《FPGA系统设计》实验报告》有限状态机的设计一、设计任务a)了解有限状态机的概念;b)掌握Moore型有限状态机的特点和其VHDL语言的描述方法;c)掌握Mealy型有限状态机的特点和其VHDL语言的描述方法。

二、设计过程实验原理在数字电路系统中,有限状态机是一种重要的时序逻辑电路模块。

它对数字系统的设计具有十分重要的作用。

例如:全自动洗衣机,浸泡、洗涤、排水、脱水,流程状态无需手动操作,只要条件满足就自动进入下一工作个状态,并且工作流程可以灵活设定。

这种控制功能完全可用有限状态机来实现。

有限状态机( Finite State Machine, FSM)也是一种时序逻辑电路。

状态机从输出方式出发,可以分为Moore型和Mealy型;从状态机结构出发,可以分为单进程状态机和多进程状态机。

我们知道,任何数字系统都可以分为相互作用的控制单元(control unit)和数据通道(data path)两部分。

数据通道通常由组合逻辑构成,而控制单元通常由时序逻辑构成,任何时序电路都可以表示为有限状态机(Finite State Machine,FSM)。

在基本时序逻辑电路建模的基础上,本实验主要介绍有限状态机实现复杂时序逻辑电路的设计。

数字系统控制部分的每一个部分都可以看作一种状态,与每一控制相关的转换条件指定了状态的下一个状态和输出。

根据有限状态机的输出与当前状态和当前输入的关系,可以将有限状态机分成Moore 型有限状态机和Mealy型有限状态机两种。

从现实的角度,这两种状态机都可以实现同样的功能,但是它们的时序不同,选择使用哪种有限状态机要根据实际情况进行具体分析。

1.单进程Moore型有限状态机程序码图6.1 引脚分配图图6.2 Moore型实验箱现象2.该状态机时一个2进程Mealy型状态机,进程COMREG是时序与组合混合型进程;进程COM1负责根据状态和输入信号给出不同的输出信号。

图6.3 引脚分配图图6.4 Mealy型实验箱现象3.该状态机属于Moore型状态机,由两个主控进程构成,其中进程REG 是主控时序进程,COM是主控组合进程。

数字电路与逻辑设计实验总结数字电路与逻辑设计实验总结数字电路与逻辑设计是电子信息工程专业中一门非常重要的基础课程。

在这门课程的实验中,我们主要学习了数字电路的基本知识、数字电路的组成和设计方法以及数字电路的应用。

以下是我的实验总结:1. 实验内容本门课程共有8个实验,其中包括了数字逻辑电路的基础实验、计数器的设计、状态机的设计等内容。

通过这些实验,我们学习到了数字电路设计的基本流程和方法,并了解了数字电路的各种应用场景。

2. 实验过程在实验过程中,我们需要根据实验手册中的要求进行组装、连接和测试。

在实验进行过程中,经常需要仔细地查看原理图和数据手册,来了解芯片的使用方法和注意事项。

在实验完成后,需要认真地分析实验结果,找出问题并进行修改。

3. 实验收获通过本门课程的学习和实验,我收获了很多。

首先,我掌握了数字电路的基本知识和设计方法,了解了数字电路在各个领域的应用。

其次,我从实验中学会了如何查看数据手册和原理图,并学会了对数字电路进行分析和修复。

此外,实验还锻炼了我的动手实践能力和团队协作能力。

4. 实验体会在实验过程中,我深刻体会到了数字电路的复杂性和精密性。

数字电路设计需要进行精细的计算和严格的测试,一旦出现问题,修复起来也十分复杂。

因此,在数字电路设计时,一定要认真细致地进行计算和测试,并保证设计的可靠性和稳定性。

总之,通过数字电路与逻辑设计的实验,我对数字电路的认识更加深入,并掌握了数字电路的设计方法和调试技巧。

这对我的电子信息工程专业学习和未来的工作都具有非常重要的意义。

状态机设计实验报告小结引言状态机是一种用于描述对象行为的工具,它在开发软件系统时具有重要的作用。

本次实验主要目的是通过学习状态机的原理和设计方法,利用状态机理论来设计和实现一个简单的系统。

本文将对实验的整体过程和结果进行总结和分析。

实验过程设计目标本次实验的设计目标是实现一个简单的自动售货机系统。

系统具有四个状态:待命状态、支付状态、出货状态和故障状态。

当用户插入钱币时,系统从待命状态转换到支付状态;当用户选择商品并确认支付时,系统从支付状态转换到出货状态;当出货完成后,系统从出货状态转换为待命状态;当系统出现故障时,系统进入故障状态。

状态图设计根据设计目标,我们绘制了自动售货机系统的状态图。

状态图清晰地显示了各个状态之间的转换关系和条件。

在状态图的设计中,我们使用了合适的符号和标注,让状态机的含义更加明确。

状态图的设计是状态机实现的基础,合理的状态图可以减少后续的修改和调试工作。

状态机实现在实验中,我们选择使用Python语言来实现状态机。

Python提供了强大的面向对象编程能力,可以很方便地实现状态机的各个组件。

我们编写了一个`StateMachine`类来表示状态机,该类具有状态转换和条件判断的功能。

通过维护状态和事件的字典,我们可以方便地进行状态转换和条件判断。

系统测试在状态机实现完成之后,我们对系统进行了一系列的测试。

测试的目的是验证系统在各个状态之间能够正确地进行转换,并且根据条件触发相应的操作。

测试包括了用户插入钱币、选择商品、确认支付、出货等动作,并检查系统是否输出了正确的结果。

通过测试,我们发现系统在各个状态下表现良好,能够正确地处理各种输入情况,并产生正确的输出结果。

实验结果经过实验,我们成功地设计和实现了一个简单的自动售货机系统。

系统能够正确地进行状态转换,并在不同的状态下展示不同的行为。

通过状态机的设计,我们清晰地定义了系统的各个状态和转换条件,提高了程序的可读性和可维护性。

状态机设计简介状态机的设计被广泛地用于时序控制逻辑中,它是许多数字系统的核心。

状态机可以应付众多应用场合的需求,覆盖宽范围的性能和复杂度;例如微处理器与VLSI外围接口的低级别控制,常规微处理器中的总线裁决和时序产生,定制的位片微处理器,数据加密和解密,传输协议等。

通常在设计周期中,控制逻辑的细节安排在最后处理,因为系统需求的改变和特征的增强会对其造成影响。

对于控制逻辑设计,可编程逻辑是一个很宽松的解决方案,因为它允许简单的修改而不必扰乱PCB板布局。

其灵活性提供了在不影响市场化时间的前提下,允许设计改动的机会。

大多数带寄存器的PAL器件应用都是需要使用状态机设计技术的时序控制逻辑。

随着技术的发展,新的高速、高性能的器件不断出现,它们简化了状态机设计的任务。

对于状态机设计,宽范围的不同功能与性能的解决方案是可行的。

在本次讨论中,我们将检验状态机执行的功能,它们在多种器件中的实现,以及它们的选择。

什么是状态机?状态机是一个以有序的方式,遍历预定的状态序列的数字设备。

状态是在电路的不同部分,测量到的一组数值。

一个简单状态机可以由以下几部分构成:基于PAL器件的组合逻辑,输出寄存器和状态寄存器。

这样一个序列发生器中的状态由状态寄存器和/或输出寄存器中所存储的值来决定。

状态机的通用形式可以用图1所示的设备来描述。

除了这一设备的输入和输出,状态机还有两个必需的组成元件:组合逻辑和存储器(寄存器)。

这类似于前面所讨论的带寄存器的记数器设计,它们本质上就是简单的状态机。

存储器用来存储状态机的状态,组合逻辑可以看成两个截然不同的功能模块:下一状态解码器和输出解码器(图2)。

当输出解码器产生实际的输出时,下一状态解码器决定状态机的下一状态。

尽管它们执行截然不同的两个功能,但是它们通常被组合成如图1所示的组合逻辑阵列。

状态机的基本操作有两部分:<!--[if !supportLists]-->1、状态机遍历状态序列,下一状态解码器基于当前状态和输入条件来决定下一状态。

<!--[endif]--><!--[if !supportLists]-->2、状态机提供基于状态转换的输出信号序列,输出解码器基于当前状态和当前输入条件来决定输出。

<!--[endif]-->用输入信号决定下一状态也被称为分支。

除了分支,复杂序列发生器提供循环的能力和子程序。

从一个状态到另一个状态的转换被称为控制定序,决定下一状态所需的逻辑被称为转换函数(图2)。

在决定输出的进程中,输入信号的使用决定了状态机的类型。

有两种被广泛知道的状态机,Mealy和Moore(图3)。

Moore型状态机的输出只是当前状态的函数。

而对于更为普遍的Mealy型状态机,输出是状态和输入信号的函数。

所需的逻辑被称为输出函数。

无论哪种类型,控制定序都取决于状态和输入信号。

多数实际的状态机是依赖于时钟信号来触发状态转换的同步时序电路。

单个时钟被连接到所有状态和输出边沿触发器,允许在时钟上升沿处发生状态转换。

异步状态机也是可能的,它利用组合逻辑的传输延迟来完成状态机的存储功能。

这样的状态机容易出故障,难以设计,很少被使用,在我们的讨论中,只着重于时序状态机。

<!--[if !supportEmptyParas]-->图1 简单状态机的功能块框图图2 状态机,带独立的输出和下一状态解码器图3 两种标准状态机的模型状态机应用状态机适用于很多系统控制应用领域。

下面举个应用的例子,讨论一下状态机是怎样被应用的。

在数字信号处理(DSP)的应用中,状态机不需要复杂微处理器的处理就可以提供高速高效的函数。

对于简单的算法,例如快速傅立叶变换的算法,状态机可以控制相乘和相加的向量组。

对于复杂的DSP操作,可编程DSP芯片更佳。

另外,可编程DSP方案不太可能得到和专用硬件方案一样快的速度。

再考虑视频控制器的例子。

它使用各种次序和长度的记数器来产生用于扫描的地址。

不是用实际的计数器来实现它们,而是用状态机的转换来实现该序列。

除了节约成本外,这种方法还有一个优点,就是释放了微处理器的资源,计数配置被设置或初始化后就不需要微处理器的管理了。

在外围控制中,简单的状态机会非常有效。

例如RLL(run-length-limited)代码。

编码和解码都可以被翻译成状态机,状态机可以在连续的数据流被读出时对其进行检查,并产生输出数据。

工业控制和机器人提供了更广泛的领域来使用简单的控制函数。

如定位机器人的手臂,简单的决策,三角函数计算这样的任务,通常不需要微处理器用堆栈和指针进行的高功耗操作,只需要一个可以存储有限多个状态并允许在各种条件下的简单分支的器件。

数据的解码和编码遇到了对大量媒体进行编码解码时相类似的问题,因为只有这儿不要求所制的图表很明显。

对于这样的问题,带安全位的可编程状态机是最理想的解决方案,因为存储器是内部编程的,不会被使用这个系统的人所访问。

所执行的功能控制器执行的所有系统设计功能都可分为归类到以下的状态机功能:<!--[if !supportLists]-->▪仲裁<!--[endif]--><!--[if !supportLists]-->▪事件监视<!--[endif]--><!--[if !supportLists]-->▪多条件的测试<!--[endif]--><!--[if !supportLists]-->▪时序延时<!--[endif]--><!--[if !supportLists]-->▪控制信号的产生<!--[endif]-->稍后我们会以一个设计实例来显示在设计状态机时,这些功能是如何被使用的。

状态机理论我们来简要分析一下所有时序逻辑系统的原理,有限状态机或简单状态机。

数字系统中,输出取决于过去的输入和当前状态的那部分可被定义为状态机。

其历史可用其内部状态值来概括。

当有新的输入时,FSM依据该输入和当前状态,会产生一个输出,FSM因此而转入下一状态。

这个新的状态同样依据该输入和当前状态。

图2显示了FSM的结构。

内部状态存储在一个标为“Memory”的模块中。

如前所述,需要两个组合函数:转换函数,产生下一状态的值;输出函数,产生状态机输出。

状态图表示如图4所示,FSM的行为可以以图形的方式来说明。

这被称为状态图,或状态转换图,每个椭圆代表一个状态,每个箭头代表状态间的一次转换。

引起转换的输入被显示在各自转换箭头的附近。

图4 状态机图示图5显示了控制定序的状态转换图。

直接控制定序需要一个以状态A到状态B的无条件转移,相似的,条件控制定序显示了根据输入信号I1来决定状态C 到状态D还是状态E的条件转换。

图5 控制定序对于Moore型状态机,输出的产生是用带状态的输出(圆圈)的方法表示,如图6。

类似的,对于Mealy型状态机,输出的产生是用输出赋值到转换(箭头)的方法表示,如图4。

有关Mealy或Moore输出产生的更多细节将在后面给出。

图6 输出的产生对于这种表示法,当有效的输入或输出信号同时出现在同一箭头附近时,输入输出区分不清。

解决的方法通常是在输入个输出之间加一条斜线(图4和图6)。

有时,采用一个附加的引脚列表来说明逻辑极性和输入输出。

如图4所示的状态转换图写出了引起转换的输入值,如果取而代之以转换,用布尔表达式定义输入组合或引起该转换的组合,该状态转换图会更加紧凑。

举个例子,如图7所示,一些转换用带输入START、X1和X2的机制来显示。

在状态1和2的转换中,输入X1和X2被忽略,因而不出现在转换图中。

这样节约了空间,使得其功能更显而易见。

图7 带记忆功能的状态转换图该方法不小心就会出这样的问题。

如图8所示的状态转换,这里有三组输入组合,(I0, I1, I2, I3) ={1011}, {1101} 和 {1111},使得(/I0 * /I2 +I3)和(I0 * I1 + I0 * I2)都为真。

因为转换到两种下一状态是不可能的,所以这里就出现了错误。

因此必须保证这些输入组合不出现,或修改转换条件。

在本例中,修改(I0 * I1+ I0 * I2)为(I0 * I1 + I0 * I2) * / I3就可以解决这个问题。

图8 带冲突分支条件的状态转换图状态转换表格表示第二种状态机表示法是如表1所示的状态转换表格形式。

顶部列出所有可能的输入组合和内部状态。

每行给出下一状态和下一输出,因而,该表格指定了转换函数和输出函数。

然而这种类型的表格不适用于定义实际的状态机,因为实际的状态机有大量的输入,而每个输入组合就占用表格的一行。

举个例子,10个输入的状态机需要1024行。

表1 状态转换表流程图另一种流行的表示法是流程图,状态用矩形框来表示,可选的状态转换用菱形框中的字符串来决定。

该单元可能有多个入口,但通常只有一个出口。

写在矩形状态框内的状态名作为第一个入口。

任何Moore输出表示都写在下面的状态框中,没有寄存的状态前面加一个插入符号(^)。

而状态代码赋值,如果已知的,就写在状态框的右上方。

决策框是菱形或六边形框,其中包含输入信号和逻辑表达式。

分别标识了0和1的两个出口,通向另一个决策框、状态框或Mealy 输出。

卵圆形被用作Mealy型状态机的输出。

插入符号(^)后面跟的状态表示没有寄存。

所有这些框都被用来适应大量的输出信号。

这些符号的使用如图9所示。

每个路径通过决策框后,从一种状态转换到另一种状态,定义输入变量的组合或组合集。

一条路径不必包括所有的输入变量,因此它适应"忽略"。

这些决策树会比表达法更占空间,但是在许多实际情况中,状态机控制器只测试每个状态的输入变量的很小的子集。

并且,决策链通常会反映出设计者所考虑的控制器的行为。

特别需要注意的是,这些测试在FSM 中并不顺序运行,而是被FSM状态转换逻辑并发进行。

转换说明的这种方法,其好处在于可以避免图8中所示的问题。

因为一个路径不可能被分支来定义两个状态路径,所以不会出现这种冲突。

由于可以定义多重的下一状态,因此不存在冲突危险,可以使用更多的复杂决策,使得流程图表示法更加紧凑。

表达式可以被测试,如图10a所示,或多个分支可以从一个译码框引出,如图10b所示。

在第二种情形中,把二进制输入组排列成矢量,对该矢量的不同值进行分支都很方便。

对于状态机的三种表示方法:状态图,状态表和流程图,因为它们都描述相同的硬件结构,所以它们是等价的,可以互换。

每种表示方法都有它特别的优势。

虽然状态转换图最流行,但是因为转换条件被直接记录在转换箭头上,在状态转换要依靠很多输入的情况时,它就会遇到复杂性的问题。