第6章 时序逻辑电路

- 格式:ppt

- 大小:2.50 MB

- 文档页数:3

第6章 时序逻辑电路(Sequential Logic)Sequential logic指的是接收到一触发信号才会改变输出的电路,由于要在触发信号出现时才会改变输出情况,因此在触发信号未出现时具有记忆功能。

在VHDL中,sequential logic一般都会写在process之中,下面会将process 的语法做一简单的介绍,并会描述各种不同的sequential logic的表示方式。

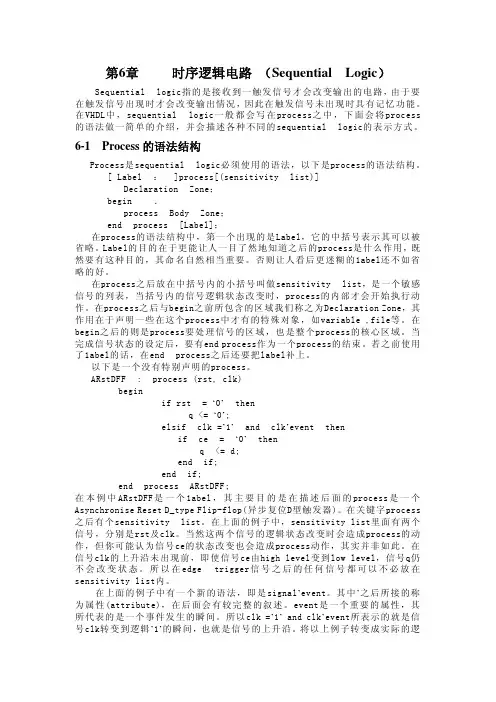

6-1 Process的语法结构Process是sequential logic必须使用的语法,以下是process的语法结构。

[ Label : ]process[(sensitivity list)]Declaration Zone;begin .process Body Zone;end process [Label];在process的语法结构中,第一个出现的是Label,它的中括号表示其可以被省略。

Label的目的在于更能让人一目了然地知道之后的process是什么作用,既然要有这种目的,其命名自然相当重要。

否则让人看后更迷糊的1abel还不如省略的好。

在process之后放在中括号内的小括号叫做sensitivity list,是一个敏感信号的列表,当括号内的信号逻辑状态改变时,process的内部才会开始执行动作。

在process之后与begin之前所包含的区域我们称之为Declaration Zone,其作用在于声明一些在这个process中才有的特殊对象,如variable ,file等。

在begin之后的则是process要处理信号的区域,也是整个process的核心区域。

当完成信号状态的设定后,要有end process作为一个process的结束。

若之前使用了1abel的话,在end process之后还要把label补上。

以下是一个没有特别声明的process。

ARstDFF : process (rst, clk)beginif rst = ‘0’ thenq <= ‘0’;elsif clk =’1’ and clk’event thenif ce = ‘0’ thenq <= d;end if;end if;end process ARstDFF;在本例中ARstDFF是一个1abel,其主要目的是在描述后面的process是一个Asynchronise Reset D_type Flip-flop(异步复位D型触发器)。

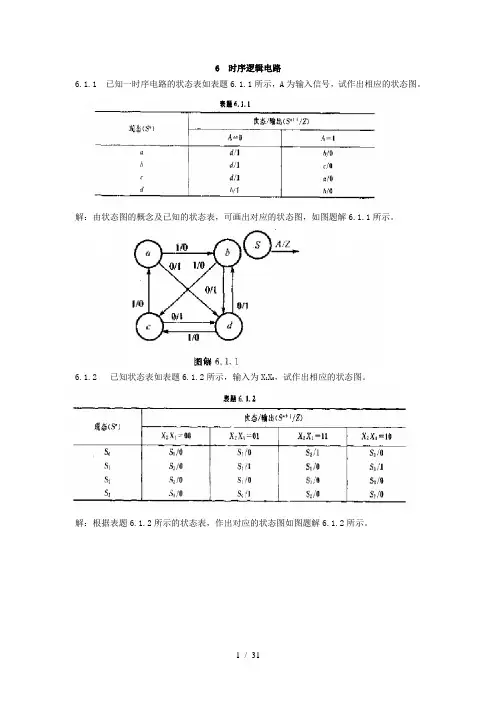

6 时序逻辑电路6.1.1 已知一时序电路的状态表如表题6.1.1所示,A为输入信号,试作出相应的状态图。

解:由状态图的概念及已知的状态表,可画出对应的状态图,如图题解6.1.1所示。

6.1.2已知状态表如表题6.1.2所示,输入为X1X0,试作出相应的状态图。

解:根据表题6.1.2所示的状态表,作出对应的状态图如图题解6.1.2所示。

6.1.3已知状态图如图题6.1.3所示,试列出它的状态表。

解:按图题6.1.3列出的状态表如表题解6.1.3所示。

6.1.5 图题6.1.5所示是某时序电路的状态图,设电路的初始状态为01,当序列A=100110(自左至右输入)时,求该电路输出Z的序列。

解:由图题6.1.5所示的状态图可知,当初态为01,输入信号的序列A=100110时,该时序电路将按图题解6.1.5所示的顺序改变状态,因而对应的输出序列为Z=011010。

6.1.6已知某时序电路的状态表如表题6.1.6所示,输入A,试画出它的状态图。

如果电路的初始状态在b,输入信号A一次是0、1、0、1、1、1、1,试求出其相应的输出。

解:根据表题6.1.6所示的状态表,可直接画出与其对应的状态图,如图题解6.1.6(a)当从初态b开始,依次输入0、1、0、1、1、1、1信号时,该时序电路将按图题解6.1.6(b)所示的顺序改变状态,因而其对应的输出为1、0、1、0、1、0、1。

6.2 同步时序逻辑电路的分析6.2.1 试分析图题6.2.1(a)所示时序电路,画出其状态表和状态图。

设电路的初始状态为0,试画出6.2.1(b)所示波形作用下,Q和Z的波形图。

解:由所给电路图可写出该电路的状态方程和输出方程,分别为1n nQ A QZAQ+=⊕=其状态表如表题解6.2.1所示,状态图如图题解6.2.1(a)所示,Q和Z的波形图如图题解6.2.1(b)所示。

6.2.2 试分析图题6.2.2(a)所示时序电路,画出其状态表和状态图。

第六章时序逻辑电路1 :构成一个五进制的计数器至少需要()个触发器A:5B:4C:3D:2您选择的答案: 正确答案: C知识点:n个触发器可构成一个不大于2n进制的计数器。

A -————-————-——-——--——------——--——----——--———-——-—-———————--—-—————-——--————-—2 :构成一个能存储五位二值代码的寄存器至少需要()个触发器A:5B:4C:3D:2您选择的答案:正确答案: A知识点:一个触发器能储存1位二值代码,所以用n个触发器组成的寄存器能储存n位二值代码。

—-————-—---—---—-—-——--—-—-—----————---—---———--—---—--——---—-------—-——--——3 : 移位寄存器不具有的功能是()A:数据存储B:数据运算C:构成计数器D:构成译码器您选择的答案: 正确答案: D知识点:移位寄存器不仅可以存储代码,还可以实现数据的串行—并行转换、数值的运算、数据处理及构成计数器。

-—-—————---—--——--—-——---——-———-—--—---——---————-————-----——-—--—-————--————4 :下列说法不正确的是()A:时序电路与组合电路具有不同的特点,因此其分析方法和设计方法也不同B:时序电路任意时刻的状态和输出均可表示为输入变量和电路原来状态的逻辑函数C:用包含输出与输入逻辑关系的函数式不可以完整地描述时序电路的逻辑功能D:用包含输出与输入逻辑关系的函数式可以完整地描述时序电路的逻辑功能您选择的答案:正确答案: D知识点:时序逻辑电路的逻辑关系需用三个方程即输出方程、驱动方程及状态方程来描述。

——---—-——-—————--—-——----—---—-—---—-——--—-—------————-——--——--———--—-------5 : 下列说法正确的是( )A:时序逻辑电路某一时刻的电路状态仅取决于电路该时刻的输入信号B:时序逻辑电路某一时刻的电路状态仅取决于电路进入该时刻前所处的状态C:时序逻辑电路某一时刻的电路状态不仅取决于当时的输入信号,还取决于电路原来的状态D:时序逻辑电路通常包含组合电路和存储电路两个组成部分,其中组合电路是必不可少的您选择的答案: 正确答案: C知识点:时序逻辑电路的特点:时序逻辑电路中,任意时刻的输出不仅取决于该时刻的输入,还取决于电路原来的状态.时序逻辑电路通常包含组合电路和存储电路两个组成部分,其中存储电路是必不可少的。