第6章-时序逻辑电路.

- 格式:doc

- 大小:2.16 MB

- 文档页数:31

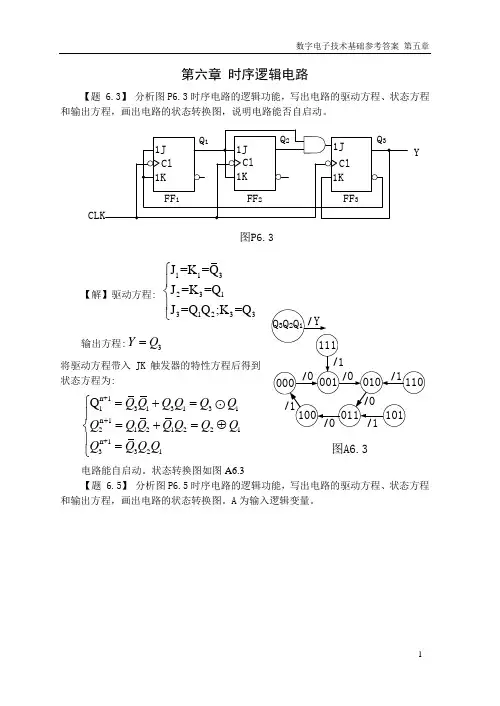

第六章 时序逻辑电路【题 6.3】 分析图P6.3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

Y图P6.3【解】驱动方程:11323131233J =K =Q J =K =Q J =Q Q ;K =Q ⎧⎪⎨⎪⎩ 输出方程:3YQ =将驱动方程带入JK 触发器的特性方程后得到状态方程为:n+11313131n 12121221n+13321Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q +⎧=+=⎪=+=⊕⎨⎪=⎩ 电路能自启动。

状态转换图如图A6.3【题 6.5】分析图P6.5时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入逻辑变量。

图A6.3Y图P6.5【解】驱动方程: 1221212()D AQ D AQ Q A Q Q ⎧=⎪⎨==+⎪⎩输出方程: 21Y AQ Q =将驱动方程带入JK 触发器的特性方程后得到状态方程为:n+112n+1212()Q AQQ A Q Q ⎧=⎪⎨=+⎪⎩ 电路的状态转换图如图A6.51图A6.5【题 6.6】 分析图P6.6时序电路的逻辑功能,画出电路的状态转换图,检查电路能否自启动,说明电路能否自启动。

说明电路实现的功能。

A 为输入变量。

AY图P6.6【解】驱动方程: 112211J K J K A Q ==⎧⎨==⊕⎩输出方程: 1212Y AQ Q AQ Q =+将驱动方程带入JK 触发器的特性方程后得到状态方程为:n+111n+1212QQ Q A Q Q ⎧=⎪⎨=⊕⊕⎪⎩ 电路状态转换图如图A6.6。

A =0时作二进制加法计数,A =1时作二进制减法计数。

01图A6.6【题 6.7】 分析图P6.7时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

Y图P6.7【解】驱动方程: 001023102032013012301;;;J K J Q Q Q K Q J Q Q K Q Q J Q Q Q K Q==⎧⎪=•=⎪⎨==⎪⎪==⎩ 输出方程: 0123Y Q Q Q Q =将驱动方程带入JK 触发器的特性方程后得到状态方程为:*00*1012301*2023012*3012303()Q ()Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q⎧=⎪=++⎪⎨=++⎪⎪=+⎩ 设初态Q 1Q 3Q 2Q 1 Q 0=0000,由状态方程可得:状态转换图如图A6.7。

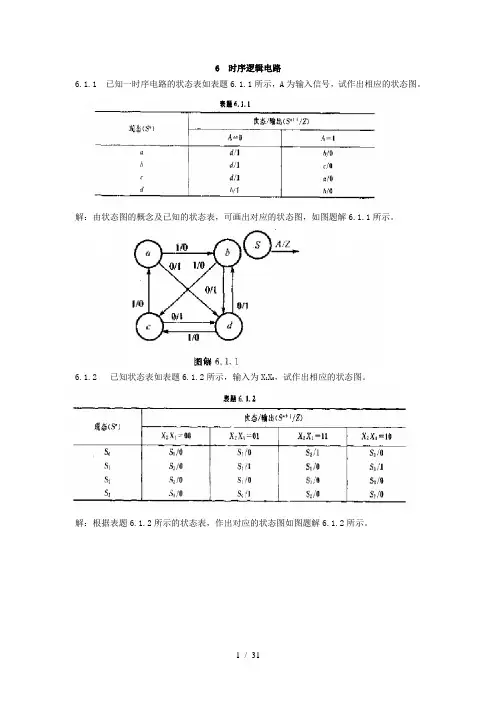

6 时序逻辑电路6.1.1 已知一时序电路的状态表如表题6.1.1所示,A为输入信号,试作出相应的状态图。

解:由状态图的概念及已知的状态表,可画出对应的状态图,如图题解6.1.1所示。

6.1.2已知状态表如表题6.1.2所示,输入为X1X0,试作出相应的状态图。

解:根据表题6.1.2所示的状态表,作出对应的状态图如图题解6.1.2所示。

6.1.3已知状态图如图题6.1.3所示,试列出它的状态表。

解:按图题6.1.3列出的状态表如表题解6.1.3所示。

6.1.5 图题6.1.5所示是某时序电路的状态图,设电路的初始状态为01,当序列A=100110(自左至右输入)时,求该电路输出Z的序列。

解:由图题6.1.5所示的状态图可知,当初态为01,输入信号的序列A=100110时,该时序电路将按图题解6.1.5所示的顺序改变状态,因而对应的输出序列为Z=011010。

6.1.6已知某时序电路的状态表如表题6.1.6所示,输入A,试画出它的状态图。

如果电路的初始状态在b,输入信号A一次是0、1、0、1、1、1、1,试求出其相应的输出。

解:根据表题6.1.6所示的状态表,可直接画出与其对应的状态图,如图题解6.1.6(a)当从初态b开始,依次输入0、1、0、1、1、1、1信号时,该时序电路将按图题解6.1.6(b)所示的顺序改变状态,因而其对应的输出为1、0、1、0、1、0、1。

6.2 同步时序逻辑电路的分析6.2.1 试分析图题6.2.1(a)所示时序电路,画出其状态表和状态图。

设电路的初始状态为0,试画出6.2.1(b)所示波形作用下,Q和Z的波形图。

解:由所给电路图可写出该电路的状态方程和输出方程,分别为1n nQ A QZAQ+=⊕=其状态表如表题解6.2.1所示,状态图如图题解6.2.1(a)所示,Q和Z的波形图如图题解6.2.1(b)所示。

6.2.2 试分析图题6.2.2(a)所示时序电路,画出其状态表和状态图。

数字电子技术(第5版)第6章时序逻辑电路1.(334)利用()可以把集成计数器设计成初态不为零的计数器。

答案.反馈置数法2.(318)时序逻辑电路由( ) 和( ) 两部分组成。

答案.组合电路存储电路3.(337)一个4位的扭环形计数器有()个状态。

答案. 84.(335)集成计数器的级联方式有()和()两种方式。

答案.异步同步5.(333)利用()和()可以改变集成计数器的计数长度。

答案.反馈归零法反馈置数法6.(332)一个模为24的计数器,能够记录到的最大计数值是()。

答案. 237.(331)计数器的模表示计数器的()计数长度。

答案.最大8.(329)构成时序电路的各触发器的时钟输入端都接在一起,这种时序电路称为()。

答案.同步时序电路9.(328)时序电路的输出不仅与电路的()有关,还与电路的()有关。

答案.现态输入信号10.(327)摩尔型时序电路的输出仅由电路的()决定,而与电路的( ) 无关。

(注:教材中没有讲述摩尔型电路的概念,故删去此题)答案.现态输入信号11.(326) 时序逻辑电路的功能描述有 ( ) 、 ( ) 、 ( ) 、 ( ) 。

答案. 逻辑方程式 状态表 状态图 时序图12.(330) 异步时序电路中的各触发器的状态转换 ( )同一时刻进行的。

答案. 不是在13.(336) 一个4位的环形计数器有( )个状态。

答案. 414.(325) 时序逻辑电路可分为 ( ) 和 ( ) 两大类。

答案. 同步时序电路 异步时序电路15.(354) 分析如图7307所示电路,说明其功能。

图7307输 入输 出CR LD T CT P CT CP 3D 2D 1D 0D 3Q 2Q 1Q 0QCO0 × × × × × × × × 000 10××↑3d 2d 1d 0d 3d 2d 1d 0d1111↑×××× 计数 110×××××× 保持 11××××××保持答案. 经分析知,采用了74LS160的同步置数功能。

第6章时序逻辑电路本章的主要知识点时序逻辑电路的基本知识、时序逻辑电路的分析和设计、关于自启动的修正问题、常用的中规模时序电路。

1.参考学时10学时(总学时32学时,课时为48课时可分配12学时)。

2.教学目标(能力要求)●掌握同步时序逻辑电路的分析和设计方法;●掌握电路挂起的修正方法;●掌握常用的中规模时序逻辑电路(计数器、寄存器)的外部特性及使用方法;●掌握脉冲异步时序逻辑电路的分析和设计方法;●掌握中规模时序逻辑电路的分析和设计方法。

3.教学重点●同步时序逻辑电路的设计:包括设计中的原始状态图、状态表、状态化简、状态编码、确定激励函数和输出函数等;●同步时序逻辑电路的自启动的分析:能根据设计好的电路分析电路是否存在自启动的问题,并学会修正它。

●脉冲异步时序逻辑电路的分析和设计方法:了解和同步时序逻辑电路的分析和设计方法的差异性,并熟练掌握脉冲异步时序逻辑电路的分析和设计方法●中规模时序逻辑电路的外部特性及使用方法:通过理论分析来学习常用中规模时序逻辑电路的外部特性及使用方法,通过具体实例来学习中规模时序逻辑电路的分析和设计方法4.教学难点●原始状态图:学生开始不知道如何增加状态,什么时候增加状态●自启动的修正:学生能分析出挂起,但是对于修正比较困难●脉冲异步时序逻辑电路的分析:当脉冲异步时序逻辑电路的存储电路是没用统一时钟端的钟控触发器时,如何分步找到每个触发器的时钟的跳变时刻对学生来说是一大挑战●计数器的使用方法:掌握置数法、清零法、级联法实现任意模的计数器5.教学主要内容(1)时序逻辑电路概述(15分钟)(2)小规模时序逻辑电路分析(120分钟)➢小规模时序逻辑电路的分析方法和步骤➢小规模同步时序逻辑电路的分析➢小规模异步时序逻辑电路的分析(3)小规模时序逻辑电路设计(180分钟)➢小规模时序逻辑电路的设计方法和步骤➢小规模同步时序逻辑电路的设计➢小规模异步时序逻辑电路的设计(4)常用中规模时序逻辑电路(45分钟)➢集成计数器➢寄存器(5)中规模时序逻辑电路的分析和设计(90分钟)➢中规模时序逻辑电路的分析➢中规模时序逻辑电路的设计6.教学过程与方法(1)时序逻辑电路概述(15分钟)简要介绍时序逻辑电路的结构、特点、分类和描述方法等。

数字电路第6章(1时序逻辑电路分析方法)1、第六章时序规律电路本章主要内容6.1概述6.2时序规律电路的分析方法6.3若干常用的时序规律电路6.4时序规律电路的设计方法6.5时序规律电路中的竞争-冒险现象1.时序规律电路的特点2.时序规律电路的分类3.时序规律电路的功能描述方法§6.1概述一、时序规律电路的特点1、功能:任一时刻的输出不仅取决于该时刻的输入;还与电路原来的状态有关。

例:串行加法器:两个多位数从低位到高位逐位相加一、时序规律电路的特点2.电路结构①包含存储电路和组合电路,且存储电路必不行少;②存储电路的输出状态必需反馈到组合电路输入端,与输入变量共同确定组合规律的输出。

yi:输出信号xi:输2、入信号qi:存储电路的状态zi:存储电路的输入可以用三个方程组来描述:Z=G(X,Q)二、时序电路的分类1.依据存储电路中触发器的动作特点不同时序电路存储电路里全部触发器有一个统一的时钟源;触发器状态改变与时钟脉冲同步.同步:异步:没有统一的时钟脉冲,电路中要更新状态的触发器的翻转有先有后,是异步进行的。

二、时序电路的分类2.依据输出信号的特点不同时序电路输出信号不仅取决于存储电路的状态,而且还取决于输入变量。

Y=F(X,Q)米利(Mealy)型:穆尔(Moore)型:输出状态仅取决于存储电路的状态。

犹如步计数器Y=F(Q)三、时序规律电路的功能描述方法描述方法3、规律方程式状态转换表状态转换图时序图三、时序规律电路的功能描述方法(1)规律方程式:写出时序电路的输出方程、驱动方程和状态方程。

输出方程反映电路输出Y与输入X和状态Q之间关系表达式;驱动方程反映存储电路的输入Z与电路输入X和状态Q之间的关系状态方程反映时序电路次态Qn+1与驱动函数Z和现态Qn之间的关系三、时序规律电路的功能描述方法(2)状态〔转换〕表:反映输出Z、次态Qn+1和输入X、现态Qn间对应取值关系的表格。

(3)状态〔转换〕图:(4)时序图:反映时序规律电路状态转换规律及相应输入、输出取值关系的有向图形。

6 时序逻辑电路6.1.1 已知一时序电路的状态表如表题6.1.1所示,A为输入信号,试作出相应的状态图。

解:由状态图的概念及已知的状态表,可画出对应的状态图,如图题解6.1.1所示。

6.1.2已知状态表如表题6.1.2所示,输入为X1X0,试作出相应的状态图。

解:根据表题6.1.2所示的状态表,作出对应的状态图如图题解6.1.2所示。

6.1.3已知状态图如图题6.1.3所示,试列出它的状态表。

解:按图题6.1.3列出的状态表如表题解6.1.3所示。

6.1.5 图题6.1.5所示是某时序电路的状态图,设电路的初始状态为01,当序列A=100110(自左至右输入)时,求该电路输出Z的序列。

解:由图题6.1.5所示的状态图可知,当初态为01,输入信号的序列A=100110时,该时序电路将按图题解6.1.5所示的顺序改变状态,因而对应的输出序列为Z=011010。

6.1.6已知某时序电路的状态表如表题6.1.6所示,输入A,试画出它的状态图。

如果电路的初始状态在b,输入信号A一次是0、1、0、1、1、1、1,试求出其相应的输出。

解:根据表题6.1.6所示的状态表,可直接画出与其对应的状态图,如图题解6.1.6(a)当从初态b开始,依次输入0、1、0、1、1、1、1信号时,该时序电路将按图题解6.1.6(b)所示的顺序改变状态,因而其对应的输出为1、0、1、0、1、0、1。

6.2 同步时序逻辑电路的分析6.2.1 试分析图题6.2.1(a)所示时序电路,画出其状态表和状态图。

设电路的初始状态为0,试画出6.2.1(b)所示波形作用下,Q和Z的波形图。

解:由所给电路图可写出该电路的状态方程和输出方程,分别为1n nQ A Q Z AQ+=⊕=其状态表如表题解6.2.1所示,状态图如图题解6.2.1(a )所示,Q 和Z 的波形图如图题解6.2.1(b )所示。

6.2.2 试分析图题6.2.2(a )所示时序电路,画出其状态表和状态图。

设电路的初始状态为0,画出在图题6.2.2(b )所示波形作用下,Q 和Z 的波形图。

解:由所给电路可写出该电路的状态方程和输出方程1()()nn nnnnn n n n nQZQ ZQ AQ AQ Q AQ AQ Q AQ AQ AZ A Q+=+=+++=+==⊕其状态表如表题解6.2.2所示,状态图如图题解6.2.2(a )所示,Q 和Z 的波形图如图题解6.2.2(b )所示。

6.2.3试分析图题6.2.3所示时序电路,画出状态图。

解:由图题6.2.3所示电路写出其状态方程组和输出方程,分别为1101010n nn Q Q Q AZ AQ Q ++===其状态表如表题解6.2.3所示,状态图如图题解6.2.3所示。

6.2.4分析图题6.2.4所示电路,写出它的激励方程组、状态方程组和输出方程,画出状态表和状态图。

解:该电路的激励方程组为00111011J Q K AQ J Q K ====状态方程组为11011010110()nn n nnnnnn n QQ Q QQ Q AQ Q Q Q A ++==+=+输出方程为10ZAQ Q =根据状态方程组和输出方程可列出状态表,如表题解 6.2.4所示,状态图如图题解6.2.4所示。

6.2.5 分析图题6.2.5所示同步时序电路,写出各触发器的激励方程、电路的状态方程组和输出方程组,画出状态表和状态图。

解:由图题6.2.5所示电路可写出各触发器的激励方程为00110120121J A K AQ J AQ K A J AQ Q K ====== 该电路的状态方程组为1201211011011010100()()nn n n n n n n n n nnn n n n QA Q Q Q Q AQ Q AQ A Q Q QAQ AQ Q A Q Q +++==+=+=+=+ 输出方程为 2ZA Q =根据状态方程组和输出方程列出该电路的状态表,如表题解 6.2.5所示,状态图如图题解6.2.5所示。

6.2.6 试画出图题6.2.6(a )所示时序电路的状态图,并画出对应于CP 的Q 1、Q 0和输出Z 的波形,设电路的初始状态为00。

解:该电路中的激励方程组为01011011J Q K J Q K ====状态方程组和输出方程分别为11101010nn n nn n Q Q Q QQ Q Z Q CP++===根据状态方程组和输出方程可列出该电路的状态表,如表题解6.2.6所示,状态图如图题解6.2.6(a )所示。

图题解6.2.6(b )所示是Q 1、Q 0及Z 的波形图。

6.3 同步时序逻辑电路的设计6.3.1 用JK触发器设计一同步时序电路,其状态如表题6.3.1所示。

解:所要设计的电路有4个状态,需要用两个JK触发器实现。

(1)列状态转换真值表和激励表由表题6.3.1所示的状态表和JK触发器的激励表,可列出转换真值表和对各触发器的激励信号,如表题解6.3.1所示、(2) 求激励方程组和输出方程由表题解6.3.1画出各触发器J 、K 端和电路输出端Y 的卡诺图,如图题解 6.3.1(a )所示。

从而,得到化简得激励方程组。

001101J K J K A Q ====⊕和输出方程10Y Q Q =根据激励方程组和输出方程可画出电路图,如图题解6.3.1(b )所示。

6.3.2 某同步时序电路的状态图如图题6.3.2所示,试写出用D触发器设计时的最简激励方程组。

解:由图题6.3.2所示状态图可知,实现该同步时序需要用三个D 触发器。

(1) 根据状态图列出完全的状态转换真值表,如表题解6.3.2所示。

其中,状态图中未包含的状态为不出现的状态,其次态可用无关项×表示。

(2)画出3个触发器的激励信号D 2、D 1、D 0的卡诺图。

由于D 触发器的特性方程为1n Q +=D,所以可由状态转换真值表直接画出这3个卡诺图,如图题解6.3.2所示。

(2) 由卡诺图得到最简激励方程组201201nn nD Q D Q D Q ===6.3.3 试用上升沿触发的JK 触发器设计一同步时序电路,其状态图如图题6.3.3所示,要求电路使用的门电路最少。

解:图题6.3.3所示的状态图有00、01、10、11四个状态,可用两个上升沿触发的JK触发器实现。

设两个触发器的输出为Q1、Q0,输入信号为A,输出信号为Y。

(1)根据图题6.3.3所示状态图和JK触发器的激励表,可直接列出相应的状态转换真值表和激励信号,如表题解6.3.3所示。

(2)画出激励信号的卡诺图,如图题解6.3.3(a)所示。

(3)由卡诺图得到最简激励方程组00101011J A Q K AQ J AQ K AQ ⎧==⎪⎨==⎪⎩和输出方程110Y AQ Q Q =+(4)根据激励方程组和输出方程画出逻辑电路图,如图题解6.3.3(b )所示。

6.4 异步时序逻辑电路的分析6.4.1 一时序电路如图题6.4.1(a)所示,试画在CP作用下,Q0、Q1、Q2和Z端的波形,设各触发器的初态均为零。

解:图题6.4.1所示电路是异步时序电路。

(1)列出各逻辑方程组①根据逻辑图列出各触发器时钟信号的逻辑表达式 012CP CP CP Q ==⊕(当2Q =0时,对于每个CP 上升沿,011cp cp ==;当2Q =1时,对于每个CP 下降沿,011cp cp ==)2211(,1)CP Q Q cp ==对于上升沿②输出方程1Z Q =③激励方程组222101091111J Q K J Q K J Q K ⎧==⎪==⎨⎪==⎩④状态方程组12222222222221121111011111110200000000100()()()nn n n n nnn n n n n nnnn n n n Q J Q K Q cp Q cp Q cp Q cp Q J Q K Q cp Q cp Q Q cp Q cp QJ Q K Q cp Q cp Q Q cp Q cp +++=++=+=++=+=++=+(2)列出状态表,画出状态图根据状态方程组、输出方程及各触发器的CP 表达式可列出该电路的状态表,如表题解6.4.1所示。

具体推导方法如下:由于022cp cp CP Q ==⊕,所以当Q 2=0时,对应于每个CP 上升沿,021cp cp ==;当Q 2=1时,对应于每个CP 下降沿,021cp cp ==。

而cp 2对应于1Q 上升沿,即对应于Q 1由1变0时为1。

对表中的每一行,首先由10n n Q Q 推导出1110n n Q Q ++,然后根据Q 1是否从1跳变到0来确定cp 2是否为1,再决定12n Q +。

最后,根据1Q 决定Z 。

逐行类推,得到完全状态表。

然后根据表中状态的变化顺序,画出完全状态图,如图题解6.4.1Q,故写入圆圈内。

(a)所示。

由于输出Z值取决于1(3)画出波形图可按状态图的变化顺序,画出Q2、Q1、Q0和Z对应于图题6.4.1(b)所示CP的波形图,如图题解6.4.1(b)所示。

这里需要特别注意:因为CP0=CP1=CP⊕Q2,因此,要根据Q2的逻辑值正确确定状态变化所对应的CP脉冲沿。

6.4.2分析图题6.4.2所示时序电路[CP脉冲同图题6.4.1(b)]。

(1) 写出各触发器的CP 信号方程和激励方程。

(2) 写出电路的状态方程组和输出方程。

(3) 画出状态表及状态图。

(4) 画出电路的时序图。

解:(1)根据逻辑图写出各触发器的CP 信号表达式和激励方程组 ① 各触发器的时钟信号表达式CP 0=CP 1=CP (对于每个CP 上升沿,cp 0=cp 1=1) CP 2=Q 0 (对于Q 0上升沿,cp 2=1) ② 激励方程组001101211J Q K J Q Q K ====(2)写出电路的状态方程组和输出方程组 ①状态方程组122222222222211211110111121110200000000100()()()nn n n nnnnn n n n nnnnn n n n Q J Q K Q cp Q cp Q cp Q cp Q J Q K Q cp Q cp Q Q Q cp Q cp Q J Q K Q cp Q cp Q Q cp Q cp +++=++=+=++=+=++=+②输出方程 20ZQ Q =(3)列出状态表,画出状态图根据状态方程组、输出方程及各触发器始终信号cp n 可列出该电路的状态表,如表题解6.4.2所示。

具体方法如下:由于相应于每个CP 上升沿021cp cp ==,所以对表中的每一行,首先由210n n n Q Q Q 推导出1110n n Q Q ++,最后确定Z 。