2012北邮数字逻辑期中试题-评分及答案

- 格式:doc

- 大小:2.77 MB

- 文档页数:8

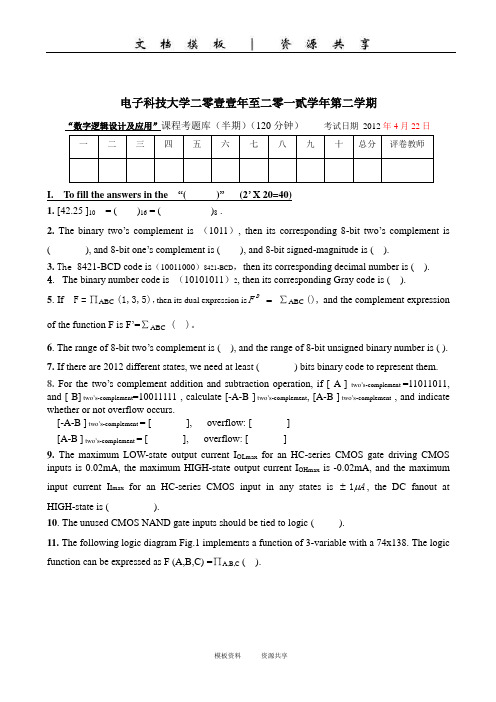

电子科技大学二零壹壹年至二零一贰学年第二学期“数字逻辑设计及应用”课程考题库(半期)(120分钟) 考试日期 2012年4月22日一 二 三 四 五 六 七 八 九 十 总分 评卷教师I. To fill the answers in the “( )” (2’ X 20=40) 1. [42.25 ]10 = ( )16 = ( )8 .2. The binary two ’s complement is (1011), then its corresponding 8-bit two ’s complement is ( ), and 8-bit one ’s complement is ( ), and 8-bit signed-magnitude is ( ).3. The 8421-BCD code is (10011000)8421-BCD ,then its corresponding decimal number is ( ).4. The binary number code is (10101011)2, then its corresponding Gray code is ( ).5. If F = ∏ABC (1,3,5),then its dual expression is =DF ∑ABC (), and the complement expressionof the function F is F ’=∑ABC ( )。

6. The range of 8-bit two ’s complement is ( ), and the range of 8-bit unsigned binary number is ( ).7. If there are 2012 different states, we need at least ( ) bits binary code to represent them.8. For the two ’s complement addition and subtraction operation, if [ A ] two’s -complement =11011011, and [ B] two’s -complement =10011111 , calculate [-A-B ] two’s -complement , [A-B ] two’s -complement , and indicate whether or not overflow occurs.[-A-B ] two’s -complement = [ ], overflow: [ ] [A-B ] two’s -complement = [ ], overflow: [ ]9. The maximum LOW-state output current I OLmax for an HC-series CMOS gate driving CMOS inputs is 0.02mA, the maximum HIGH-state output current I OHmax is -0.02mA, and the maximum input current I Imax for an HC-series CMOS input in any states is A μ1±, the DC fanout at HIGH-state is ( ).10. The unused CMOS NAND gate inputs should be tied to logic ( ).11. The following logic diagram Fig.1 implements a function of 3-variable with a 74x138. The logic function can be expressed as F (A,B,C) =∏A,B,C ( ).Fig.112. The CMOS circuit is shown in Fig.2. Write the function of the circuit. ( )Fig.2II. There is only one correct answer in the following questions.(3’ X 10=30)1. What is the correct 2’s -complement representation of the decimal number -325?( ) A) 1010111011 B) 1101000101 C) 1011010011 D) 10101001102. A 20-to-1 multiplexer need ( ) selection control inputs at least.A) 4B) 5C) 6D) 203. In the 8-radix number system, the result of operation 721/20 is: ( )A) 36.05B) 35.04C) 35.05D) 36.044. What is the duality logic function of the logic function: F = ∑ABC (0,3,5,7)( )A),,(1,2,4,6)A B C ∑ B),,(0,2,4,7)A B C ∑ C),,(0,2,4,7)A B C ∏D),,(1,2,4,6)A B C ∏5. The inputs waveform A,B,C and output waveform F of a combinational circuit are shown as Fig.3. The canonical product-of-sums expression of this circuit is ( )A) (),,2,3,5,7A B C∑B)(),,0,2,4,6A B C∑C) ,,(1,2,4,7)A B C ∏ D),,(0,3,5,6)A B C ∏Fig.36. For each of the following logic expressions, ( ) is the hazard-free circuit.A) F=A’·B + A·C + B’·C B ) F=A’·B + A·C + B·C C) F=(A+B)·(B’+C)·(C+D) D) F=(A+B’)·(B+C)·(C’+D) 7. For the logic function )''()''(),,,(C B D C AB D C B A F '++=, the corresponding minimal sum is ( ).A) A’+B+C’D’ B ) (A’+B+C’)(A’+B+D’) C) A’+B+B’C’D’ D ) A’+B+AC’D’8. The INVERTER and AND-OR-INVERTER circuits are shown as Fig.4 (a), (b) respectively, which conclusion below is correct? ( )A) The delay between input and output of (a) circuit is much less than (b) circuit. B) The delay between input and output of (a) circuit is much greater than (b) circuit. C) The delay between input and output of (a) circuit is about same as (b) circuit. D) The delay relationship between circuit (a) and (b) is uncertainty.Fig.4 (a)Fig.4 (b)9. The circuit shown in Fig.5 realize a logic functin F about input variable W, X, Y . Then, the Fis:( )A) F=,,,(0,1,3,7,9,13,14)w x y z ∑B) F=,,,(0,2,5,7,9,13,14)w x y z ∑C) F=,,,(0,1,3,7,8,12,15)w x y z ∑D) F=,,,(1,2,5,7,9,12,15)w x y zFig.510. Which of the following statements are NOT correct about logic function? ( )A) There are multi-expressions of a logic function ’s minimal sum. B) The canonical sum of a circuit is a sum of minterms.C) Any logic function can be expressed using a sum of minterms or a product of maxterms. D) A sum of prime implicants must be the logic function ’s minimal sum. III. Combinational Circuit Analysis And Design: [30’]1.Write the truth table and the logic function performed by the CMOS circuit in Figure 6. (7’)Fig.62.Simplify the following logic function into the minimal sum expression using Karnaugh map.F(A,B,C,D)= ∑m(0,1,2,4,5,9)+ ∑d(7,8,10,11,12,13) (8’)3.Analyze the following circuit in Fig.7, write the logic expression F(A,B,C).(7’)S A B Z 0 0 0 0 0 10 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 112-to-4decoder Y0Y1Y2Y3G I0I1Y0Y1Y2Y3GI0I1EN A B C D0D1D2D3D4D5D6D7Y AB CFC B AMUXFig.74. Design a code converter circuit that maps 4-bit 2421 cord word to 4-bit 8421 cord word. (8’)(a) Use NAND gates.(b) Use one 74x157 multiplexer and some gates00000001001000110100010101100111100010010000000100100011010010111100110111101111123456789BCD(8421)242100000001001000110100010101100111100010010000000100100011010010111100110111101111D 3D 2D 1D 0I 3I 2I 1I 0Truth Table for a 74x157G_L S 1Y 2Y 3Y 4Y 1 X 0 00 10 0 0 0 1A 2A 3A 4A 1B 2B 3B 4BTruth table:。

北京邮电大学2005——2006学年第一学期 《数字逻辑与数字系统》期末考试试题(B )一、选择题(每小题1分,共10分。

) . 逻辑函数 B B A DEG B B A F +++= 的最简式为( )。

A.B F = B.F=B C.F=0 D.F=1 . 逻辑函数F (ABC )=A ⊙C 的最小项标准式为( )。

A.F=∑(0,3) B. C A C A F += C.F=m 0+m 2+m 5+m 7 D. F=∑(0,1,6,7) .八进制数(573.4)8的十六进制数是( )。

A.(17C.4)16 B.(16B.4)16 C. (17B.8)16 D. (17B.5)16 . 在下列电路中,不是组合逻辑电路的是( )。

A. 编码器 B. 锁存器 C. 全加器 D. 比较器 . 八路数据分配器,其数据输入端有( )个。

A. 1 B. 2 C. 3 D.86.n 个触发器构成的扭环计数器中,无效状态有( )个。

A.nB.2nC.2n-1D. 2n -2n7.构成数字系统必不可少的逻辑执行部件为( )。

A. 控制器B. 计数器C. 基本子系统D. 逻辑门8.电路如图1所示,其中完成A Q Q n 1n +=+电路是( )。

9. 使用256×4位EPROM 芯片构成2K ×32位存储器,共需EPROM 芯片( )片。

A.64B.32C.48D.1610.在ispLSI1032中,巨块是( )。

A.逻辑宏单元B.输出布线C.时钟设置网络D.GLB 及其对应的ORP ,IOC 等的总称二、填空题(每小题2分,共20分)1. 用卡诺图判断函数AC BC AB F ++=和C A C B B A G ++=之间的逻辑关系是______________________。

2. 一个逻辑函数如果有n 个变量,则有__________个最小项。

任何一个逻辑函数可以化成一组________________之和表达式。

2012数字逻辑复习提要一、选择题1.若ABCDEFGH 为最小项,则它有逻辑相邻项个数为( A )A. 8B. 82C. 28D. 162.如果编码0100表示十进制数4,则此码不可能是(B )A. 8421BCD 码B. 5211BCD 码C. 2421BCD 码D. 余3循环码3.构成移位寄存器不能采用的触发器为( D )A. R-S 型B. J-K 型C. 主从型D. 同步型5.以下PLD 中,与、或阵列均可编程的是(C )器件。

A. PROMB. PALC. PLAD. GAL6.函数F(A,B,C,D)=∑m(1,3,4,6,8,10),它的卡诺图如右图所示。

函数的最简与或表达式F= A 。

A . B . C .D . 7.组合电路是指 B 组合而成的电路。

A .触发器 B .门电路 C .计数器 D .寄存器8.电路如右图所示,经CP 脉冲作用后,欲使Q n+1=Q ,则A ,B 输入应为 AB 。

A .A=0,B=0 B .A=1,B=1C .A=0,B=1D .A=1,B=09.一位十进制计数器至少需要 4个触发器。

A .3B .4C .5D .10DB A D B A D B A ++DB A DC A C B A ++D C A D B A C B A ++DB A D B A D B A ++10.n 个触发器构成的扭环计数器中,无效状态有 D 个。

A .n B .2n C .2n-1 D .2n -2n11.GAL 器件的与阵列 ,或阵列 D 。

A .固定,可编程B .可编程,可编程C .固定,固定D .可编程,固定12.下列器件中是 C 现场片。

A .触发器B .计数器C .EPROMD .加法器13.IspLSI 器件中,缩写字母GLB 是指 B 。

A . 全局布线区B .通用逻辑块C .输出布线区D .I/O 单元14. 在下列逻辑部件中,不属于组合逻辑部件的是D 。

第一章1.什么是模拟信号?什么是数字信号?试举出实例。

模拟信号 -------指在时间上和数值上均作连续变化的信号。

例如,温度、压力、交流电压等信号。

数字信号------- 指信号的变化在时间上和数值上都是断续的,阶跃式的,或者说是离散的,这类信号有时又称为离散信号。

例如,在数字系统中的脉冲信号、开关状态等。

2.数字逻辑电路具有哪些主要特点?数字逻辑电路具有如下主要特点:●电路的基本工作信号是二值信号。

●电路中的半导体器件一般都工作在开、关状态。

●电路结构简单、功耗低、便于集成制造和系列化生产。

产品价格低廉、使用方便、通用性好。

●由数字逻辑电路构成的数字系统工作速度快、精度高、功能强、可靠性好。

3.数字逻辑电路按功能可分为哪两种类型?主要区别是什么?根据数字逻辑电路有无记忆功能,可分为组合逻辑电路和时序逻辑电路两类。

组合逻辑电路:电路在任意时刻产生的稳定输出值仅取决于该时刻电路输入值的组合,而与电路过去的输入值无关。

组合逻辑电路又可根据输出端个数的多少进一步分为单输出和多输出组合逻辑电路。

时序逻辑电路:电路在任意时刻产生的稳定输出值不仅与该时刻电路的输入值有关,而且与电路过去的输入值有关。

时序逻辑电路又可根据电路中有无统一的定时信号进一步分为同步时序逻辑电路和异步时序逻辑电路。

4.最简电路是否一定最佳?为什么?一个最简的方案并不等于一个最佳的方案。

最佳方案应满足全面的性能指标和实际应用要求。

所以,在求出一个实现预定功能的最简电路之后,往往要根据实际情况进行相应调整。

5.把下列不同进制数写成按权展开形式。

(1) (4517.239)10(3) (325.744)8(2) (10110.0101)2(4) (785.4AF)16解答(1)(4517.239)10 = 4×103+5×102+1×101+7×100+2×10-1+3×10-2+9×10-3(2)(10110.0101)2= 1×24+1×22+1×21+1×2-2+1×2-4(3)(325.744)8= 3×82+2×81+5×80+7×8-1+4×8-2+4×8-3 (4) (785.4AF)16= 7×162+8×161+5×160+4×16-1+10×16-2+15×16-36.将下列二进制数转换成十进制数、八进制数和十六进制数。

━ ━ ━ ━ ━ ━ ━ ━ ━ 装 ━ ━ ━ ━ ━ ━ ━ 订 ━ ━ ━ ━ ━ ━ ━ 线 ━ ━ ━ ━ ━ ━ ━ ━ ━防灾科技学院2014~ 2015学年 第一学期期中考试 数字逻辑试卷 (A) 使用班级1250421/22 /23/24 答题时间__120分钟一、选择题(本大题共 10 小题,每题 3 分,共 30 分。

)1、下列几种TTL 电路中,输出端可实现线与功能的电路是()。

A 、或非门B 、与非门C 、异或门D 、OC 门2、一个8位二进制数,能够表示的最大无符号整数是( )。

A 、128B 、127C 、255D 、2563、用二进制代码表示十进制数100时,至少要( )位二进制数。

A 、5B 、6C 、7D 、84、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于( )逻辑关系。

A 、与B 、或C 、非D 、与非5、和逻辑式AB 表示不同逻辑关系的逻辑式是( )。

A .B A + B .B A ⋅C .B B A +⋅D .A B A +6、逻辑函数AC B A B F ++=的最简与或式为( )。

A .C AB A F += B .AC B F += C .B A F +=D .C B A F +=7、一个16选一的数据选择器,其地址输入(选择控制输入)端有( ) 个。

A.1B.2C.4D.168、欲实现一个三变量的组合逻辑函数,可选用( )电路的芯片A 、译码器B 、数据选择器C 、译码器或数据选择器D 、加法器9、74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=111时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

A 、01111111B 、11111110C 、11111101D 、1111101110、四输入的译码器,其输出端最多为( )。

A .4个B .8个C .10个D .16个二、判断题。

第一章1。

什么是模拟信号?什么是数字信号?试举出实例。

模拟信号—----指在时间上和数值上均作连续变化的信号。

例如,温度、压力、交流电压等信号.数字信号--—--指信号的变化在时间上和数值上都是断续的,阶跃式的,或者说是离散的,这类信号有时又称为离散信号。

例如,在数字系统中的脉冲信号、开关状态等。

2. 数字逻辑电路具有哪些主要特点?数字逻辑电路具有如下主要特点:●电路的基本工作信号是二值信号。

●电路中的半导体器件一般都工作在开、关状态.●电路结构简单、功耗低、便于集成制造和系列化生产。

产品价格低廉、使用方便、通用性好。

●由数字逻辑电路构成的数字系统工作速度快、精度高、功能强、可靠性好。

3。

数字逻辑电路按功能可分为哪两种类型?主要区别是什么?根据数字逻辑电路有无记忆功能,可分为组合逻辑电路和时序逻辑电路两类。

组合逻辑电路:电路在任意时刻产生的稳定输出值仅取决于该时刻电路输入值的组合,而与电路过去的输入值无关。

组合逻辑电路又可根据输出端个数的多少进一步分为单输出和多输出组合逻辑电路。

时序逻辑电路:电路在任意时刻产生的稳定输出值不仅与该时刻电路的输入值有关,而且与电路过去的输入值有关。

时序逻辑电路又可根据电路中有无统一的定时信号进一步分为同步时序逻辑电路和异步时序逻辑电路。

4. 最简电路是否一定最佳?为什么?一个最简的方案并不等于一个最佳的方案。

最佳方案应满足全面的性能指标和实际应用调整。

5。

把下列不同进制数写成按权展开形式。

(1) (4517.239)10(3) (325.744)8(2)(10110.0101)2(4) (785.4AF)16解答(1)(4517。

239)10 = 4×103+5×102+1×101+7×100+2×10—1+3×10—2+9×10—3(2)(10110.0101)2= 1×24+1×22+1×21+1×2-2+1×2-4(3)(325.744)8 = 3×82+2×81+5×80+7×8-1+4×8-2+4×8—3(4) (785。

电子科技大学2014 - 2015 学年第 二 学期期 中 考试卷课程名称:数字逻辑设计及应用 考试形式:闭卷 考试日期:2015年5月10日 考试时长:120分钟课程成绩构成:平时 %, 期中 %, 小班讨论 %, 期末 % 本试卷试题由__VII___部分构成,共__6___页。

I. Please fill out the correct an swers in the brackets “( )” . ( 2’ X 20 = 40’ )1. [510.5] 10 = ( 111111110.1 )2 = ( 1FE.8 ) 162. (2015)10 =( 0010000000010101 )8421BCD =( 0101001101001000 ) Excess-33. If X’s signed -magnitude representation X SM is 000110102, then (2X)’s 8-bit two’scomplement representation is ( 00110100 ), and (-X/2)’s 8-bit two’s complement representation is ( 11110011 ). 4. If a logic function is, its complement expression is(0,4,5,7),anditsdualexpressionis.(0,2,3,7)5. For CMOS inverters, can different outputs of common CMOS inverters be connected together?[Yes or No] ( No ); Three-state inverters have three-state outputs, which are HIGH 、LOW and ( Hi-Z ). Can different outputs of three-state inverters be connected together? [Yes or No] ( Yes ). 6. Given a binary number X=101101012, its corresponding Gray code is ( 11101111 ).7. If [X] two’s -complement =0111 00112, [Y] two’s -complement =1001 11002, then [X-Y] two’s -complement =( 10101001 1101 0111 ),whether overflow occurs? [Yes or No] ( Yes ). 8. Given 126 different states, it requires at least (7 ) binary bits to represent them.9. For CMOS NOR gates, their unused inputs should connect to ( 0 ) state.10. From Table 1 below, if 74HC devices drive 74LS devices,in HIGH state , DC noise margin V NH is ( 1.84 ), Fan-out NH is ( 200 ); in LOW state , DC noise margin V NL is ( 0.47 ), Fan-out NL is ( 10 ).Table 1Family DescriptionSymbol 74LS 74HC LOW-level input voltage (V) V ILmax 0.8 1.35 LOW-level output voltage (V) V OLmax 0.5 0.33 HIGH-level input voltage (V) V IHmin 2.0 3.85 HIGH-level output voltage (V) V OHmin 2.7 3.84 LOW-level input current (uA) I ILmax -400 1 LOW-level output current (mA) I OLmax 8 4 HIGH-level input current (uA) I IHmax 20 -1 HIGH-level output current (mA)I OHmax-0.4-4II. Choose the correct answer and fill the item number in the brackets. (Singleselection for question 1~8, Multi-selection for 9~10, 2’ X 10=20 ) 1. For logic function, its minimal sum is( C ) A. B.C.D.2. Given a circuit design, its output expression with positive logic is,then its output expression with negative logic is ( C)A.B.C. D.3. For the priority encoder 74X148, its inputs are: I 0-L , I 1-L , I 2-L , I 3-L , I 4-L , I 5-L , I 6-L , I 7-L ,outputsare Y 2-L ,Y 1-L ,Y 0-L . The inputs and outputs are all active-low. When active-low enable input EN _L =0, I 1-L = I 5-L = I 4-L =0, and any other inputs are all 1, then Y 2-L , Y 1-L , Y 0-L is ( B ).A. 110B. 010C. 001D. 101 4. Except enable lines, an 8-1 multiplexer should have ( C ) control/select lines. A. 1 B. 2 C. 3 D. 4 5. The truth table of a circuit is shown in Table 2, the logic expression of this circuit is ( D ).A. F=A+BB. F=S+A+BC.D.6. In one number system is correct, its radix is (B ) A. 5B. 6C. 7D. 8 7. In figure 1, the output logic function is (B )A) B)C)D)8. If the minimal sum of a logic function is same as canonical sum, it may have ( D ).A. static-0 hazardB. static-1 hazardC. both static-0 hazard and static-1 hazardD. neither static-0 hazard nor static-1 hazardC YFigure 19. In two-level AND-OR circuit design, our minimization is aimed to ( B C )A. minimize the inputs of OR gatesB. minimize the number of AND gatesC. minimize the inputs of AND gatesD. shorten the signal path from input to output10. Methods that are ( A B C D ) can be used to describe combinational circuitsA. sum-of-productsB. product-of-sumsC. truth tableD. timing diagramIII. Combinational Circuit Analysis And Design: [40’]1.Given F(W,X,Y,Z)=W/Y/Z/+W/X/Z+WXY/Z+YZ, there are also don’t-cares defined as d(9,12,14). Simplify the logic function F(A,B,C,D) into the minimal-product using Karnaugh map, and write out NOR-NOR logic expression of the minimal-product. (8’)1.2. F minimal-product (W,X,Y,Z)=(Y/+Z)(W/+Z)(W+X/+Y+Z/)3.“或非-或非“表达式F NOR-NOR(W,X,Y,Z) = [(Y/+Z)/+(W/+Z)/+(W+X/+Y+Z/)/]/2. A combinational circuit is shown as below. (8’)(1) Write out the product-of-sum expression of output F(W,X,Y,Z) for the circuit.(2) Analysis all conditions that the static hazard may exit for the circuit, and indicate types of static hazard.(3)Write out the minimal-product of output F(W,X,Y,Z) for the hazard-free.1.F(W,X,Y,Z)=(W+X/)(Y+Z/)(W/+X/+Y/+Z/)2.当WXZ=111,Y变化时(1分),存在静态0冒险当XYZ=111,W变化时(1分),存在静态0冒险3.F hazard-free (W,X,Y,Z)= (W+X/)(Y+Z/)(X/+Z/)3.Implement F(W,X,Y,Z)=W/X/Y/+W/Y/Z+WY/Z/+WX/Y using only a 74x139 and a NAND gate. (6’)1.4.A combinational circuit is shown as below, which contains a 74x138 decoder、two 74x153multiplexer and a OR gate. (8’)(1) List out the truth table for the circuit.(2) Indicate the logic function of the circuit.1.2. 16选1的多路复用器。

北京邮电大学2006—2007学年第二学期《数字电路与逻辑设计》考试试题一.判断题:(10分)(在本题下方的表格中对应题号填入√或×)电路的输出仅取决于电路当前的输入,该电路为组合逻辑电路。

T 由与、或、非门电路构成的逻辑电路一定是组合逻辑电路。

F 与非逻辑门的某输入端悬空时,可认为输入是逻辑“1”。

T 若让TTL 电路的某输入端接低电平,可直接接地或通过任意阻值的F门的输出相互连接并接上拉电阻后,实现“线或”功能。

F 米里 (Mealy) 型时序逻辑电路的输出取决于输入信号和触发器的 T4个触发器不一定能够构成长度为11 的移位型序列信号发生器。

T 状态简化中,若S 1、S 2两状态的输出不同,则S 1、S 2两状态肯定不等价。

T9. 实现模值为11的计数器至少需要4个触发器。

T10. TTL 门输出最大拉电流能力是指输出低电平时流入输出端的最大允许电流。

F二.选择填空题(20分,每空2分)(将正确答案填入本题下方的表格中,可能为多选题。

)1.若输入AB 均为1时,输出F =0,否则输出F =1,输入和输出之间的逻辑关系为:( C )。

(A )异或 (B) 同或 (C) 与非 (D) 或非 2.在图2-1的TTL 门电路中,输出为高电平的有( )(A ). (B ). (C ).(D )图2-13. JK 触发器在时钟脉冲的作用下,如果要使n n Q Q =+1,则输入信号JK 应为 A 。

A ,1==K JB , nn Q K Q J ==, C , nn Q K Q J ==,D ,1,==K Q J n4.函数D)D)(B D)(C A )(C B (A F +++++=的最简或与式为:( )(A)D)D)(C A )(C B (A F ++++= (B)D)A )(C B (A F +++=(C)CD D A C AB F ++= (D)B CD D AC C AB F ++=5.已知某TTL 门电路的输出端最大灌电流负载能力为4mA ,最大拉电流负载能力为2mA 。

中国石油大学(北京)远程教育学院《数字逻辑》期末复习题3. 全加器中向高位的进位 C i i 为(DC.A B i C iD. (A i C i )B i4. 一片十六选一数据选择器,它应有( A A. 4 B. 5 C.105. 欲对78个信息以二进制代码表示,则最少需要( A. 4B. 7C. 786. 十进制数25用8421BCD 码表示为(B ) A.10 101B.0010 01017. 常用的BCD 码有(C ) A:奇偶校验码B:格雷码C:8421码8. 已知Y A AB AB ,下列结果中正确的是(C ) A:Y=AB:Y=BC:Y=A+B9. 下列说法不正确的是(D )A:同一个逻辑函数的不同描述方法之间可相互转换 B:任何一个逻辑函数都可以化成最小项之和的标准形式 C:具有逻辑相邻性的两个最小项都可以合并为一项 D:任一逻辑函数的最简与或式形式是唯一的10. 逻辑函数的真值表如下表所示,其最简与或式是( C )一、单项选择题1. TTL 门电路输入端悬空时,应视为 A.高电平B.低电平2. 最小项A B C D 的逻辑相邻项是( A . ABCDB . ABCD(A ) C.不定D ) D.高阻C . ABCDD .ABCDA. A jB iC iB. ABi(A B i)Ci位地址输入变量D. 16 B )位二进制码D. 10C.100101D.10101D:ASCII 码D : Y A BA: ABC ABC ABCB: ABC ABC ABCC:BC ABD: BC AC11•以下不是逻辑代数重要规则的是(D )。

A.代入规则B.反演规则_C.对偶规则D.加法规则12.已知I函数F A B(C DE)的反函数应该是(A)。

A.F A B C(D E)B.F A B C(D E)C.F A B C(D E)D.F A B C(D E)13•组合逻辑电路一般由( A )组合而成。

北京邮电大学

《数字电路与逻辑设计》期中考试试题 2012.3.24

班级 姓名 班内序号

注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。

一、(每题1分,共20分)判断(填√或×)、选择(单项选择)题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。

) 1.组合逻辑电路中不存在记忆单元。

( √ )

2.晶体管的饱和越深,其对灌电流负载的驱动能力越强,但工作速度越慢。

( √ )

3.TTL 门的某输入端通过100K Ω电阻接电源端时,可认为该输入是逻辑“1”。

( √ )

4.为了增加驱动能力,相同输入时的相同逻辑门输出可以互连在一起使用。

( √ )

5.当两个或两个以上输入信号同时变化,变化前后输出相同,而在输入信号变化时可能出现输出瞬间逻辑错误,称为静态逻辑冒险。

( × ) 6.正逻辑的或非门,对应负逻辑的与非门。

( √ )

7.TTL 与非门的关门电平V OFF 越接近阈值电压V T ,其噪声容限越大。

( √ ) 8.当i j ≠时,必有两个最大项之积0i j M M ⋅=。

( × )

9. 用最简与或式表示一个函数时,其表达式可能不是唯一的。

( √ ) 10.反相器的拉电流负载电阻过小时,主要对输出的高电平产生影响。

( √ ) 11.逻辑项ABCD 的相邻项有: C 。

A.ABCD

B.BCD A

C.ABC D ⋅

D. C A B D ⋅ 12.判断下列两个函数式中,是否存在逻辑冒险。

B 。

1(,,)Y A B C A =+ 2(,,)Y A B C =+

A.不存在,存在

B. 不存在,不存在

C.存在,不存在

D. 存在,存在 13.通过适当连接和控制,可以实现数据双向传输的门电路是 D 。

A. 集电极开路输出的TTL 门电路; B. 互补式输出的TTL 门电路; C. ECL 门电路; D. 三态输出的门电路。

14.若某TTL 门电路的输出端最大灌电流负载能力为16mA ,最大拉电流负载能力为-12mA(流出输出端)。

其输入端低电平的输入最大电流为-1mA(流出输入端),输入端高电平时的输入最大电流为0.1mA(流入输入端),该门电路的扇出系数为: A 。

A . 16 B. 120 C. 12 D. 160 15.图1.1中电路为TTL 电路。

不能实现对应逻辑功能的电路有 A 。

A

B

图1.1

16.逻辑函数为m F(A,B,C,D)(1,3,4,5,6,8,9,12,14)=∑,判断当输入变量ABCD 分别从:0000→0110及 0110→1100时是否存在冒险: D 。

A.不存在,存在

B.存在,存在

C.存在,不存在

D.不存在,不存在 17.根据反演规则,函数F A[B (CD EG)]=++的反函数F = A 。

A. A B(C D)(E G) +++

B. A B C DE G +++

C. A B(C D)(E G) +++

18.函数F(A,B,C)A B = 的标准最小项表达式为: C 。

A. ∑m(2,3,4,5),

B. ∑m(2,3,6,7),

C. ∑m(0,1,6,7),

D. ∑m(0,1,4,5) 19.函数F AC ABCD ABC CD ABD =++++的最简与或式为: B 。

A. ()()()F A B C A D C D =++++ B. F AC CD =+

C. F ABC AD CD =++

20.ECL 逻辑门与TTL 门相比,主要优点有: C 。

A. 抗干扰能力强 B.功耗低 C. 工作速率快

二、(共10分)某器件的内部电路简图如图2.1所示。

(1),说明当输入端C分别0和1时,电路的输出F与输入A、B的逻辑关系。

(2),画出该器件的符号。

图2.1

答案:

(1),当C=1时,F=高阻(3分)

当C=0时,F AB

=(3分)

(2),

C

A

B

(4分)

三、(10分)逻辑电路如图3.1所示。

(1)按照图示电路写出F的原始表达式;(2)将表达式简化为与或式,并填入图3.2的卡诺图;(3)写出用与或非门实现该函数的最简表达式;(4)在图3.3中标明输入信号(未用输入端不许悬空)。

图3.1 图3.2 图3.3

答案:

(1)

F ABC B ABD ACD D ABD

=⋅⋅⋅⋅⋅(2分)

(2)

=+⋅⋅++⋅⋅(2分)

F AB B C D AD B C D

2分)

(3)F B D AC ABD

=⋅++(2分)

(4)

2分)

(10分)图4.1中,已知OC门的输出晶体管管截止时的漏电流为I OH=200μA,四、

导通时允许的最大负载电流为I OL(max)=10mA(输出电压不大于0.5V时);负载门(与门及或门)的低电平(0.5V时)输入电流为I IL=-1mA,高电平(3V 时)输入电流为I IH=50μA,V cc=5V,要求OC门的输出高电平V OH≥3.0V,输出低电平V OL≤0.5V 。

求R的范围。

图4.1

答案:输出高电平:53

50.20.2R K -≤

=Ω+ (5分)

输出低电平:50.5

643103R mA

-≥

=Ω- (5分)

五.(10分)用8选1数据选择器设计一个函数发生电路,实现

(,,,)(1,3,5,7,8,9,10,11)M F A B C D =∏。

8选1数据选择器的输出逻辑函数式为: 021*********()()()W D A A

A D A A A D A A A =⋅⋅+⋅+ 32104210()()D A A A D A A A ++⋅521062107210()()()D A A A D A A A D A A A +++

(1),将函数F 填入卡诺图(图5.1),按照图5.2的地址要求圈出8个子图。

(2),在片脚图(图5.2)中标明D 0-D 7的输入信号。

A B C

图5.2

图5.1

A

B

C

函数填入及子图正确2分

数据端正确,各1分,共8分

六、(10分) 74LS155是地址端公用的双数据分配器,功能表如表6-1所示,请附加最少的门实现如下两输出函数(在给出的图6.1上完成设计,A为高位;)。

1(,,)

F A B C A B C A B C B C

=⋅⋅+⋅⋅+⋅

2(,,)(0123567)

m

F A B C=∑,,,,,,

表6-1 74LS155功能表

6.1

3分,F2,3分,F1,4分

七、(10分)试用两片4位数码比较器74LS85组成三个数的判断电路。

要求能够判别

三个4位二进制数()0123a a a a A 、()0123b b b b B 、()0123c c c c C 相等(输出F 1=0,F 2=1)及A 最大(输出F 1=1,F 2=0)。

在图7.1上完成设计,可附加与门。

(芯片74LS85的3个输出端,分别表示在A>B 时

Y A>B =1;A=B 时Y A=B =1;A<B 时Y A<B =1)。

答案:评分:3个输入各2分,2个输出各2分

01230123

八、(10分)用或非门实现函数,,,)F A B C D AC A BD A CD =+⋅+(,要求没有逻辑冒险。

(1),将函数填入图8.1的卡诺图;(2),画出逻辑电路。

图8.1

答案:6分+4分

F

九、应用问题简答:

已知供电电压为5V 的74S 系列器件的I OH =-1mA ,I OL =20mA ,74LS 系列器件的I OH =-0.4mA ,I OL =8mA 。

5V

+5V

()

d ()

c ()b ()a

图9.1

1.现需驱动一个发光二极管(正向压降为 1.5V ),要求发光时的电流I LED =10mA 。

(1)应使用74S 系列还是74LS 系列器件?74S 系列(2分) (2)应使用图9.1(a )电路还是(b )电路?(b )电路(2分) (3)简述图中R 的作用。

限流(2分)

2. 若需驱动一个5V 继电器,继电器的电流为I J =5mA 。

(图中D 的作用是抑制自感生的高电压,起到保护器件的作用)。

(1)可以选择哪个系列的器件?74S 或74LS (2分)

(2)应使用图9.1(c )电路还是(d )电路?(d )电路(2分)。