阻抗计算公式、polarsi9000(教程)

- 格式:doc

- 大小:1.20 MB

- 文档页数:16

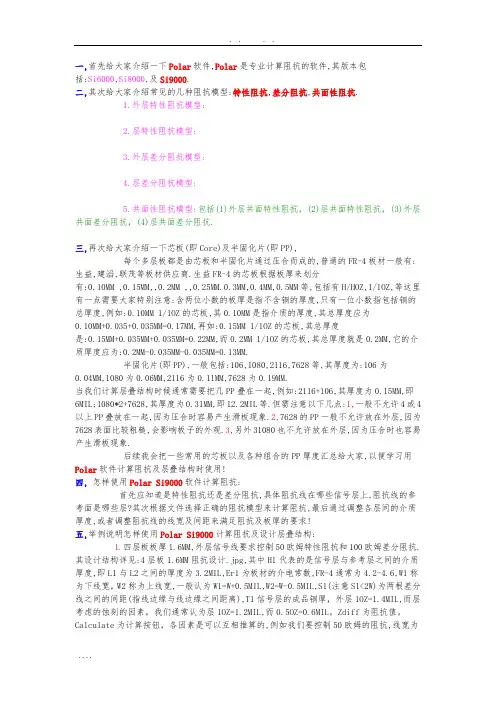

一,首先给大家介绍一下Polar软件,Polar是专业计算阻抗的软件,其版本包括:Si6000,Si8000,及Si9000.二,其次给大家介绍常见的几种阻抗模型:特性阻抗,差分阻抗,共面性阻抗.1.外层特性阻抗模型:2.内层特性阻抗模型:3.外层差分阻抗模型:4.内层差分阻抗模型:5.共面性阻抗模型:包括(1)外层共面特性阻抗,(2)内层共面特性阻抗,(3)外层共面差分阻抗,(4)内层共面差分阻抗.三,再次给大家介绍一下芯板(即Core)及半固化片(即PP),每个多层板都是由芯板和半固化片通过压合而成的,普通的FR-4板材一般有:生益,建滔,联茂等板材供应商.生益FR-4的芯板根据板厚来划分有:0.10MM ,0.15MM,,0.2MM ,,0.25MM.0.3MM,0.4MM,0.5MM等,包括有H/HOZ,1/1OZ,等这里有一点需要大家特别注意:含两位小数的板厚是指不含铜的厚度,只有一位小数指包括铜的总厚度,例如:0.10MM 1/1OZ的芯板,其0.10MM是指介质的厚度,其总厚度应为0.10MM+0.035+0.035MM=0.17MM,再如:0.15MM 1/1OZ的芯板,其总厚度是:0.15MM+0.035MM+0.035MM=0.22MM,而0.2MM 1/1OZ的芯板,其总厚度就是0.2MM,它的介质厚度应为:0.2MM-0.035MM-0.035MM=0.13MM.半固化片(即PP),一般包括:106,1080,2116,7628等,其厚度为:106为0.04MM,1080为0.06MM,2116为0.11MM,7628为0.19MM.当我们计算层叠结构时候通常需要把几张PP叠在一起,例如:2116+106,其厚度为0.15MM,即6MIL;1080*2+7628,其厚度为0.31MM,即12.2MIL等.但需注意以下几点:1,一般不允许4张或4张以上PP叠放在一起,因为压合时容易产生滑板现象.2,7628的PP一般不允许放在外层,因为7628表面比较粗糙,会影响板子的外观.3,另外3张1080也不允许放在外层,因为压合时也容易产生滑板现象.后续我会把一些常用的芯板以及各种组合的PP厚度汇总给大家,以便学习用Polar软件计算阻抗及层叠结构时使用!四, 怎样使用Polar Si9000软件计算阻抗:首先应知道是特性阻抗还是差分阻抗,具体阻抗线在哪些信号层上,阻抗线的参考面是哪些层?其次根据文件选择正确的阻抗模型来计算阻抗,最后通过调整各层间的介质厚度,或者调整阻抗线的线宽及间距来满足阻抗及板厚的要求!五,举例说明怎样使用Polar Si9000计算阻抗及设计层叠结构:1.四层板板厚1.6MM,外层信号线要求控制50欧姆特性阻抗和100欧姆差分阻抗.其设计结构详见:4层板1.6MM阻抗设计.jpg,其中H1代表的是信号层与参考层之间的介质厚度,即L1与L2之间的厚度为3.2MIL,Er1为板材的介电常数,FR-4通常为4.2-4.6,W1称为下线宽,W2称为上线宽,一般认为W1=W+0.5MIL,W2=W-0.5MIL,S1(注意S1<2W)为两根差分线之间的间距(指线边缘与线边缘之间距离),T1信号层的成品铜厚,外层1OZ=1.4MIL,而内层考虑的蚀刻的因素,我们通常认为内层1OZ=1.2MIL,而0.5OZ=0.6MIL。

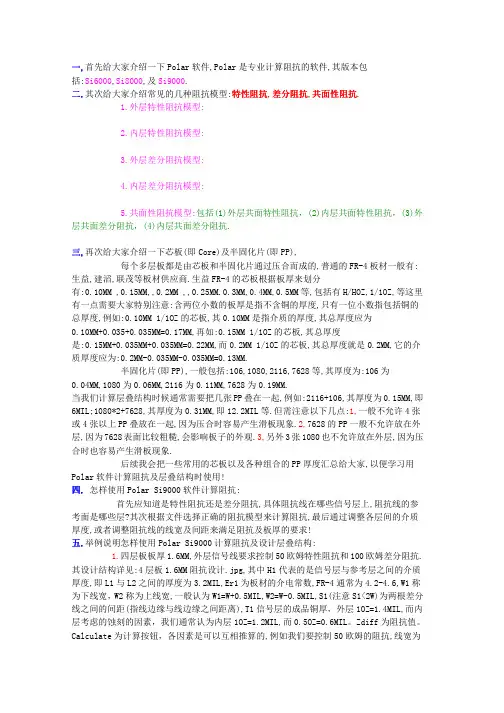

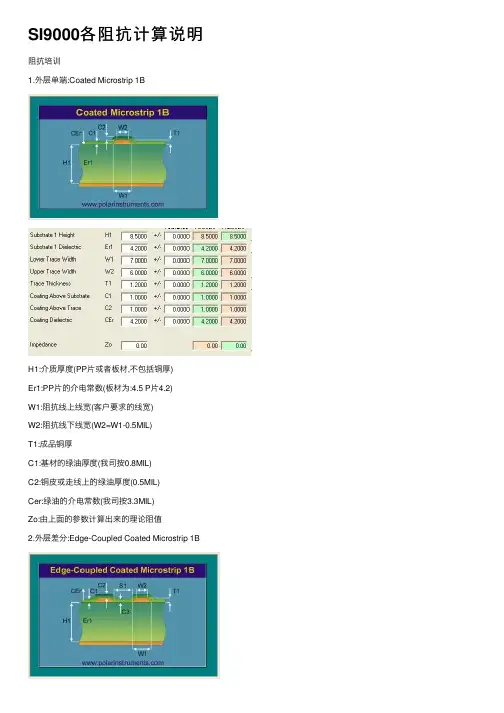

SI9000各阻抗计算说明阻抗培训1.外层单端:Coated Microstrip 1BH1:介质厚度(PP⽚或者板材,不包括铜厚)Er1:PP⽚的介电常数(板材为:4.5 P⽚4.2)W1:阻抗线上线宽(客户要求的线宽)W2:阻抗线下线宽(W2=W1-0.5MIL)T1:成品铜厚C1:基材的绿油厚度(我司按0.8MIL)C2:铜⽪或⾛线上的绿油厚度(0.5MIL)Cer:绿油的介电常数(我司按3.3MIL)Zo:由上⾯的参数计算出来的理论阻值2.外层差分:Edge-Coupled Coated Microstrip 1BH1:介质厚度(PP⽚或者板材,不包括铜厚) Er1:PP⽚的介电常数(板材为:4.5 P⽚4.2) W1:阻抗线上线宽(客户要求的线宽)W2:阻抗线下线宽(W2=W1-0.5MIL)S1:阻抗线间距(客户原稿)T1:成品铜厚C1:基材的绿油厚度(我司按0.8MIL)C2:铜⽪或⾛线上的绿油厚度(0.5MIL)C3:基材上⾯的绿油厚度(0.50MIL) Cer:绿油的介电常数(我司按3.3MIL)3.内层单端:Offset Stripline 1B1AH1:介质厚度(PP⽚或者光板,不包括铜厚) Er1:H1厚度PP⽚的介电常数(P⽚4.2MIL) H2:介质厚度(PP⽚或者光板,不包括铜厚)Er2:H2厚度PP⽚的介电常数(P⽚4.2MIL)W1:阻抗线上线宽(客户要求的线宽)W2:阻抗线下线宽(W2=W1-0.5MIL)T1:成品铜厚Zo:由上⾯的参数计算出来的理论阻值4.内层差分:Edge-Couled Offset Stripline 1B1AH1:介质厚度(PP⽚或者光板,不包括铜厚)Er1:H1厚度PP⽚的介电常数(P⽚4.2MIL)H2:介质厚度(PP⽚或者光板,不包括铜厚)Er2:H2厚度PP⽚的介电常数(P⽚4.2MIL)W1:阻抗线上线宽(客户要求的线宽)W2:阻抗线下线宽(W2=W1-0.5MIL)S1:客户要求的线距T1:成品铜厚Zo:由上⾯的参数计算出来的理论阻值5.外层单端共⾯地:Coated Coplanar Waveguide With Ground 1BH1:介质厚度(PP⽚或者板材,不包括铜厚)Er1:PP⽚的介电常数(板材为:4.5 P⽚4.2)W1:阻抗线上线宽(客户要求的线宽)W2:阻抗线下线宽(W2=W1-0.5MIL)D1:阻抗线到两边铜⽪的距离T1:成品铜厚C1:基材的绿油厚度(我司按0.8MIL)C2:铜⽪或⾛线上的绿油厚度(0.5MIL)Cer:绿油的介电常数(我司按3.3MIL)Zo:由上⾯的参数计算出来的理论阻值6.外层差分共⾯地:Diff Coated Coplanar Waveguide With Ground 1BH1:介质厚度(PP⽚或者板材,不包括铜厚) Er1:PP⽚的介电常数(板材为:4.5 P⽚4.2) W1:阻抗线上线宽(客户要求的线宽)W2:阻抗线下线宽(W2=W1-0.5MIL)S1:阻抗线间距(客户原稿)D1:阻抗线到铜⽪的距离T1:成品铜厚C1:基材的绿油厚度(我司按0.8MIL)C2:铜⽪或⾛线上的绿油厚度(0.5MIL)C3:基材上⾯的绿油厚度(0.50MIL) Cer:绿油的介电常数(我司按3.3MIL) Zo:由上⾯的参数计算出来的理论阻值。

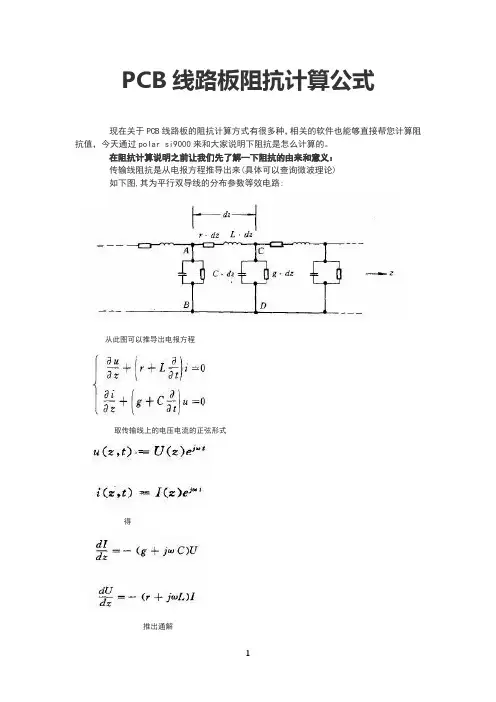

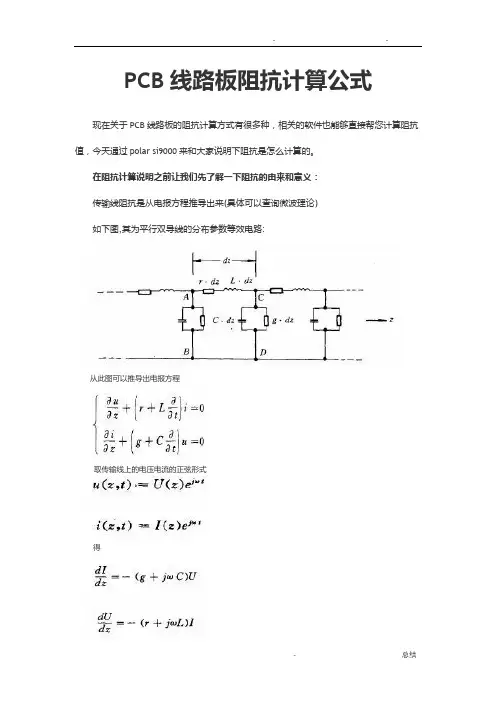

PCB线路板阻抗计算公式现在关于PCB线路板得阻抗计算方式有很多种,相关得软件也能够直接帮您计算阻抗值,今天通过polar si9000来与大家说明下阻抗就是怎么计算得。

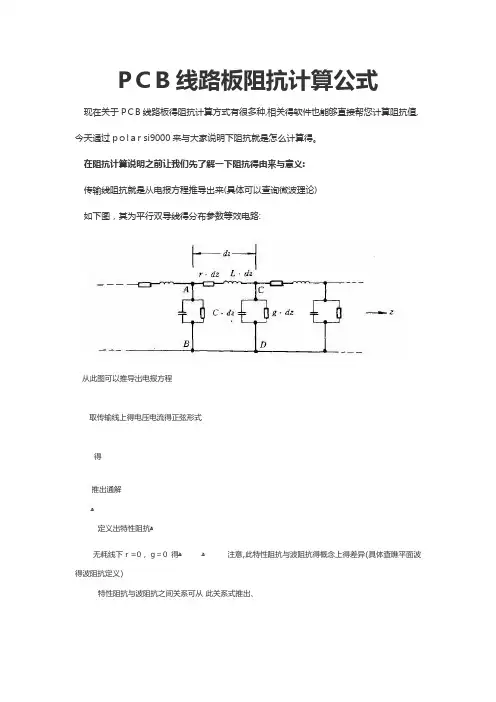

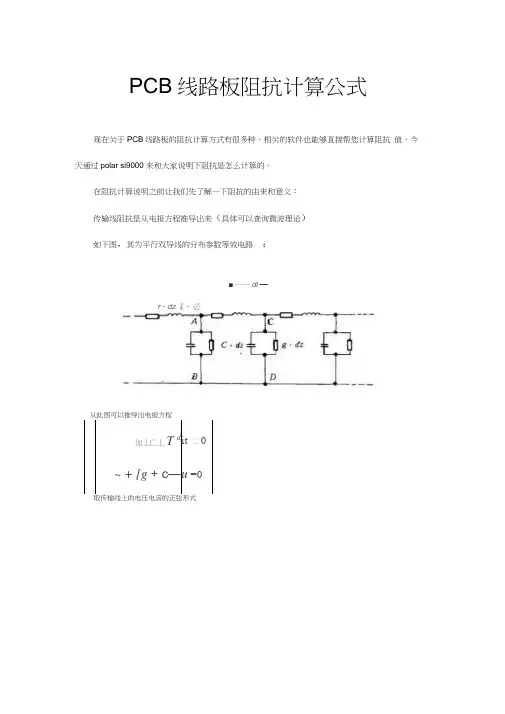

在阻抗计算说明之前让我们先了解一下阻抗得由来与意义:传输线阻抗就是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线得分布参数等效电路:从此图可以推导出电报方程取传输线上得电压电流得正弦形式得推出通解ﻫ定义出特性阻抗ﻫ无耗线下r=0,g=0 得ﻫﻫ注意,此特性阻抗与波阻抗得概念上得差异(具体查瞧平面波得波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出、Ok,理解特性阻抗理论上就是怎么回事情,瞧瞧实际上得意义,当电压电流在传输线传播得时候,如果特性阻抗不一致所求出得电报方程得解不一致,就造成所谓得反射现象等等、在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配得重要性在此展现出来、叠层(stackup)得定义我们来瞧如下一种stackup,主板常用得8 层板(4 层power/ground以及4 层走线层,sggssggs,分别定义为L1,L2…L8)因此要计算得阻抗为L1,L4,L5,L8下面熟悉下在叠层里面得一些基本概念,与厂家打交道经常会使用得Oz 得概念Oz本来就是重量得单位Oz(盎司)=28、3 g(克)在叠层里面就是这么定义得,在一平方英尺得面积上铺一盎司得铜得厚度为1Oz,对应得单位如下介电常数(DK)得概念电容器极板间有电介质存在时得电容量Cx与同样形状与尺寸得真空电容量Co之比为介电常数:ﻫε =Cx/Co=ε'-ε”ﻫPrepreg/Core 得概念pp就是种介质材料,由玻璃纤维与环氧树脂组成,core其实也就是pp类型介质,只不过她两面都覆有铜箔,而pp没有、传输线特性阻抗得计算首先,我们来瞧下传输线得基本类型,在计算阻抗得时候通常有如下类型:微带线与带状线,对于她们得区分,最简单得理解就是,微带线只有1个参考地,而带状线有2个参考地,如下图所示对照上面常用得8 层主板,只有top 与bottom走线层才就是微带线类型,其她得走线层都就是带状线类型在计算传输线特性阻抗得时候, 主板阻抗要求基本上就是:单线阻抗要求55 或者60O hm,差分线阻抗要求就是70~110Ohm,厚度要求一般就是1~2mm,根据板厚要求来分层得到各厚度高度、在此假设板厚为1、6mm,也就就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下得叠层来走线。

一,首先给大家介绍一下Polar软件,Polar是专业计算阻抗的软件,其版本包括:Si6000,Si8000,及Si9000.二,其次给大家介绍常见的几种阻抗模型:特性阻抗,差分阻抗,共面性阻抗.1.外层特性阻抗模型:2.层特性阻抗模型:3.外层差分阻抗模型:4.层差分阻抗模型:5.共面性阻抗模型:包括(1)外层共面特性阻抗,(2)层共面特性阻抗,(3)外层共面差分阻抗,(4)层共面差分阻抗.三,再次给大家介绍一下芯板(即Core)及半固化片(即PP),每个多层板都是由芯板和半固化片通过压合而成的,普通的FR-4板材一般有:生益,建滔,联茂等板材供应商.生益FR-4的芯板根据板厚来划分有:0.10MM ,0.15MM,,0.2MM ,,0.25MM.0.3MM,0.4MM,0.5MM等,包括有H/HOZ,1/1OZ,等这里有一点需要大家特别注意:含两位小数的板厚是指不含铜的厚度,只有一位小数指包括铜的总厚度,例如:0.10MM 1/1OZ的芯板,其0.10MM是指介质的厚度,其总厚度应为0.10MM+0.035+0.035MM=0.17MM,再如:0.15MM 1/1OZ的芯板,其总厚度是:0.15MM+0.035MM+0.035MM=0.22MM,而0.2MM 1/1OZ的芯板,其总厚度就是0.2MM,它的介质厚度应为:0.2MM-0.035MM-0.035MM=0.13MM.半固化片(即PP),一般包括:106,1080,2116,7628等,其厚度为:106为0.04MM,1080为0.06MM,2116为0.11MM,7628为0.19MM.当我们计算层叠结构时候通常需要把几PP叠在一起,例如:2116+106,其厚度为0.15MM,即6MIL;1080*2+7628,其厚度为0.31MM,即12.2MIL等.但需注意以下几点:1,一般不允许4或4以上PP叠放在一起,因为压合时容易产生滑板现象.2,7628的PP一般不允许放在外层,因为7628表面比较粗糙,会影响板子的外观.3,另外31080也不允许放在外层,因为压合时也容易产生滑板现象.后续我会把一些常用的芯板以及各种组合的PP厚度汇总给大家,以便学习用Polar软件计算阻抗及层叠结构时使用!四,怎样使用Polar Si9000软件计算阻抗:首先应知道是特性阻抗还是差分阻抗,具体阻抗线在哪些信号层上,阻抗线的参考面是哪些层?其次根据文件选择正确的阻抗模型来计算阻抗,最后通过调整各层间的介质厚度,或者调整阻抗线的线宽及间距来满足阻抗及板厚的要求!五,举例说明怎样使用Polar Si9000计算阻抗及设计层叠结构:1.四层板板厚1.6MM,外层信号线要求控制50欧姆特性阻抗和100欧姆差分阻抗.其设计结构详见:4层板1.6MM阻抗设计.jpg,其中H1代表的是信号层与参考层之间的介质厚度,即L1与L2之间的厚度为3.2MIL,Er1为板材的介电常数,FR-4通常为4.2-4.6,W1称为下线宽,W2称为上线宽,一般认为W1=W+0.5MIL,W2=W-0.5MIL,S1(注意S1<2W)为两根差分线之间的间距(指线边缘与线边缘之间距离),T1信号层的成品铜厚,外层1OZ=1.4MIL,而层考虑的蚀刻的因素,我们通常认为层1OZ=1.2MIL,而0.5OZ=0.6MIL。

PCB线路板阻抗计算公式现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000 来和大家说明下阻抗是怎么计算的。

在阻抗计算说明之前让我们先了解一下阻抗的由来和意义:传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:■------ di —r - dz£・必从此图可以推导出电报方程加丄匚丄T d ~ + [g+ c—it 二0 u=0取传输线上的电压电流的正弦形式劣==一+ j如oc= - -f*推岀通解辽/『+ jy g + J^c定义岀特性阻抗无耗线下r=0, g=0 得7 -区%、注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)|£C = Ep特性阻抗与波阻抗之间关系可从厂此关系式推岀.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等•在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来•叠层(stackup)的定义我们来看如下一种 stackup,主板常用的8层板(4层power/ground 以及4层走线 层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8Oz 的概念 Oz 本来是重量的单位 0z (盎司)=28.3 g (克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为 1Oz,对应的单位如下介电常数(DK )的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量 Co 之比为介电常数:e = Cx/Co = - ee"'Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜 箔,而pp 没有.外匚走线L1F 面熟悉下在叠层里面的一些基本概念 ,和厂家打交道经常会使用的TQP L2L3L4L5 L6 L7CORFCORE .005"f 9 OZ(QiitAr l^yer+Pl^t ng)1 OZ(GMD)1 OZ1 OZ (VCC) I OZ (S1GMAL) 1 OZ(SIGNAL) 1 OZ(GrJD)F'repreo 丄 rril传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型:微带线和带状 线,对于他们的区分,最简单的理解是,微带线只有1个参考地,而带状线有2个参考地,如下图 所示诫带线 带状线对照上面常用的8层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候,主板阻抗要求基本上是:单线阻抗要求55或者600hm, 差分线阻抗要求是 70~1100hm ,厚度要求一般是1~2mm ,根据板厚要求来分层得到各厚度高度•在此假设板厚为1.6mm ,也就是63mil 左右,单端阻抗要求60Ohm ,差分阻抗要求 100Ohm ,我们假设以如下的叠层来走线。

阻抗匹配计算公式si9000概述本文档将介绍阻抗匹配计算公式s i9000的基本原理和使用方法。

阻抗匹配是电子电路设计中常用的技术,用于优化信号传输和减少反射。

什么是阻抗匹配阻抗匹配是一种通过调整电路中的阻抗,使其与信号源或负载的阻抗相匹配的技术。

当信号在电路中传输时,如果信号源和负载之间的阻抗不匹配,会导致信号的反射和损耗。

而通过阻抗匹配,可以最大限度地提高信号传输的效率和质量。

阻抗匹配原理阻抗匹配的基本原理是利用电路中的传输线特性以及一些补偿元件,调整输入和输出阻抗,使其与信号源或负载的阻抗相等。

这样可以使信号在电路中无反射地传输,并最大限度地传递能量。

常用的阻抗匹配方法包括使用传输线、补偿电容和电感元件等。

通过合理选择这些元件的数值和布局,可以实现阻抗匹配,并优化电路的性能。

阻抗匹配计算公式si9000s i9000是一种常用的阻抗匹配计算公式,可以用于计算阻抗匹配网络的参数。

以下是s i9000的计算公式:s i9000=(Z2-Z0)/(Z2+Z0)其中,s i9000表示阻抗匹配系数,Z2表示负载阻抗,Z0表示信号源的阻抗。

使用方法使用阻抗匹配计算公式s i9000,可以快速计算阻抗匹配网络的参数。

以下是使用s i9000的步骤:1.确定信号源的阻抗Z0和负载阻抗Z2的数值。

2.将上述数值代入si9000的计算公式中。

3.计算公式给出的si9000值即为阻抗匹配系数。

根据阻抗匹配系数,可以选择合适的补偿元件,并根据其数值和布局,调整电路的阻抗,以实现阻抗匹配。

注意事项在使用阻抗匹配计算公式si9000时,需要注意以下事项:1.确保输入的阻抗数值准确无误。

2.选择合适的补偿元件时,考虑其频率响应和功耗等因素。

3.进行阻抗匹配时,应综合考虑整个电路的性能和稳定性。

总结阻抗匹配计算公式si9000是一种实用工具,可用于优化电路的阻抗匹配。

通过合理选择补偿元件,可以实现阻抗的匹配并提高信号传输的效率。

一,首先给大家介绍一下Polar软件,Polar是专业计算阻抗的软件,其版本包括:Si6000,Si8000,及Si9000.二,其次给大家介绍常见的几种阻抗模型:特性阻抗,差分阻抗,共面性阻抗.7 g1 B: b4 A+ [0 W, d# X1.外层特性阻抗模型:3 c7 ?" ~0 m8 G& X3 k% }2.内层特性阻抗模型:. k2 r/ N# G* I, U. d3 `# [! F3.外层差分阻抗模型:; h+ Z: ?3 B9 w/ S2 t8 J2 _9 S# h& X( k4 _4.内层差分阻抗模型:* N8 N+ D9 F# r0 F8 h" k0 s# @1 V) z* |' X- k7 E5.共面性阻抗模型:包括(1)外层共面特性阻抗,(2)内层共面特性阻抗,(3)外层共面差分阻抗,(4)内层共面差分阻抗.三,再次给大家介绍一下芯板(即Core)及半固化片(即PP),8 a& L7 C2 a5 e; M9 A( @每个多层板都是由芯板和半固化片通过压合而成的,普通的FR-4板材一般有:生益,建滔,联茂等板材供应商.生益FR-4的芯板根据板厚来划分有:0.10MM ,0.15MM,,0.2MM ,,0.25MM.0.3MM,0.4MM,0.5MM等,包括有H/HOZ,1/1OZ,等这里有一点需要大家特别注意:含两位小数的板厚是指不含铜的厚度,只有一位小数指包括铜的总厚度,例如:0.10MM 1/1OZ的芯板,其0.10MM是指介质的厚度,其总厚度应为0.10MM+0.035+0.035MM=0.17MM,再如:0.15MM 1/1OZ的芯板,其总厚度是:0.15MM+0.035MM+0.035MM=0.22MM,而0.2MM 1/1OZ的芯板,其总厚度就是0.2MM,它的介质厚度应为:0.2MM-0.035MM-0.035MM=0.13MM.半固化片(即PP),一般包括:106,1080,2116,7628等,其厚度为:106为0.04MM,1080为0.06MM,2116为0.11MM,7628为0.19MM.( u4 f% A8 v4 f* M% u当我们计算层叠结构时候通常需要把几张PP叠在一起,例如:2116+106,其厚度为0.15MM,即6MIL;1080*2+7628,其厚度为0.31MM,即12.2MIL等.但需注意以下几点:1,一般不允许4张或4张以上PP叠放在一起,因为压合时容易产生滑板现象.2,7628的PP一般不允许放在外层,因为7628表面比较粗糙,会影响板子的外观.3,另外3张1080也不允许放在外层,因为压合时也容易产生滑板现象.后续我会把一些常用的芯板以及各种组合的PP厚度汇总给大家,以便学习用Polar软件计算阻抗及层叠结构时使用!四,怎样使用Polar Si9000软件计算阻抗:( E& A* }* x4 X首先应知道是特性阻抗还是差分阻抗,具体阻抗线在哪些信号层上,阻抗线的参考面是哪些层?其次根据文件选择正确的阻抗模型来计算阻抗,最后通过调整各层间的介质厚度,或者调整阻抗线的线宽及间距来满足阻抗及板厚的要求!( S6 t; o* g8 n五,举例说明怎样使用Polar Si9000计算阻抗及设计层叠结构:1.四层板板厚1.6MM,外层信号线要求控制50欧姆特性阻抗和100欧姆差分阻抗.其设计结构详见:4层板1.6MM阻抗设计.jpg,其中H1代表的是信号层与参考层之间的介质厚度,即L1与L2之间的厚度为3.2MIL,Er1为板材的介电常数,FR-4通常为4.2-4.6,W1称为下线宽,W2称为上线宽,一般认为W1=W+0.5MIL,W2=W-0.5MIL,S1(注意S1<2W)为两根差分线之间的间距(指线边缘与线边缘之间距离),T1信号层的成品铜厚,外层1OZ=1.4MIL,而内层考虑的蚀刻的因素,我们通常认为内层1OZ=1.2MIL,而0.5OZ=0.6MIL。

一,首先给大家介绍一下Polar 软件,Polar 是专业计算阻抗的软件,其版本包括:Si6000,Si8000,及Si9000.二,其次给大家介绍常见的几种阻抗模型:特性阻抗,差分阻抗,共面性阻抗.. n- a$ t9 c1 o6 i1.外层特性阻抗模型:8 d7 D- O: @' G) W: x2.内层特性阻抗模型:6 {' {- b# F- g1 p3.外层差分阻抗模型:+ l% V3 Z& G1 }; V( p2 w9 o4.内层差分阻抗模型:& f8 D1 {7 s& \% K% T4 E" v3 n; W/ K$ o! \1 D! A ] 5.共面性阻抗模型:包括(1)外层共面特性阻抗,(2)内层共面特性阻抗,(3)外层共面差分阻抗,(4)内层共面差分阻抗.8 o1 m" V% {9 }& Y- P 三,再次给大家介绍一下芯板(即Core)及半固化片(即PP), 每个多层板都是由芯板和半固化片通过压合而成的,普通的FR-4板材一般有:生益,建滔,联茂等板材供应商.生益FR-4的芯板根据板厚来划分有:0.10MM ,0.15MM,,0.2MM ,,0.25MM.0.3MM,0.4MM,0.5MM 等,包括有H/HOZ,1/1OZ,等这里有一点需要大家特别注意:含两位小数的板厚是指不含铜的厚度,只有一位小数指包括铜的总厚度,例如:0.10MM 1/1OZ 的芯板,其0.10MM 是指介质的厚度,其总厚度应为0.10MM+0.035+0.035MM=0.17MM,再如:0.15MM 1/1OZ 的芯板,其总厚度是:0.15MM+0.035MM+0.035MM=0.22MM,而0.2MM 1/1OZ 的芯板,其总厚度就是0.2MM,它的介质厚度应为:0.2MM-0.035MM-0.035MM=0.13MM. 半固化片(即PP),一般包括:106,1080,2116,7628等,其厚度为:106为0.04MM,1080为0.06MM,2116为0.11MM,7628为0.19MM.当我们计算层叠结构时候通常需要把几张PP 叠在一起,例如:2116+106,其厚度为0.15MM,即6MIL;1080*2+7628,其厚度为0.31MM,即12.2MIL 等.但需注意以下几点:1,一般不允许4张或4张以上PP 叠放在一起,因为压合时容易产生滑板现象.2,7628的PP 一般不允许放在外层,因为7628表面比较粗糙,会影响板子的外观.3,另外3张1080也不允许放在外层,因为压合时也容易产生滑板现象." X7 R) e0 B% J" p, G 后续我会把一些常用的芯板以及各种组合的PP 厚度汇总给大家,以便学习用Polar 软件计算阻抗及层叠结构时使用!四, 怎样使用Polar Si9000软件计算阻抗: 首先应知道是特性阻抗还是差分阻抗,具体阻抗线在哪些信号层上,阻抗线的参考面是哪些层?其次根据文件选择正确的阻抗模型来计算阻抗,最后通过调整各层间的介质厚度,或者调整阻抗线的线宽及间距来满足阻抗及板厚的要求!五,举例说明怎样使用Polar Si9000计算阻抗及设计层叠结构:1.四层板板厚1.6MM,外层信号线要求控制50欧姆特性阻抗和100欧姆差分阻抗.其设计结构详见:4层板1.6MM 阻抗设计.jpg,其中H1代表的是信号层与参考层之间的介质厚度,即L1与L2之间的厚度为3.2MIL,Er1为板材的介电常数,FR-4通常为4.2-4.6,W1称为下线宽,W2称为上线宽,一般认为W1=W+0.5MIL,W2=W-0.5MIL,S1(注意S1<2W)为两根差分线之间的间距(指线边缘与线边缘之间距离),T1信号层的成品铜厚,外层1OZ=1.4MIL,而内层考虑的蚀刻的因素,我们通常认为内层1OZ=1.2MIL,而0.5OZ=0.6MIL 。

PCB线路板阻抗计算公式现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000来和大家说明下阻抗是怎么计算的。

在阻抗计算说明之前让我们先了解一下阻抗的由来和意义:传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:从此图可以推导出电报方程取传输线上的电压电流的正弦形式得推出通解定义出特性阻抗无耗线下r=0, g=0 得注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.叠层(stackup)的定义我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的Oz 的概念Oz 本来是重量的单位Oz(盎司 )= g(克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下介电常数(DK)的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:ε = Cx/Co = ε'-ε"Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示对照上面常用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度.在此假设板厚为,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线。

PCB线路板阻抗计算公式现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000来和大家说明下阻抗是怎么计算的。

在阻抗计算说明之前让我们先了解一下阻抗的由来和意义:传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:从此图可以推导出电报方程取传输线上的电压电流的正弦形式得推出通解定义出特性阻抗无耗线下r=0, g=0 得注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.叠层(stackup)的定义我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的Oz 的概念Oz 本来是重量的单位Oz(盎司)=28.3 g(克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下介电常数(DK)的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:ε = Cx/Co = ε'-ε"Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示对照上面常用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度.在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线。

阻抗控制計算目的: 學會使用Polar si9000對特殊信號線的阻抗計算舉例 :1. 差分信號線的阻抗計算以 E03為例,E03 USB2.0 D+ , D- 要求有90歐姆的阻抗匹配,依照此要求,計算出這兩條差分信號線在走線時的線寬和線間距.計算需準備的數據;板層的迭構方式, 各個板層之間的介質厚度,介質常數,銅箔厚度,阻抗控制的設計阻值.板層的迭構方式thickness Er UNIT:MIL SOLDER0.844 4.2TOP 1.0OZ 1.4PP8 4.2VCC 1.0OZ 1.4CORE6 4.2GND 1.0OZ 1.4PP8 4.2BOT 1.0OZ 1.4SOLDER0.844 4.2此差分信號走線是在BOT層,與他相鄰的一層就是GND層,所以我們在計算時用到數據是BOT與GND之間的數據.安裝好計算工具後,打開Polar si9000.依據下圖的設置來計算:2. G06 的GPS 傳輸線阻抗計算紅色走線部分需要做50 OHM 阻抗匹配板層結構thickness Er UNIT:MIL SOLDER0.8 3.8L1 (TOP)1.0OZ 1.4PP21166 4.6L2 (IN2)1.0OZ 1.4CORE6 4.2L3 (IN3)1.0OZ 1.4PP2116441.0OZ 1.42V8_RFDIGCORE44 L5 (IN5 VCC) 1.0OZ 1.4PP211644L6 (IN6) 1.0OZ 1.4CORE6 4.2L7 (IN7) 1.0OZ 1.4PP21166 4.6 L8 (BOT) 1.0OZ 1.4SOLDER0.8 3.8TOL:48.8在LAYOUT 中實際走線為L1(TOP) 層,其下對應的7層為GND即以 L2 層作為參考平面實際計算此傳輸線的線寬在計算工具中輸入參數F。

PCB线路板阻抗计算公式之宇文皓月创作现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000来和大家说明下阻抗是怎么计算的。

在阻抗计算说明之前让我们先了解一下阻抗的由来和意义:传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:从此图可以推导出电报方程取传输线上的电压电流的正弦形式得推出通解定义出特性阻抗无耗线下r=0, g=0 得注意,此特性阻抗和波阻抗的概念上的差别(具体检查平面波的波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗纷歧致所求出的电报方程的解纷歧致,就造成所谓的反射现象等等.在信号完整性领域里,比方反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.叠层(stackup)的定义我们来看如下一种stackup,主板经常使用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1,L2…L8)因此要计算的阻抗为L1,L4,L5,L8下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的Oz 的概念Oz 原本是重量的单位Oz(盎司 )=28.3 g(克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下介电常数(DK)的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:ε = Cx/Co = ε'ε"Prepreg/Core 的概念pp 是种介质资料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示对照上面经常使用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度.在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线。

阻抗计算公式

1、阻抗公式:z=r+j(xl–xc)。

2、阻抗z= r+j(xl –xc)。

其中r为电阻,xl

为感抗,xc为容抗。

如果(xl–xc)\ue 0,称为“感性负载”;反之,如果(xl –xc)\uc 0称为“容性负载”。

电感的感抗、电容的容抗三种类型的复物,复合后统称“阻抗”,写成数学公式。

阻抗(物理量):

在具备电阻、电感和电容的电路里,对电路中的电流拉艾的制约促进作用叫作电阻。

电阻常用z则表示,就是一个复数,实部称作电阻,虚部称作电抗,其中电容在电路中对

交流电拉艾的制约促进作用称作感抗,电感在电路中对交流电拉艾的制约促进作用称作容抗,电容和电感在电路中对交流电引发的制约促进作用总称作电抗。

电阻的单位就是欧姆。

电阻的概念不仅存有于电路中,在力学的振动系统中也存有牵涉。

电路中阻抗的计算公式在我们日常生活中,电无处不在,从家里亮堂堂的电灯,到手中便捷的手机,都离不开电的功劳。

而要深入理解电的世界,就不得不提到电路中的一个重要概念——阻抗。

阻抗,简单来说,就是对电流流动的阻碍作用。

它就像是电路中的“小拦路虎”,让电流不能随心所欲地乱跑。

那阻抗是怎么计算的呢?这可得好好说道说道。

在交流电路中,阻抗的计算公式是Z = √(R² + (Xₗ - Xc)²) 。

这里面的“Z”就代表阻抗,“R”表示电阻,“Xₗ”是感抗,“Xc”则是容抗。

先来说说电阻“R”。

电阻大家应该都比较熟悉,比如咱们平时用的电灯泡里就有电阻丝。

电阻的大小取决于导体的材料、长度、横截面积还有温度。

打个比方,就像不同粗细的水管,细水管对水流的阻碍就大,粗水管对水流的阻碍就小。

电阻也是这个道理,又细又长的导线电阻大,又粗又短的导线电阻小。

再讲讲感抗“Xₗ”。

感抗通常出现在有电感的电路中,像电感线圈啥的。

感抗的大小和交流电的频率以及电感的自感系数有关。

频率越高,感抗越大;自感系数越大,感抗也越大。

这就好比跑步的时候,频率快了,遇到的阻力也就大了。

然后是容抗“Xc”。

容抗常见于有电容的电路。

电容越大,交流电频率越低,容抗越小。

想象一下,电容就像是一个能储存电荷的小仓库,仓库越大,能装的电荷越多,对电流的阻碍就越小。

给大家分享一个我自己的经历吧。

有一次,我在家里修一个小音箱,怎么弄声音都不对劲,后来一检查,发现就是电路中的阻抗出了问题。

我拿着万用表,一点点测电阻、感抗和容抗,根据公式算来算去,终于找到了故障点。

原来是其中一个电感老化,感抗变小了,导致整个电路的阻抗失衡。

经过一番折腾,换了个新电感,音箱又欢快地响起来啦!在实际的电路设计和分析中,准确计算阻抗可是非常重要的。

如果阻抗计算不准确,可能会导致电路工作不正常,设备发热甚至损坏。

比如说,在设计手机充电器的时候,如果不考虑好阻抗,可能会让充电速度变慢,或者让充电器过热,甚至有可能会损坏手机电池。

阻抗计算公式、polarsi9000(教程)给初学者的⼀直有很多⼈问我阻抗怎么计算的. ⼈家问多了,我想给⼤家整理个材料,于⼰于⼈都是个⽅便.如果⼤家还有什么问题或者⽂档有什么错误,欢迎讨论与指教!在计算阻抗之前,我想很有必要理解这⼉阻抗的意义。

传输线阻抗的由来以及意义传输线阻抗是从电报⽅程推导出来(具体可以查询微波理论)如下图,其为平⾏双导线的分布参数等效电路: 从此图可以推导出电报⽅程取传输线上的电压电流的正弦形式得推出通解定义出特性阻抗⽆耗线下r=0, g=0 得注意,此特性阻抗和波阻抗的概念上的差异(具体查看平⾯波的波阻抗定义) 特性阻抗与波阻抗之间关系可从此关系式推出.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不⼀致所求出的电报⽅程的解不⼀致,就造成所谓的反射现象等等.在信号完整性领域⾥,⽐如反射,串扰,电源平⾯切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.叠层(stackup)的定义我们来看如下⼀种stackup,主板常⽤的8 层板(4 层power/ground 以及4 层⾛线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8 下⾯熟悉下在叠层⾥⾯的⼀些基本概念,和⼚家打交道经常会使⽤的Oz 的概念Oz 本来是重量的单位Oz(盎司)=28.3 g(克)在叠层⾥⾯是这么定义的,在⼀平⽅英尺的⾯积上铺⼀盎司的铜的厚度为1Oz,对应的单位如下介电常数(DK)的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺⼨的真空电容量Co之⽐为介电常数:ε = Cx/Co = ε'-ε" Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两⾯都覆有铜箔,⽽pp 没有.传输线特性阻抗的计算⾸先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,⽽带状线有2个参考地,如下图所⽰对照上⾯常⽤的8 层主板,只有top 和bottom ⾛线层才是微带线类型,其他的⾛线层都是带状线类型在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求⼀般是1~2mm,根据板厚要求来分层得到各厚度⾼度.在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来⾛线先来计算微带线的特性阻抗,由于top 层和bottom 层对称,只需要计算top 层阻抗就好的,采⽤polarsi6000,对应的计算图形如下: 在计算的时候注意的是:1,你所需要的是通过⾛线阻抗要求来计算出线宽W(⽬标)2,各⼚家的制程能⼒不⼀致,因此计算⽅法不⼀样,需要和⼚家进⾏确认3,表层采⽤coated microstrip 计算的原因是,⼚家会有覆绿漆,因⽽没⽤surface microstrip 计算,但是也有⼚家采⽤surface microstrip 来计算的,它是经过校准的4,w1 和w2 不⼀样的原因在于pcb 板制造过程中是从上到下⽽腐蚀,因此腐蚀出来有梯形的感觉(当然不完全是)5,在此没计算出精确的60Ohm 阻抗,原因是实际制程的时候⼚家会稍微改变参数,没必要那么精确,在1,2ohm 范围之内我是觉得没问题6,h/t 参数对应你可以参照叠层来看再计算出L5 的特性阻抗如下图记得当初有各版本对于stripline 还有symmetrical stripline 的计算图,实际上的差异从字⾯来理解就是symmetrical stripline 其实是offset stripline 的特例H1=H2在计算差分阻抗的时候和上⾯计算类似,除所需要的通过⾛线阻抗要求来计算出线宽的⽬标除线宽还有线距,在此不列出选⽤的图是在计算差分阻抗注意的是:1,在满⾜DDR2 clock 85Ohm~1394 110Ohm 差分阻抗的同时⼜满⾜其单端阻抗,因此我通常选择的是先满⾜差分阻抗(很多是电流模式取电压的)再考虑单端阻抗(通常板⼚是不考虑的,实际做很多板⼦,问题确实不算⼤,看样⼦差分线还是⾛线同层同via 同间距要求⼀定要符合)----------谨以此⽂怀念初学SI 的艰苦岁⽉特性阻抗公式 (含微带线,带状线的计算公式)a.微带线(microstrip) Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)] 其中,W为线宽,T为⾛线的铜⽪厚度,H为⾛线到参考平⾯的距离,Er是PCB板材质的介电常数(dielectric constant)。

阻抗值计算公式

阻抗是电路中的重要参数之一,它是指电路中电阻、电感和电容三者产生的总阻力。

阻抗值的计算需要根据电路的具体情况进行分析和计算。

一般来讲,电路中的阻抗可以使用如下公式来计算:

Z = R + j(XL – XC)

其中,Z为阻抗值,R为电阻值,XL为电感值,XC为电容值,j 为虚数单位。

当电路中只有电阻时,阻抗值计算公式为:

Z = R

当电路中只有电感时,阻抗值计算公式为:

Z = jXL

当电路中只有电容时,阻抗值计算公式为:

Z = -jXC

需要注意的是,电阻、电感和电容的单位分别为欧姆、亨利和法拉。

在实际计算中,需要将单位进行统一换算。

另外,对于串联电路和并联电路中的阻抗,可以使用对应的公式进行计算。

串联电路中的阻抗计算公式为:

Z = Z1 + Z2 + … + Zn

而并联电路中的阻抗计算公式为:

1/Z = 1/Z1 + 1/Z2 + … + 1/Zn

通过以上公式的应用,可以准确地计算出电路中的阻抗值,进而

为电路的设计和优化提供指导。

一直有很多人问我阻抗怎么计算的. 人家问多了,我想给大家整理个材料,于己于人都是个方便.如果大家还有什么问题或者文档有什么错误,欢迎讨论与指教!在计算阻抗之前,我想很有必要理解这儿阻抗的意义。

传输线阻抗的由来以及意义传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:从此图可以推导出电报方程取传输线上的电压电流的正弦形式得推出通解定义出特性阻抗无耗线下r=0, g=0 得注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.叠层(stackup)的定义我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的Oz 的概念Oz 本来是重量的单位Oz(盎司 )=28.3 g(克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下介电常数(DK)的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:ε = Cx/Co = ε'-ε"Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示对照上面常用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度. 在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线先来计算微带线的特性阻抗,由于top 层和bottom 层对称,只需要计算top 层阻抗就好的,采用polar si6000,对应的计算图形如下:在计算的时候注意的是:1,你所需要的是通过走线阻抗要求来计算出线宽W(目标)2,各厂家的制程能力不一致,因此计算方法不一样,需要和厂家进行确认3,表层采用coated microstrip 计算的原因是,厂家会有覆绿漆,因而没用surface microstrip 计算,但是也有厂家采用surface microstrip 来计算的,它是经过校准的4,w1 和w2 不一样的原因在于pcb 板制造过程中是从上到下而腐蚀,因此腐蚀出来有梯形的感觉(当然不完全是)5,在此没计算出精确的60Ohm 阻抗,原因是实际制程的时候厂家会稍微改变参数,没必要那么精确,在1,2ohm 范围之内我是觉得没问题6,h/t 参数对应你可以参照叠层来看再计算出L5 的特性阻抗如下图记得当初有各版本对于stripline 还有symmetrical stripline 的计算图,实际上的差异从字面来理解就是symmetrical stripline 其实是offset stripline 的特例H1=H2在计算差分阻抗的时候和上面计算类似,除所需要的通过走线阻抗要求来计算出线宽的目标除线宽还有线距,在此不列出选用的图是在计算差分阻抗注意的是:1,在满足DDR2 clock 85Ohm~1394 110Ohm 差分阻抗的同时又满足其单端阻抗,因此我通常选择的是先满足差分阻抗(很多是电流模式取电压的)再考虑单端阻抗(通常板厂是不考虑的,实际做很多板子,问题确实不算大,看样子差分线还是走线同层同via 同间距要求一定要符合)特性阻抗公式 (含微带线,带状线的计算公式)a.微带线(microstrip)Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)] 其中,W为线宽,T为走线的铜皮厚度,H为走线到参考平面的距离,Er是PCB板材质的介电常数(dielectric constant)。

此公式必须在0.1<(W/H)<2.0及1<(Er)<15的情况才能应用。

b.带状线(stripline)Z=[60/sqrt(Er)]ln{4H/[0.67π(0.8W+T)]} 其中,H为两参考平面的距离,并且走线位于两参考平面的中间。

此公式必须在W/H<0.35及T/H<0.25的情况才能应用差分阻抗的计算方法及公式The Differential Impedance Calculator is provided free to registered users.Please Register hereInstructions:1. Select the number of substrate layers required.2. You will then be presented with a table representing the suggested stack-up for that type of substrate.3. Modify the variables to examine the effects on the trace Characteristic and Differential Impedance.Important: The trace separation should not be adjusted to alter the Differential Impedance - trace separation should always be kept to the minimum clearance specified by the PCB vendor.Note:1.All dimensions are in MIL (thousands of an inch).2.The Dielectric Constant of FR4 material may vary by as much as 20%(4.2 to 5.2).3.The overall Dielectric Thickness (Cu to Cu) should total 62 MILnominally.4.Variables unavailable for modification have no significant effecton the impedance of the traces.5.The default multilayer board stack-ups are taken from AdvanceDesign for SMT, Barry Olney/AMC.6.The Impedance Calculator uses formulae derived from:IPC-D-317 - Design Standard for Electronic Packaging Utilizing High Speed Techniques.EMC & the Printed Circuit Board - Montrose.7.Only Edge Coupled Differential Pairs are considered. No allowancehas been made for Broad Side Coupling from adjacent layers. It is goodpractice to route adjacent layers orthogonal to each other in order toreduce any coupling that may occur.8. To reduce EMI, high frequency, fast rise time signals should be routedbetween the reference planes.All care has been taken to ensure that the results are correct but noresponsibility is taken for any errors.If you prefer to do the calculations yourself - please use the formulae below.whereW = trace widthT = trace thicknessH = distance to nearest reference planeEr = dielectric constantD = trace edge to edge spacingC = signal layer separationB = reference plane separationRelative Dielectric Constants of substrate materials PCB阻抗设计详解1、前言随着科技发展, 尤其在积体电路的材料之进步,使运算速度有显著提升, 促使积体电路走向高密度﹑小体积, 单一零件, 这些都导致今日及未來的印刷电路板走向高频响应, 高速率数位电路之运用, 也就是必須控制线路的阻抗﹑低失真﹑低干扰及低串音及消除电磁干扰EMI。

阻抗设计在PCB设计中显得越来越重要。

作为PCB制造前端的制前部,负责阻抗的模拟计算,阻抗条的设计。

客户对阻抗控制要求越来越严,而阻抗管控数目也原来越多,如何快速,准确地进行阻抗设计,是制前人员非常关注的一个问题。

2、阻抗主要类型及影响因素阻抗(Zo)定义:对流经其中已知频率之交流电流所产生的总阻力称为阻抗(Zo)。

对印刷电路板而言,是指在高频讯号之下,某一线路层(signal layer)对其最接近的相关层(reference plane)总合之阻抗。