华南理工大学数字电子技术试卷精华版全集

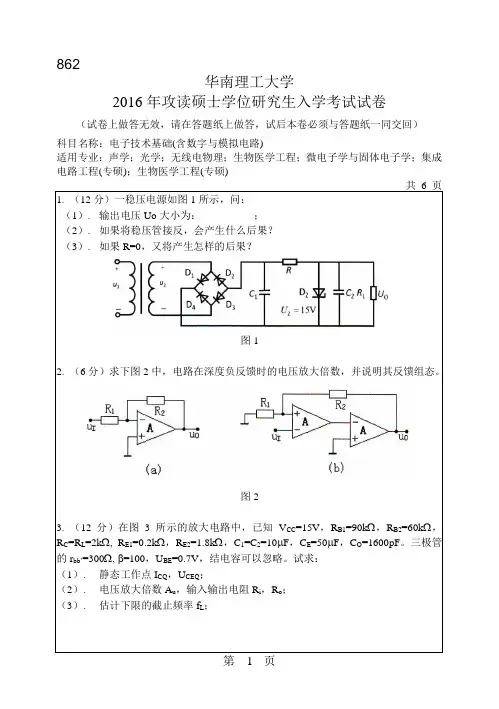

- 格式:doc

- 大小:2.61 MB

- 文档页数:38

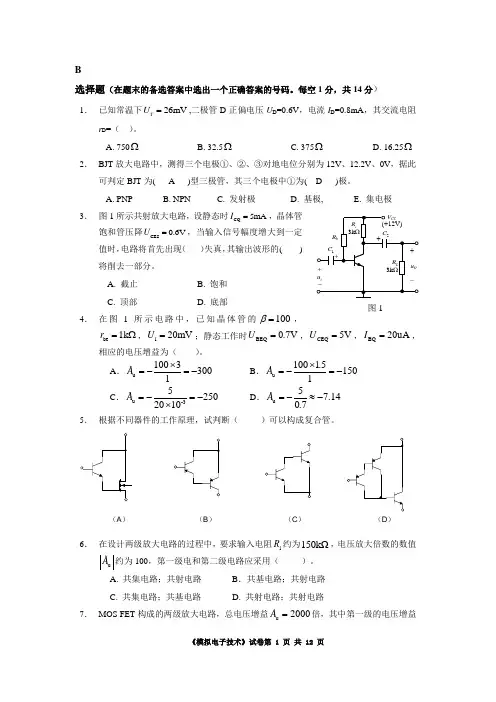

B选择题(在题末的备选答案中选出一个正确答案的号码。

每空1分,共14分)1. 已知常温下26mV T U =,二极管D 正偏电压U D =0.6V ,电流I D =0.8mA ,其交流电阻r D =( )。

A. 750ΩB. 32.5ΩC. 375ΩD. 16.25Ω 2. BJT 放大电路中,测得三个电极①、②、③对地电位分别为12V 、12.2V 、0V ,据此可判定BJT 为( A )型三极管,其三个电极中①为( D )极。

A. PNPB. NPNC. 发射极D. 基极,E. 集电极 3. 图1所示共射放大电路,设静态时CQ 5mA I =,晶体管饱和管压降CES 0.6V U =,当输入信号幅度增大到一定值时,电路将首先出现( )失真,其输出波形的( )将削去一部分。

A. 截止B. 饱和C. 顶部D. 底部4. 在图1所示电路中,已知晶体管的100β=,be 1k r =Ω,i 20mV U =;静态工作时BEQ 0.7V U =,CEQ 5V U =,BQ 20uA I =,相应的电压增益为( )。

A .u 10033001A ⨯=-=- B .u 1001.51501A ⨯=-=- C .u -352502010A =-=-⨯D .u 57.140.7A =-≈-5. 根据不同器件的工作原理,试判断( )可以构成复合管。

(A)(B)(C)(D )6. 在设计两级放大电路的过程中,要求输入电阻i R 约为150k Ω,电压放大倍数的数值u A 约为100,第一级电和第二级电路应采用( )。

A. 共集电路;共射电路 B .共基电路;共射电路C. 共集电路;共基电路D. 共射电路;共射电路7. MOS FET 构成的两级放大电路,总电压增益u 2000A =倍,其中第一级的电压增益为20倍,则第二级的电压增益为( )。

A .10dBB. 20dBC. 40dBD.100dB8. 对于单管共射放大电路,若其上、下限频率分别为H f 、L f ,当L f f =时,oU 滞后iU ( )。

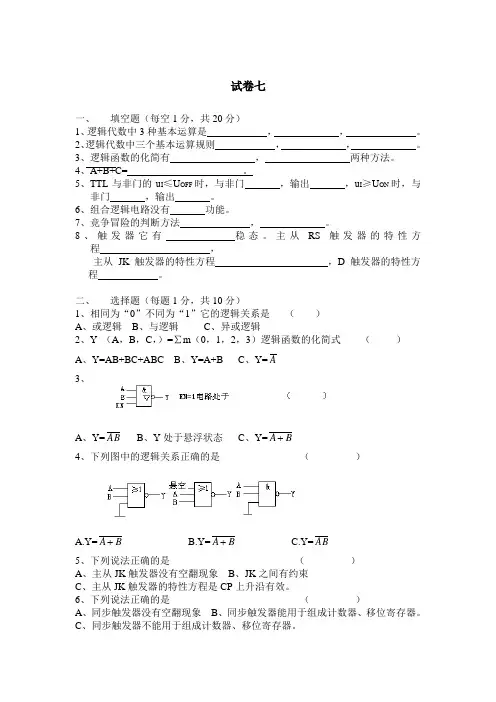

试卷七一、 填空题(每空1分,共20分) 1、逻辑代数中3种基本运算是 , , 。

2、逻辑代数中三个基本运算规则 , , 。

3、逻辑函数的化简有 , 两种方法。

4、A+B+C= 。

5、TTL 与非门的u I ≤U OFF 时,与非门 ,输出 ,u I ≥U ON 时,与非门 ,输出 。

6、组合逻辑电路没有 功能。

7、竞争冒险的判断方法 , 。

8、触发器它有 稳态。

主从RS 触发器的特性方程 ,主从JK 触发器的特性方程 ,D 触发器的特性方程 。

二、 选择题(每题1分,共10分)1、相同为“0”不同为“1”它的逻辑关系是 ( ) A 、或逻辑 B 、与逻辑 C 、异或逻辑2、Y (A ,B ,C ,)=∑m (0,1,2,3)逻辑函数的化简式 ( ) A 、Y=AB+BC+ABC B 、Y=A+B C 、Y=A3、A 、Y=AB B 、Y 处于悬浮状态C 、Y=B A +4、下列图中的逻辑关系正确的是 ( )A.Y=B A +B.Y=B A +C.Y=AB5、下列说法正确的是 ( ) A 、主从JK 触发器没有空翻现象 B 、JK 之间有约束 C 、主从JK 触发器的特性方程是CP 上升沿有效。

6、下列说法正确的是 ( )A 、同步触发器没有空翻现象B 、同步触发器能用于组成计数器、移位寄存器。

C 、同步触发器不能用于组成计数器、移位寄存器。

7、下列说法是正确的是()A、异步计数器的计数脉冲只加到部分触发器上B、异步计数器的计数脉冲同时加到所有触发器上C、异步计数器不需要计数脉冲的控制8、下列说法是正确的是()A、施密特触发器的回差电压ΔU=U T+-U T-B、施密特触发器的回差电压越大,电路的抗干扰能力越弱C、施密特触发器的回差电压越小,电路的抗干扰能力越强9、下列说法正确的是()A、多谐振荡器有两个稳态B、多谐振荡器有一个稳态和一个暂稳态C、多谐振荡器有两个暂稳态10、下列说法正确的是()A、555定时器在工作时清零端应接高电平B、555定时器在工作时清零端应接低电平C、555定时器没有清零端三、判断题(每题1分,共10分)1、A+AB=A+B ()2、当输入9个信号时,需要3位的二进制代码输出。

华南理工大学数必考题型————————————————————————————————作者:————————————————————————————————日期:一、填空(每空1分,计20分)1、计数器按增减趋势分有、和计数器。

2、TTL与非门输入级由组成。

两个OC门输出端直接接在一起称为。

3、在TTL与非门,异或门,集电级开路门,三态门中,为实现线与逻辑功能应选用,要有推拉式输出级,又要能驱动总线应选用门。

4、一个触发器可以存放位二进制数。

5、优先编码器的编码输出为码,如编码输出A2A1A0=011,可知对输入的进行编码。

6、逻辑函数的四种表示方法是、、、。

7、移位寄存器的移位方式有,和。

8、同步RS触发器中,R,S为电平有效,基本RS触发器中R,S 为电平有效。

9、常见的脉冲产生电路有二.判断题:(每题1分,共10分)1、对于JK触发器J=K=1时,输出翻转。

()2、一个存储单元可存1位2进制数。

()3、同一CP控制各触发器的计数器称为异步计数器。

()4、对MOS门电路多余端不可以悬空。

()5、函数式F=ABC+AB C+A B C= (3、5、6、7)()6、JK触发器的输入端J悬空,相当于J=1。

()7、时序电路的输出状态仅与此刻输入变量有关。

()8、一个触发器能存放一位二进制数。

()9、计数器随CP到来计数增加的称加计数器。

()10、数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

()三、选择题(每题1分,共10分)1、对于MOS门电路,多余端不允许()A、悬空B、与有用端并联C、接电源D、接低电平2、右图①表示()电路,②图表示()电路A、与门B、或门C、非门D、与非门3、卡诺图③、④表示的逻辑函数最简式分别为()和()A、F=B+DB、F=B+DC 、F=BD+BD D 、F=BD+BD4、逻辑电路如图⑤,函数式为( )A 、 F=AB +C B 、 F=A B +C C 、F=AB +CD 、F=A+B C5、一位8421B C D 码计数器至少需要 个触发器。

华南理工大学期末考试模拟电子技术基础试卷及答案一、填空(25分)1.二极管最主要的特性是 。

2.三极管是 控制型器件,而场效应管是 控制型器件。

3.射极输出器具有______________恒小于1、接近于1,______________ 和__________同相,并具有_____________高和_______________低的特点。

5.如果变压器二次(即副边)电压的有效值为_______V ,桥式整流后(不滤波)的输出电压为_________V ,经过电容滤波后为________V 二极管所承受的最大反向电压为 V 。

6、在门电路中,最基本的三种门电路是 门 门和 门。

7.时序逻辑电路按照其触发器是否有统一的时钟控制分为 时序电路和 时序电路。

二、单项选择题 (每小题 2分,总共20分)1.在某放大电路中,测的三极管三个电极的静态电位分别为,则这只三极管是( )。

A .NPN 型硅管 B.NPN 型锗管 C.PNP 型硅管 D.PNP 型锗管2.某场效应管的转移特性如图所示,该管为( )。

A .P 沟道增强型MOS 管 B 、P 沟道结型场效应管 C 、N 沟道增强型MOS 管 D 、N 沟道耗尽型MOS 管3.通用型集成运放的输入级采用差动放大电路,这是因为它的( )。

A .输入电阻高 B.输出电阻低 C.共模抑制比大 D.电压放大倍数大 4.与甲类功率放大方式相比,乙类互补对称功放的主要优点是( )。

A .不用输出变压器B .不用输出端大电容C .效率高D .无交越失真 5.稳压二极管稳压时,其工作在( ),发光二极管发光时,其工作在( )。

A .正向导通区 B .反向截止区 C .反向击穿区 6. 图示逻辑电路的逻辑式为( )。

(a) F =A B +A B(b) F =AB AB +(c) F =AB +A B8. 逻辑代数又称为 代数。

最基本的逻辑关系有 、 、 三种。

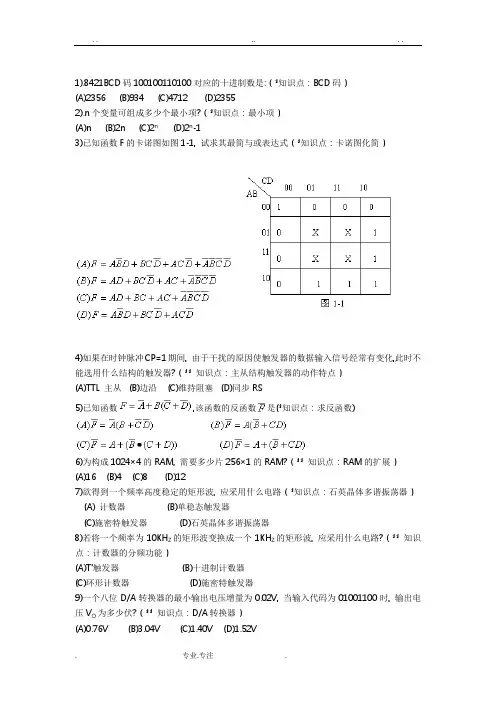

1).8421BCD码100100110100对应的十进制数是:(*知识点:BCD码)(A)2356 (B)934 (C)4712 (D)23552).n个变量可组成多少个最小项?(*知识点:最小项)(A)n (B)2n (C)2n (D)2n-13)已知函数F的卡诺图如图1-1, 试求其最简与或表达式(*知识点:卡诺图化简)4)如果在时钟脉冲CP=1期间, 由于干扰的原因使触发器的数据输入信号经常有变化,此时不能选用什么结构的触发器?(** 知识点:主从结构触发器的动作特点)(A)TTL 主从(B)边沿(C)维持阻塞(D)同步RS5)已知函数,该函数的反函数是(*知识点:求反函数)6)为构成1024×4的RAM, 需要多少片256×1的RAM?(** 知识点:RAM的扩展)(A)16 (B)4 (C)8 (D)127)欲得到一个频率高度稳定的矩形波, 应采用什么电路(*知识点:石英晶体多谐振荡器)(A) 计数器(B)单稳态触发器(C)施密特触发器(D)石英晶体多谐振荡器8)若将一个频率为10KH Z的矩形波变换成一个1KH Z的矩形波, 应采用什么电路?(** 知识点:计数器的分频功能)(A)T'触发器 (B)十进制计数器(C)环形计数器(D)施密特触发器9)一个八位D/A转换器的最小输出电压增量为0.02V, 当输入代码为01001100时, 输出电压V O为多少伏?(** 知识点:D/A转换器)(A)0.76V (B)3.04V (C)1.40V (D)1.52V10) 对于TTL门电路来说,下列各图哪个是正确的?( *** 知识点:TTL门电路)二.分析题.1.逻辑电路及输入端CP、D的波形如图2-1, 设Q0=Q1=Q2=0(10分)(** 知识点:移位寄存器)(1)试画出在CP、D作用下,输出端Q0、Q1、Q2的波形;(2)说明电路的逻辑功能.2.由555定时器构成的单稳态电路如图2-2, 试回答下列问题(15分)(**** 知识点:555定时器)(1)该电路的暂稳态持续时间two=?(2)根据two的值确定图2-2中, 哪个适合作为电路的输入触发信号, 并画出与其相应的V C和V O波形.三.设计题:1.已知函数, 试用以下几种组件实现电路(15分)(*** 知识点:用MSI进行组合逻辑电路的设计)(1)八选一数据选择器(2)四线-十六线译码器和多输入端与非门.2。

《数字电子技术基础》复习提纲重点● 基本概念、基本方法、分析和解决问题的能力。

● 器件掌握外特性。

● SSI 记住各种表达方法。

● MSI 题目给出功能表或表达式及逻辑框图。

第一章 逻辑代数基础1.1 要求1、二、十六进制及其与十进制的相互转换。

2、8421码、BCD 的编码方法;了解其它常用的编码方法。

3、逻辑运算的特点、逻辑代数的基本定律与定理;会写反演式、对偶式、与非-与非式、或非-或非式等。

4、逻辑问题的各种描述方法:真值表、逻辑式、逻辑符号等。

5、逻辑代数的公式化简法,卡诺图化简法;最小项、无关项及其应用。

1.2 例题1、与(1000 0111)8421BCD 相等的二进制数是, 十六进制数是57,十进制数是87。

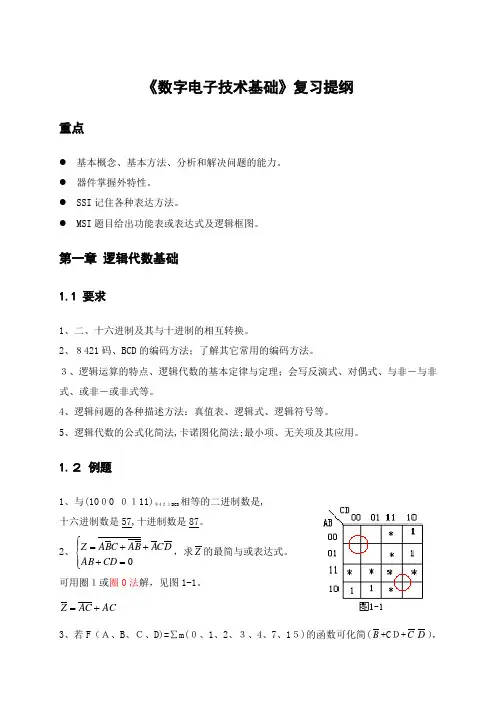

2、⎪⎩⎪⎨⎧=+++=0CD AB D C A B A C B A Z ,求Z 的最简与或表达式。

可用圈1或圈0法解,见图1-1。

AC C A Z +=3、若F (A、B 、C、D)=∑m(0、1、2、3、4、7、15)的函数可化简(B +C D+C D ),则可能存在的约束项为(C),见图1-2。

A.0=+DACA B.0=+BAACC.0=+BACA/0=+BADA D.0=+CBBA1.3习题P37 一、二、三、四、七、八、九、1.10、1.11。

第二章门电路2.1 要求(集成电路内部只作定性分析,不作定量计算)1、掌握正逻辑和负逻辑的概念。

2、掌握各种门电路的功能和各种表示方法。

3、了解TTL和CMOS门电路的使用特点。

4、若干电参数的物理意义。

V OH 、VOL、VIH、VIL、VTH、VNH、VNL、IIH、IIL、IOH、IOL、N、tpd1、某电路在正逻辑下的表达式是B A C Y +=, 在负逻辑下的表达式是(B A AC +),可列真值表,将0变1、1变0得到。

见表2-1 负逻辑式:C B AC Y +=- 反函数式:C B C A Y += 比较两式可知不同之处。

数字电子技术基础试卷及答案8套(共29页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--数字电子技术基础1一.1.(15分)试根据图示输入信号波形分别画出各电路相应的输出信号波形L1、L2、L3、L4、和L5。

设各触发器初态为“0”。

AB二.(15分)已知由八选一数据选择器组成的逻辑电路如下所示。

试按步骤分析该电路在M1、M2取不同值时(M1、M2取值情况如下表所示)输出F的逻辑表达式。

八选一数据选择器输出端逻辑表达式为:Y=Σm i D i,其中m i是S2S1S0最小项。

FM2M1 F0 00 1111三.(8分)试按步骤设计一个组合逻辑电路,实现语句“A>B”,A、B均为两位二进制数,即A (A1、A0),B(B1、B0)。

要求用三个3输入端与门和一个或门实现。

四.(12分)试按步骤用74LS138和门电路产生如下多输出逻辑函数。

23123Y AC Y ABC ABC BC Y BC ABC=⎧⎪=++⎨⎪=+⎩ 74LS138逻辑表达式和逻辑符号如下所示。

五.(15分)已知同步计数器的时序波形如下图所示。

试用维持-阻塞型D 触发器实现该计数器。

要求按步骤设计。

六.(18分)按步骤完成下列两题1.分析图5-1所示电路的逻辑功能:写出驱动方程,列出状态转换表,画出完全状态转换图和时序波形,说明电路能否自启动。

2.分析图5-2所示的计数器在M=0和M=1时各为几进制计数器,并画出状态转换图。

图5-14BCCPAEpE T LDDQ0Q1 Q3Q2 74LS163 Rd1M&1计数脉冲1图5-2七.八.(10分) 电路下如图所示,按要求完成下列问题。

1.指出虚线框T1中所示电路名称.2.对应画出V C、V01、A、B、C的波形。

并计算出V01波形的周期T=。

56数字电子技术基础2一.(20分)电路如图所示,晶体管的β=100,Vbe=。

(1)求电路的静态工作点;(2) 画出微变等效电路图, 求Au 、r i 和r o ;(3)若电容Ce 开路,则将引起电路的哪些动态参数发生变化?并定性说明变化趋势.二.(15分)求图示电路中a U 、bU 、b U 、c U 及L I 。

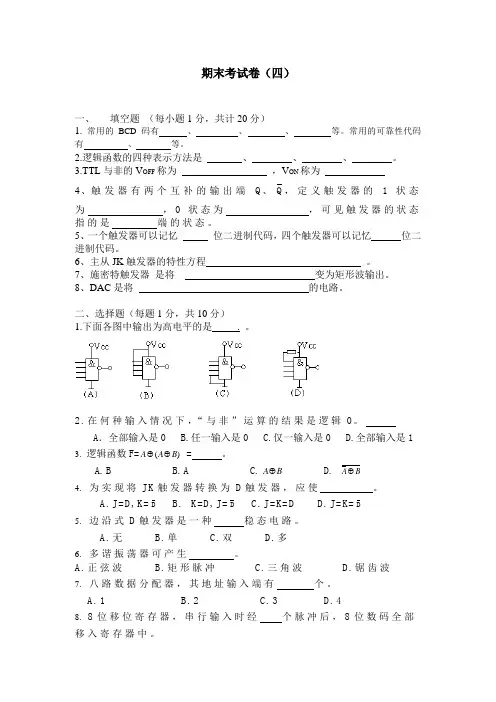

期末考试卷(四)一、填空题(每小题1分,共计20分)1.常用的BCD码有、、、等。

常用的可靠性代码有、等。

2.逻辑函数的四种表示方法是、、、。

3.TTL与非的V OFF称为,V ON称为4、触发器有两个互补的输出端Q、Q,定义触发器的1状态为,0状态为,可见触发器的状态指的是端的状态。

5、一个触发器可以记忆位二进制代码,四个触发器可以记忆位二进制代码。

6、主从JK触发器的特性方程。

7、施密特触发器是将变为矩形波输出。

8、DAC是将的电路。

二、选择题(每题1分,共10分)1.下面各图中输出为高电平的是.。

2.在何种输入情况下,“与非”运算的结果是逻辑0。

A.全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是1 3.逻辑函数F=)⊕ = 。

A⊕(BAA.BB.AC.BA⊕A⊕ D.B4.为实现将J K触发器转换为D触发器,应使。

A.J=D,K=DB. K=D,J=DC.J=K=DD.J=K=D5.边沿式D触发器是一种稳态电路。

A.无B.单C.双D.多6.多谐振荡器可产生。

A.正弦波B.矩形脉冲C.三角波D.锯齿波7.八路数据分配器,其地址输入端有个。

A.1B.2C.3D.48.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.89、一位8421B CD码计数器至少需要个触发器。

A.3B.4C.5D.1010、一个16选1多路选择器输入地址有A、2位B、3位C、4位D、8位三、判断题(每题1分,共10分)1. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

()2.格雷码具有任何相邻码只有一位码元不同的特性。

()3. 若两个函数具有相同的真值表,则两个逻辑函数必然相等。

()。

4. 三态门的三种状态分别为:高电平、低电平、不高不低的电压。

()5. 一般TTL门电路的输出端可以直接相连,实现线与。

()6. D触发器的特性方程为Q n+1=D,与Q n无关,所以它没有记忆功能。

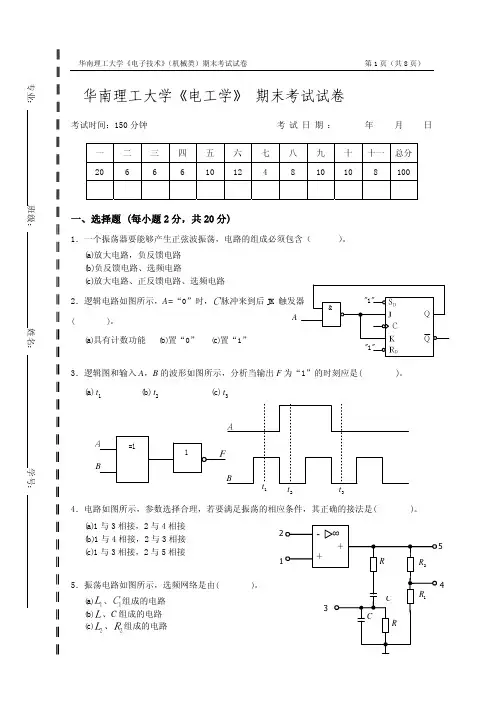

华南理工大学《电工与电子技术》考试试卷第1页(共8页)专业:班级:姓名:学号:华南理工大学期末考试试卷《电工与电子技术》(化工类)考试时间:150分钟考试日期:年月日一二三四五六七八九十十一十二总分12 8 8 10 8 10 86 10 87 5 100一.选择题(每小题2分,共12分)1、图示电路中,供出功率的电源是()。

(a)理想电压源(b)理想电流源 (c)理想电压源与理想电流源U4VS2、图示电路正处于谐振状态,闭合S后,电流表A的读数将()。

(a)增大(b)减小(c)不变S3、图示电路在稳定状态下闭合开关S,该电路()。

(a)不产生过渡过程,因为换路未引起L的电流发生变化(b)要产生过渡过程,因为电路发生换路(c)要发生过渡过程,因为电路有储能元件且发生换路2R4、运行中的三相异步电动机,当负载增大且不超过额定负载时,其转速将()。

(a)增加(b)不变(c)稍微减小5、所示电路中,二极管D为理想元件,设u i=10sinωt V,稳压管D Z的稳定电压为5V,正向压降不计,则输出电压uO的波形为图2中()。

华南理工大学《电工电子技术》考试试卷 第2页(共8页)图15图2ttOD(a)(b)(c)6、电路如图所示,当R L 的值由大变小时,I L 将( )。

(a)变大 (b)变小 (c)不变二、图示电路中,已知:U S =15V ,I S1=3A ,I S2=2A ,R 1=3Ω,R 2=8Ω,R 3=4Ω,R 4=12Ω,R 5=2Ω。

用戴维宁定理求电流I 。

(8分)U BS1华南理工大学《电工与电子技术》考试试卷 第3页(共8页)专业:班级: 姓名: 学号:三、如图所示的正弦交流电路中,电源频率为50Hz ,L =0.138H ,电流有效值I C =2A , I R =1.414A ,电路功率因数cos ϕ=1。

试求R 和C 。

(8分)Li LC专业: 班级: 姓名:华南理工大学《电工电子技术》考试试卷 第4页(共8页)四、线电压U l =220V 的对称三相电源上接有两组对称三相负载,一组是接成三角形的感性负载,每相功率为4.84kW ,功率因数cos ϕ=0.8;另一组是接成星形的电阻负载,每相阻值为10Ω,如图所示。

华南理工大学《电子技术》(机械类)期末考试试卷考试时间:150分钟考试日期: 年 月 日 一二三四五六七八九十十一 总分20 6 6 6 10 12 4 8 10 10 8 100一、选择题 (每小题2分,共20分)1.一个振荡器要能够产生正弦波振荡,电路的组成必须包含( )。

(a)放大电路,负反馈电路 (b)负反馈电路、选频电路(c)放大电路、正反馈电路、选频电路2.逻辑电路如图所示,A=“0”时,C 脉冲来到后JK( )。

(a)具有计数功能 (b)置“0” (c)置“1”3.逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

(a) t 1 (b) t 2 (c) t 3t 1t 2t 31=1ABFAB4.电路如图所示,参数选择合理,若要满足振荡的相应条件,其正确的接法是( )。

(a)1与3相接,2与4相接 (b)1与4相接,2与3相接 (c)1与3相接,2与5相接5.振荡电路如图所示,选频网络是由( )。

(a)L 1、C 1组成的电路 (b)L 、C 组成的电路 (c)L 2、R 2组成的电路214专业: 班级: 姓名: 学号:ACC6.在运算放大器电路中,引入深度负反馈的目的之一是使运放()。

(a)工作在线性区,降低稳定性(b)工作在非线性区,提高稳定性(c)工作在线性区,提高稳定性7.比较器电路如图1所示,其传输特性为图2中()。

(a)(b)(c)图28.具有发射极电阻R E的典型差动放大电路中,R E的电流负反馈作用对()有效。

(a)差模输入信号(b)共模输入信号(c)共模和差模两种输入信号9.电路如图所示,二极管为同一型号的理想元件,电阻R =4k Ω,电位u=1V ,u =3V ,则电位u F 等于( )。

(a)1V (b)3V (c)12V10.编码器的逻辑功能是( )。

(a)把某种二进制代码转换成某种输出状态 (b)将某种状态转换成相应的二进制代码 (c)把二进制数转换成十进制数二、(6分)单相桥式整流电路如图所示,已知u t 2362=sin (ωV),二极管为理想元件,从示波器上观察到u O 的波形如图所示。

华南理工大学期末考试《 模拟电子技术 》试卷A (电类07级,2009.07.06)一、选择题(在题末的备选答案中选出一个正确答案的号码。

每小题2分,共14分) 1. 电路如图1所示,二极管的导通电压0.7V D U =,则图1中二极管的工作状态及输出电压值为( )。

A.D1导通,D2截止,0.7V OU = B.D1截止,D2导通, 5.3V O U =- C.D1截止,D2截止,12V O U = D.D1导通,D2导通,0.7V OU =2. 图2管压降当输入信号幅度增大到一定值时,电路将首先出现( )失真,其输出波形的( )将削去一部分。

A. 饱和;底部B. 饱和;顶部C. 截止;底部D. 截止;顶部3. 在图2所示电路中,已知UT =26mV ,静态时2mA CQ I =,晶体管参数:100β=,bb'200r =Ω,正弦交流输入电压i t u ω=,则交流输出o u 为( )。

A .o )u t ωπ=+B .o )u t ω=C.o )u t ωπ=+D4. 根据不同器件的工作原理,可判断下图中()可以构成复合管。

(A )(B )(C )(D )5. 对于RC 耦合单管共射放大电路,若其上、下限频率分别为H f 、L f ,则当L f f=时,下列描述正确的是( )。

AiU B .o U 滞后iU ︒135 C.o U 超前i U ︒45D .o U 超前iU 135︒6. 某负反馈放大电路,其开环增益9.9mS iu A =,反馈系数10ui F k =Ω,开环输入电阻图15.0i R K '=Ω,可推算出其闭环输入电阻ifR '=( )。

A. 500k Ω;B. 50; C.50; D. 5Ω7. 如下图4所示单相桥式整流、电容滤波电路,电容量足够大时,已知副边电压有效值为210V U =,测得输出电压的平均值() 4.5V O AV U =,则下列描述正确的是( )。

数电期末考试题及答案华工一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是()。

A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑答案:A2. 下列哪个不是数字电路的优点?()A. 高速度B. 低功耗C. 易于集成D. 体积大答案:D3. 在以下触发器中,具有记忆功能的触发器是()。

A. 与非门B. 或非门C. D触发器D. 异或门答案:C4. 一个完整的数字系统通常由以下哪两个部分组成?()A. 模拟部分和数字部分B. 硬件部分和软件部分C. 输入部分和输出部分D. 运算部分和存储部分答案:B5. 以下哪个不是数字电路设计中常用的工具?()A. 逻辑仿真软件B. 波形发生器C. 模拟示波器D. 电阻测试仪答案:D...(此处省略其他选择题及答案)二、填空题(每题2分,共20分)1. 一个四位二进制计数器可以计数到______。

答案:152. 一个典型的数字电路设计流程包括逻辑设计、______、测试和验证。

答案:电路实现3. 在数字电路中,______是最基本的逻辑单元。

答案:逻辑门4. 一个简单的加法器可以完成二进制数的______和加法运算。

答案:加5. 一个时钟周期包括上升沿和______。

答案:下降沿...(此处省略其他填空题及答案)三、简答题(每题10分,共30分)1. 简述数字电路与模拟电路的区别。

答案:数字电路与模拟电路的主要区别在于信号的形式和处理方式。

数字电路处理的是离散的数字信号,通常只有两个状态,如二进制的0和1,而模拟电路处理的是连续变化的模拟信号,可以有无限多的状态。

数字电路具有更高的抗干扰能力,且易于集成和大规模生产,而模拟电路则在信号处理和放大方面有其优势。

2. 解释什么是时序逻辑电路,并给出一个例子。

答案:时序逻辑电路是一种包含存储元件的数字电路,其输出不仅取决于当前的输入,还取决于电路的历史状态。

例如,一个简单的触发器就是一个时序逻辑电路,它可以存储一个位的信息,并根据输入信号改变其状态。

诚信应考 ,考试作弊将带来严重后果!华南理工大学期末考试《 数字电子技术 》试卷 A注意事项:1. 考前请将密封线内填写清楚;2. 所有答案请直接答在试卷上 ( 或答题纸上 3 .考试形式 : 闭卷;4. 本试卷共 四 大题,满分 100 分, 考试时间 120 分钟 。

题号一二三四总分得分评卷人B. 000100101000 D.1001010002.已知函数 F 的卡诺图如图 1-1, 试求其最简与 或表达式,其BC .D .4.对于 TTL 数字集成电路来说,下列说法那个是错误的:(A ) 电源电压极性不得接反,其额定值为 5V ; (B ) 不使用的输入端接 1;(C ) 输入端可串接电阻,但电阻值不应太大;A.10000000 C.100000001.十进制数 128的 8421BCD 码是3. 已知函数的反演式为 原函数为( )。

A .(D)OC 门输出端可以并接。

5.欲将正弦信号转换成与之频率相同的脉冲信号,应用A.T ,触发器B. 施密特触发器C.A/D 转换器D. 移位寄存器6.下列A/D 转换器中转换速度最快的是( )。

A. 并联比较型B.双积分型C.计数型D.逐次渐近型7.一个含有32768个存储单元的ROM,有8个数据输出端,其地址输入端有() 个。

A. 10B. 11C. 12D. 88.如图1-2,在TTL 门组成的电路中,与非门的输入电流为I iL≤–1mA?I iH≤20μ A。

G1 输出低电平时输出电流的最大值为I OL(max)=10mA,输出高电平时最大输出电流为I OH(max)=–0.4mA 。

门G1 的扇出系数是(A. 1B. 4C. 5D. 109.十数制数2006.375 转换为二进制数是:A. 11111010110.011B. 1101011111.11C. 11111010110.11D. 1101011111.01110.T TL 或非门多余输入端的处理是:A. 悬空B. 接高电平C. 接低电平D.接”1” 二.填空题(每小题2分,共20分)1.CMOS 传输门的静态功耗非常小,当输入信号的频率增加时,其功耗将_______ 。

1).8421BCD码对应的十进制数是:(*知识点:BCD码)(A)2356 (B)934 (C)4712 (D)23552).n个变量可组成多少个最小项(*知识点:最小项)(A)n (B)2n (C)2n (D)2n-13)已知函数F的卡诺图如图1-1, 试求其最简与或表达式(*知识点:卡诺图化简)4)如果在时钟脉冲CP=1期间, 由于干扰的原因使触发器的数据输入信号经常有变化,此时不能选用什么结构的触发器(** 知识点:主从结构触发器的动作特点)(A)TTL 主从 (B)边沿 (C)维持阻塞 (D)同步RS5)已知函数,该函数的反函数是(*知识点:求反函数)6)为构成1024×4的RAM, 需要多少片256×1的RAM(** 知识点:RAM的扩展)(A)16 (B)4 (C)8 (D)127)欲得到一个频率高度稳定的矩形波, 应采用什么电路(*知识点:石英晶体多谐振荡器)(A) 计数器 (B)单稳态触发器(C)施密特触发器 (D)石英晶体多谐振荡器8)若将一个频率为10KH Z的矩形波变换成一个1KH Z的矩形波, 应采用什么电路(** 知识点:计数器的分频功能)(A)T'触发器(B)十进制计数器(C)环形计数器 (D)施密特触发器9)一个八位D/A转换器的最小输出电压增量为, 当输入代码为01001100时, 输出电压V O为多少伏(** 知识点:D/A转换器)(A) (B) (C) (D)10) 对于TTL门电路来说,下列各图哪个是正确的( *** 知识点:TTL门电路)二.分析题.1.逻辑电路及输入端CP、D的波形如图2-1, 设Q0=Q1=Q2=0(10分)(** 知识点:移位寄存器)(1)试画出在CP、D作用下,输出端Q0、Q1、Q2的波形;(2)说明电路的逻辑功能.2.由555定时器构成的单稳态电路如图2-2, 试回答下列问题(15分)(**** 知识点:555定时器)(1)该电路的暂稳态持续时间two=(2)根据two的值确定图2-2中, 哪个适合作为电路的输入触发信号, 并画出与其相应的V C和V O波形.555定时器功能表4脚6脚2脚3脚7脚0××0导通1>2/3V CC>1/3V CC0导通1<2/3V CC>1/3V CC不变不变1<2/3V CC<1/3V CC1截止1>2/3V CC<1/3V CC1截止三.设计题:1.已知函数, 试用以下几种组件实现电路(15分)(*** 知识点:用MSI进行组合逻辑电路的设计)(1)八选一数据选择器(2)四线-十六线译码器和多输入端与非门.2。

试用JK触发器设计一个同步时序逻辑电路, 其状态转换表如表3-1. 要求画出卡诺图,求状态方程、驱动方程、画出逻辑电路图.(15分) (**** 知识点:同步时序电路的设计)Q2n Q1nX 0 1Q2n+1 Q1n+10 01 10 1 1 0 10 00 10 01 11 00 00 1题号1 2 34 5 6 78 910答案B C C A B A D B D B1).8421BCD码对应的十进制数是: (*知识点:BCD码)(A)2356 (B)934 (C)4712 (D)23552).n个变量可组成多少个最小项(*知识点:最小项)(A)n (B)2n (C)2n (D)2n-13)已知函数F的卡诺图如图1-1, 试求其最简与或表达式(*知识点:卡诺图化简)4)如果在时钟脉冲CP=1期间, 由于干扰的原因使触发器的数据输入信号经常有变化,此时不能选用什么结构的触发器(**知识点:主从结构触发器的动作特点)(A)TTL 主从 (B)边沿 (C)维持阻塞 (D)同步RS5)已知函数,该函数的反函数是(*知识点:求反函数)6)为构成1024×4的RAM, 需要多少片256×1的RAM (**知识点:RAM的扩展)(A)16 (B)4 (C)8 (D)127)欲得到一个频率高度稳定的矩形波, 应采用什么电路(*知识点:石英晶体多谐振荡器)(A) 计数器 (B)单稳态触发器(C)施密特触发器 (D)石英晶体多谐振荡器8)若将一个频率为10KH Z的矩形波变换成一个1KH Z的矩形波, 应采用什么电路(**知识点:计数器的分频功能)(A)T'触发器(B)十进制计数器(C)环形计数器 (D)施密特触发器9)一个八位D/A转换器的最小输出电压增量为, 当输入代码为01001100时, 输出电压V O为多少伏(**知识点:D/A转换器)(A) (B) (C) (D)10)对于TTL门电路来说,下列各图哪个是正确的 (*** 知识点:TTL门电路)二.分析题.1.逻辑电路及输入端CP、D的波形如图2-1, 设Q0=Q1=Q2=0(10分)(** 知识点:移位寄存器)(1)试画出在CP、D作用下,输出端Q0、Q1、Q2的波形;(2)说明电路的逻辑功能.答案:(1) (2)右移移位寄存器2.由555定时器构成的单稳态电路如图2-2, 试回答下列问题(15分)(**** 知识点: 555定时器)(1)该电路的暂稳态持续时间two=(2)根据two的值确定图2-2中, 哪个适合作为电路的输入触发信号, 并画出与其相应的V C和V O波形.555定时器功能表4脚6脚2脚3脚7脚0××0导通1>2/3V CC>1/3V CC0导通1<2/3V CC>1/3V CC不变不变1<2/3V CC<1/3V CC1截止1>2/3V CC<1/3V CC1截止答案(1)two==μs(2)Vi2适合作为单稳态电路的输入触发脉冲三.设计题:1.已知函数, 试用以下几种组件实现电路(15分)(*** 知识点:用MSI进行组合逻辑电路的设计)(1)八选一数据选择器(2)四线-十六线译码器和多输入端与非门.答案: (1)令A2=A A1=B A0=C,则D7=D6=D5=D3=1, D4=D2=D1=D0=0(2)2.试用JK触发器设计一个同步时序电路, 其状态转换如表3-1. 要求画出卡诺图,求状态方程、驱动方程,画出逻辑电路图.(15分)(**** 知识点:同步时序电路的设计)表3-1Q2n Q1nX 0 1Q2n+1 Q1n+10 01 10 1 1 0 10 00 10 01 11 00 00 1答案:卡诺图: 状态方程:DC B AD C A B ++驱动方程:逻辑电路图:数字电子技术试卷(注:红色部分为答案)一、填空(20分)1. 数制转换:(8F)16 = ( 143 )10= ( )2 = ( 217 )8。

(3EC)H = ( 1004 )D ,(2003) D = ()B = ( 3723)O 。

2. 有一数码,作为自然二进制数时,它相当于十进制数 147 ,作为8421BCD 码时,它相当于十进制数 93 。

3. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =4. 如果对键盘上108个符号进行二进制编码,则至少要 7 位二进制数码。

5. 在TTL 门电路的一个输入端与地之间接一个10K 电阻,则相当于在该输入端输入 高 电平;在CMOS 门电路的输入端与电源之间接一个1K 电阻,相当于在该输入端输入 高 电平。

6.TTL 电路的电源电压为 5 V , CMOS 电路的电源电压为 3—18 V 。

7. 74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为 。

8. 一个10位地址码、8位输出的ROM ,其存储容量为 8K 或213 。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有 11 根地址线,有 16 根数据读出线。

10 .能够实现“线与”的TTL 门电路叫 OC 门 ,能够实现“线与”的CMOS 门电路叫 OD 门。

二、完成以下要求。

(8分) 1. 要实现Y=A+B 的逻辑关系,请正确连接多余端。

(a )多余端接电源或与A 或B 接在一起 (b )多余端接地或与A 或B 接在一起2. 写出下图的逻辑表达式。

三、用代数法将下列函数化简为最简与或表达式。

(9分) 1. ;C B BD ABC D BC ABD D ABC Y +++++=2= BA B 5VYA B 5VY&(a)(b)A B EN Y&=CCB AC B A C B A Y ⋅⋅++++⋅⋅=12.. n n Q K Q J K J Y ++=3= 3. = 1四、用卡诺图法化简函数,写出它们的最简与或表达式。

(9分) 1.D C B ABC C AB C B A Y +++=1;Y 1= 3.()()∑=9,8,5,2,0,,,2m D C B A Y ,约束条件AB +BC =0;Y2= 4.()()∑∑+=15,014,13,11,9,8,5,33d m Y . = 五、请根据题图和题表, 完成以下要求: (7分)1、按表1栏的要求, 图中完善F1~F5的逻辑符号,并按图中的逻辑符号将F6~F7的名称填入相应位置;2、表2栏中填入各输出端的逻辑表达式;3、ABCD = 1001,将各输出值填入表3栏中。

六、用四选一数据选择器74LS153设计一个3变量的多数表决电路。

(10分)nQK K J ++=D C C B AB ++DB AC A BD ++CDB ABCD C B C B A +++AB C D&1 =1 =11&1 C A B过程略七、用集成二进制译码器74LS138和与非门构成全加器。

(10分)八、请画出题图电路的Q 0、Q 1的输出波形,假设初始状态皆为0。

(8分) (过程略)九、分析用集成十进制同步可逆计数器CT74LS192组成的下列计数器分别是几进制计数器。

CT74LS192的CR 为异步清零端(高电平有效),LD 为异步置数控制端(低电平有效),CP U 、CP D 为加、减计数脉冲输入端(不用端接高电平),CO 和BO 分别为进位和借位输出端。

(8分)Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7A 0 A 1 A 2ST BST CST A& &1 C i-1 B i A iS i C i1CPACPA Q 01JC11K1JC11KQ 0 Q 1 1(a) (b)(a )为6进制加计数器; (b )为23进制加计数器十、写出由ROM 所实现的逻辑函数的表达式。