AD9854对照翻译

- 格式:docx

- 大小:1.05 MB

- 文档页数:45

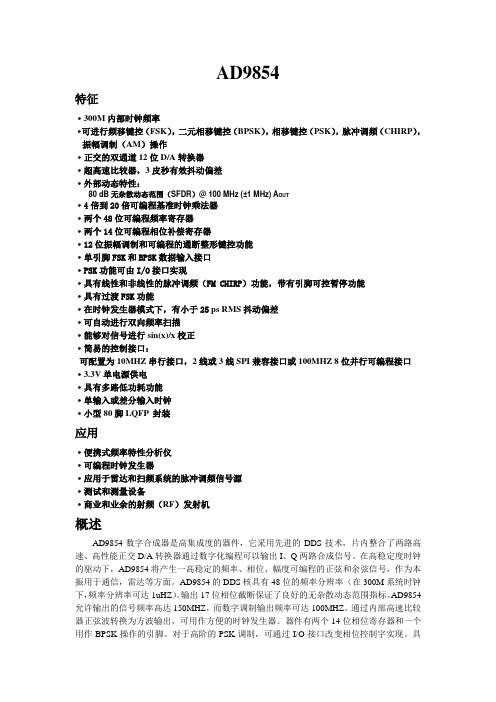

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

AD9854/52 Rev E Evaluation Board InstructionsMarch 04, 2003Introduction:The AD9854/52 Rev E evaluation board includes either an AD9854ASQ or AD9852ASQ IC.The ASQ package permits 300 MHz operation by virtue of its thermally enhanced design. This package has a bottom-side heat “slug” that must be soldered to the ground plane of the PCB directly beneath the IC. In this manner, the evaluation board, PCB ground plane layer extracts heat from the AD9854/52 IC package. If device operation is limited to 200 MHz and below, the AST package without a heat “slug” may be used in customer installations over the full temperature range. The AST package is less expensive than the ASQ package and those costs are reflected in the price of the IC.Evaluation boards for both the AD9854 and AD9852 are identical except for the installed IC.The AD9852 or AD9854 data sheet is essential to understand all of their modes of operation. While various Preliminary data sheets have been prepared and disseminated only the released data sheet should be used since errors and omissions in the preliminary data sheets are inevitable. A released data sheet will have no Preliminary markings and will display a revision status such as “REV 0” or “REV A” at the lower left corner of each page.To assist in proper placement of the pin-header shorting-jumpers, the instructions on page 2 will refer to direction (left, right, top, bottom) as well as header pins to be shorted. Pin #1 for each three pin-header has been marked on the PCB corresponding with the schematic diagram. When following these instructions, position the PCB so that the PCB text can be read from left to right. The board is shipped with the pin-headers configuring the board as follows:1) REFCLK for the AD9854/52 is configured as differential. The differentialclock signals are provided by the MC100LVEL16D differential receiver.2) Input clock for the MC100LVEL16D is single-ended via J25. This signal maybe 3.3VCMOS or a 2V p-p sine wave capable of driving 50 ohms (R13).3) Both DAC outputs from the AD9854/52 are routed through the two 120 MHzelliptical LP filters and their outputs connected to J7 (Q) and J6 (I).4) The board is setup for software control via the printer port connector.5) The DAC’s output currents are configured for 10 mA.General operating Instructions:Load the Version 1.72 software from the provided CD onto your PC’s hard disk. Connect a printer cable from the PC to the AD9854 Evaluation Board printer port connector labeled “J11”. Version 1.72 software will support Windows 95, Windows 98, Windows Me, Windows NT, Windows 2000 or Windows Xp.Hardware Preparation: Using the schematic in conjunction with these instructions will be helpful in acquainting the user with the electrical functioning of the evaluation board.Attach power wires to connector labeled “TB1” using the screw-down terminals. This is a plastic connector that press-fits over a 4-pin header soldered to the board. Table below shows connections to each pin. DUT = “device under test”AVDD +3.3V for all DUT analog pins DVDD +3.3Vfor all DUTdigital pinsVCC +3.3Vfor all otherdevicesGround – forall devicesAttach REFCLK to clock input, J25.Clock input, J25. This is actually a single-ended input that will be routed to the MC100LVEL16D for conversion to differential PECL output. This is accomplished by attaching a 2V p-p clock or sine wave source to J25. Note that this is a 50-Ohm impedance point set by R13. The input signal will be ac-coupled and then biased to the center-switching threshold of the MC100LVEL16D. To engage the differential-clocking mode of the AD9854 W3 pins 2 & 3 (the bottom two pins) must be connected with a shorting jumper.The signal arriving at the AD9854 is called the Reference Clock. If you choose to engage the on-chip PLL clock multiplier, then this signal is the reference clock for the PLL and the multiplied PLL output becomes the SYSTEM CLOCK. If you choose to bypass the PLL clock multiplier, the reference clock that you have supplied is directly operating the AD9854 and is therefore the system clock.Tri-state control or switch headers W9,W11, W12, W13, W14 and W15 must be shorted to allow the provided software to control the AD9854 evaluation board via the printer port connector J11.If programming of the AD9854 is not to be provided by the users PC and ADI software then headers W9, W11, W12, W13, W14 and W15 should be opened (shorting jumpers removed). This effectively detaches the PC interface and allows the 40-pin header, J10, and J1 to assume control without bus contention. Input signals on J10 and J1 going to the AD9854 should be 3.3V CMOS logic levels.Low pass filter testing. The purpose of 2-pin headers W7 and W10 (associated with J4 and J5) are to allow the two 50-ohm 120 MHz filters to be tested during PCB assembly without interference from other circuitry attached to the filter inputs. Normally, a shorting jumper will be attached to each header to allow the DAC signals to be routed to the filters. If the user wishes to test the filters, the shorting jumpers at W7 and W10 should be removed and 50-Ohm test signals applied at J4 and J5 inputs to the 50-ohm elliptic filters. User should refer to the provided schematic and the following sections to properly position the remaining shorting jumpers. Observing the unfiltered Iout1and the unfiltered Iout2 DAC signals. This allows the viewer to observe the unfiltered DAC outputs at J5 (the “I” signal) and J4 (the “Q” or Control DAC signal). The procedure below simply routes the two 50-ohm terminated analog DAC outputs to the SMB connectors and disconnects any other circuitry. The “raw” DAC outputs may appear as a series of quantized (stepped) output levels that may not resemble a sine wave until they have been filtered. The default 10 mA output current will develop a 0.5 volts p-p signal across the on-board 50-Ohm termination. If your “observation” equipment offers 50-Ohm inputs, then the DAC will develop only 0.25 volts p-p due to the double termination.1. Install shorting jumpers at W7 and W10.2. Remove shorting jumper at W163. Remove shorting jumper from 3-pin header W1.4. Install shorting jumper on pins 1 & 2 (bottom two pins) of 3-pin header W4If using the AD9852 evaluation board, Iout2, the Control DAC output is under user control through the serial or parallel ports. 12-bit, 2’s-complement value(s) is/are written to the Q-DAC register that will set the Iout2 output to a static dc level. Allowable hexadecimal values are 7FF (maximum) to 800 (minimum) with all 0’s being mid-scale. Rapidly changing the contents of the Q-DAC register (up to 100 MSPS) allows Iout2 to assume any waveform that can be programmed.Observing the filtered Iout1and the filtered Iout2. This allows viewer to observe the filtered “I“ & “Q” (or Control) DAC outputs at J6 (the “I” signal) and J7 (the “Q” or Control signal). This places the 50–ohm (input and output Z) low pass filters in the “I” and “Q” (or Control) DAC pathways to remove images and aliased harmonics and other spurious signals above approximately 120 MHz. For “I” & “Q” signals, these signals will appear as nearly pure sine waves and 90 degrees out-of-phase with each other. These filters are designed with the assumption that the system clock speed is at or near maximum (300 MHz). If you system clock speed is much less than 300 MHz, for example 200 MHz, then it is possible or inevitable that unwanted DAC products other than the fundamental signal will be passed by the low pass filters. If you are using the AD9852 evaluation board then any reference to the “Q” signal should be interpreted to mean “Control DAC”.1. Install shorting jumpers at W7 and W102. Install shorting jumper at W163. Install shorting jumper on pins 1 & 2 (bottom two pins) of 3-pin header W14. Install shorting jumper on pins 1 & 2 (bottom two pins) of 3-pin header W45. Install shorting jumper on pins 2 & 3 (bottom two pins) of 3-pin header W2 and W8Observing the filtered Iout1 and the filtered Iout1B. This allows viewer to observe only the filtered “I” DAC outputs at J6 (the “true” signal) and J7 (the “complementary” signal). This places the 120 MHz low pass filters in the true and complementary outputs paths of the “I” DAC to remove images and aliased harmonics and other spurious signals above approximately 120 MHz. These signals will appear as nearly pure sine waves and 180 degrees out-of-phase with each other. ). If you system clock speed is much less than 300 MHz, for example 200 MHz, then it is possible or inevitable that unwanted DAC products other than the fundamental signal will be passed by the low pass filters.1. Install shorting jumpers at W7 and W102. Install shorting jumper at W163. Install shorting jumper on pins 2 & 3 (top two pins) of 3-pin header W14. Install shorting jumper on pins 2 & 3 (top two pins) of 3-pin header W45. Install shorting jumpers on pins 2 & 3 (bottom two pins) of 3-pin header W2 and W8To connect the high-speed comparator to the DAC output signals you can choose either the quadrature filtered output configuration (AD9854 only) or the complementary filtered output configuration outlined above (both AD9854 and AD9852). Follow steps 1 through 4 for either filtered configuration as above. Step 5 below will re-route the filtered signals away from their output connectors (J6 and J7) and to the 100-Ohm configured comparator inputs. This sets-upthe comparator for differential input without control of the comparator output duty cycle.The comparator output duty cycle should be close to 50% in this configuration.5. Install shorting jumper on pins 1 & 2 (top two pins) of 3-pin header W2 and W8User may elect to change the Rset resistor, R2 from 3.9k ohms to 1.95k ohms to get a more robust signal at the comparator inputs. This will decrease jitter and extend comparator-operating range. User can accomplish this by installing a shorting jumper at W6, which provides a second 3.9k chip resistor (R20) in parallel with the provided R2. This boosts the DAC output current from 10 mA to 20 mA and doubles the p-p output voltage developed across the loadsTo connect the high-speed comparator in a single-ended configuration that will allow duty cycle or pulse width control requires that a dc threshold voltage be present at one of the comparator inputs. You may supply this voltage using the “Q-DAC or Control DAC” by configuring it as a control DAC in software. A 12-bit, 2’s-complement value is written to the Q-DAC registerthat will set the Iout2 output to a static dc level. Allowable hexadecimal values are 7FF (maximum) to 800 (minimum) with all 0’s being mid-scale. The Iout1 channel will continue to output a filtered sine wave programmed by user. These two signals are routed to the comparator using W2 and W8 3-pin header switches. You must be in the configuration described in the section “Observing the filtered Iout1 and the filtered Iout2”. Follow steps 1 through 4 in that section and then the following:5. Install shorting jumper on pins 1 & 2 (top two pins) of 3-pin header W2 and W8The user may elect to change the Rset resistor, R2 from 3.9k ohms to 1.95k ohms to get a more robust signal at the comparator inputs. This will decrease jitter and extend comparator-operating range. User can accomplish this by installing a shorting jumper at W6, which provides a second 3.9k chip resistor (R20) in parallel with the provided R2.Using the provided software:The software is provided on a CD. If your circumstances require 3.5 inch disks, contact the applications engineer via email (david.brandon@) to obtain disks. This brief set of instructions should be used in conjunction with the AD9854 or AD9852 data sheet and the AD9854/52 Evaluation Board schematic.Version 1.72 Software has been improved from previous versions in the following ways: * Now works with all Windows Operating Systems except Windows NT 3.5The CD-ROM contains the following* The AD9852/54 Evaluation Software.* The latest AD9852 and AD9854 datasheets.* The DDS Tutorial* Installers for all supported Windows Operating Systems* Evaluation Board Schematics* Evaluation Board PCB Layout Gerber FilesSeveral numerical entries, such as frequency and phase information, et al, require that the ENTER key by pressed to register that information. So, for example, if you input a new frequency and hit the load button and nothing new happens, it is probably because you forgot to press the enter key after typing the new frequency information.1) Normal operation of the AD9854/52 evaluation board begins with a master reset. Many ofthe default register values after reset are depicted in the software “control panel”. The reset command sets the DDS output amplitude to minimum and 0 Hz, 0 phase-offset as well as other states that are listed in the AD9854/52 Register Layout table in the data sheet.2) The next programming block should be the “Reference Clock & Multiplier” since thisinformation is used to determine the proper 48-bit frequency tuning words that will be entered and calculated later.3) The output amplitude defaults to the 12-bit straight binary multiplier values of the “I” and “Q”multiplier registers of 000hex and no output should be seen from the DAC’s. Set both multiplier amplitudes in the Output Amplitude window to a substantial value, such as FFFhex. You may bypass the digital multiplier by clicking the box “Output Amplitude is always Full-Scale” but experience has shown that doing so does not result in best SFDR. Best SFDR, as much as 11 dB better, is obtained by routing the signal through the digital multiplier and “backing off” on the multiplier amplitude. For instance, FC0 hex produces lessspurious signal amplitude than FFF hex. It’s an exploitable and repeatable phenomenon that should be investigated in your application if SFDR (spurious-free dynamic range) must be maximized. This phenomenon is more readily observed at higher output frequencies where good SFDR becomes more difficult to achieve.4) The user of this evaluation board is assumed to be a technically orientated person with basicknowledge of DDS, familiar with binary mathematics and digital / analog / RF electronics. The user should be able to “play” with the software from this point and learn how to operate the evaluation board intuitively. Refer to the datasheet and evaluation board schematic to understand all the functions of the AD9854/52 available to the user and to gain an understanding of what the software is doing in response to your commands. The AD9854 and AD9852 final data sheets will become available the first week of November 1999.In the event that you encounter difficulty, contact the applications engineer, david.brandon@, for help.End of instructions.。

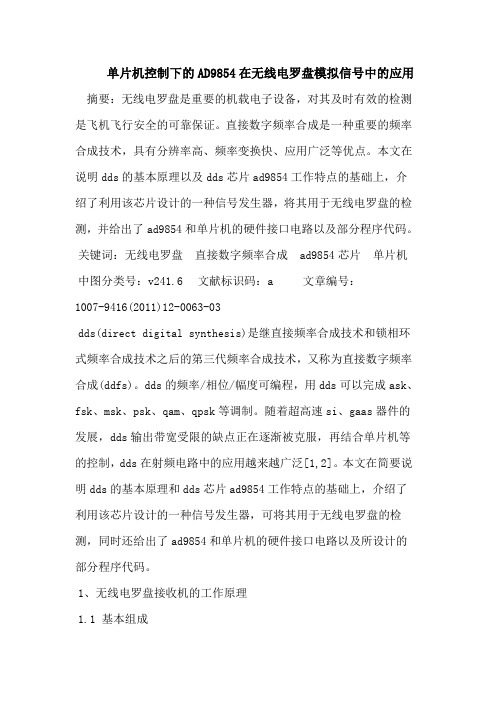

单片机控制下的AD9854在无线电罗盘模拟信号中的应用摘要:无线电罗盘是重要的机载电子设备,对其及时有效的检测是飞机飞行安全的可靠保证。

直接数字频率合成是一种重要的频率合成技术,具有分辨率高、频率变换快、应用广泛等优点。

本文在说明dds的基本原理以及dds芯片ad9854工作特点的基础上,介绍了利用该芯片设计的一种信号发生器,将其用于无线电罗盘的检测,并给出了ad9854和单片机的硬件接口电路以及部分程序代码。

关键词:无线电罗盘直接数字频率合成 ad9854芯片单片机中图分类号:v241.6 文献标识码:a 文章编号:1007-9416(2011)12-0063-03dds(direct digital synthesis)是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术,又称为直接数字频率合成(ddfs)。

dds的频率/相位/幅度可编程,用dds可以完成ask、fsk、msk、psk、qam、qpsk等调制。

随着超高速si、gaas器件的发展,dds输出带宽受限的缺点正在逐渐被克服,再结合单片机等的控制,dds在射频电路中的应用越来越广泛[1,2]。

本文在简要说明dds的基本原理和dds芯片ad9854工作特点的基础上,介绍了利用该芯片设计的一种信号发生器,可将其用于无线电罗盘的检测,同时还给出了ad9854和单片机的硬件接口电路以及所设计的部分程序代码。

1、无线电罗盘接收机的工作原理1.1 基本组成无线电罗盘由接收机、控制箱、环形天线、均衡器、罗差补偿器、连接电缆、垂直天线及指示器等部分组成[3]。

1.2 主要功用无线电罗盘的主要功用是自动定向。

与其他设备配合,可以测出偏流角,求出风向、风速等航行数据;在能见度不好时,还可以与无线电高度表、信标接收机等配合,进行仪表着陆等。

1.3 定向原理1.3.1 环形天线的方向性当环形天线的环面对准电波来向,即电波的交变磁通不穿过环面时,它就没有感应电势输出;当环面偏离电波来向,即电波的交变磁通部穿过环面时,它就产生感应电势输出,而且偏左与偏右时其感应电势的相位相反。

AD9854芯片资料一、芯片特征:AD9854拥有300MHZ内部时钟频率,可以进行FSK、BPSK、PSK、chirp、AM等的操作,双综合12bit数模转换器,超高速,3ps rms 抖动比较,它还有出色的动态性能,4到20倍可编程时钟乘法器,双48bit可编程频率寄存器,双14比特可编程相位寄存器,12bit可编程调幅以及输出开/关键控功能,单管脚FSK、BPSK数据接口,PSK可输入/输出接口,具有单管脚频率保持功能的线性或者非线性脉冲等一些优良特征。

AD9854数字合成器是一个利用DDS技术、两个内部高速高性能正交DACs 控制数字可编程输入输出的综合器件。

当给AD9854加上一个确定时钟时,它可以生成高度稳定、频率-相位-幅度可编程的sine或者cosine输出,这些特点可以被用于灵敏的LO以及雷达和其他一些应用。

AD9854具有创新意义的高速DDS 核心提供48bit的频率分辨率。

保持17bit确保了SFDR性能优良。

AD9854的电路结构允许同步正交输出信号的频率最高达到150MHZ。

而且这些信号的数字调频可以最高达到每秒1亿次。

正弦波输出可以转换成正交波,而这要通过内部比较器来实现,这种转换主要应用于灵敏时钟生成。

AD9854提供两个14bit的相位寄存器和一个单脚用于BPSK控制。

对于高阶PSK操作,I/O接口可以用于相位变换。

拥有两个DDS结构的12bit的I和Q DACs提供出色的宽带和窄带输出SFDR。

如果正交功能功能不适宜,那么Q DAC也可以配置成一个用户可编程的控制DAC。

当配置比较器的时候,12bit的控制DAC使高速时钟生成器应用中的静态循环控制更加便利。

两个12bit的数字乘法器允许可编程的幅度调制、开/关输出键控以及精确的正交输出幅度控制。

为了使宽带宽频全面应用更加方便,AD9854采用了脉冲功能控制。

AD9854的内部可编程4倍到20倍REFCLK乘法器电路生成300MHZ 的系统时钟,而时钟源是来自于一个外部低频时钟。

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

DDS模块设计DDS模块的设计是本系统的重点,也是本章阐述的重点。

DDS模块主要是围绕芯片AD9852进行设计的,设计要求既要满足性能指标,还要求优化电路,减小电路面积,否则13路DDS共同存在会使系统体积显得较大。

下面先介绍AD9852的基本特性。

4.2.1 AD9852介绍式参考时钟输入D更新读信号写信号行选择复位源地比较器输入模拟信号输出模拟信号输出比较器输出图4-2 AD9852功能结构框图chart4-2 AD9852 function and structure如图4-2所示,AD9852内部包括一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300MHz DAC,一个高速模拟比较器以及接口逻辑电路。

其主要性能特点如下:1.高达300MHz的系统时钟;2.能输出一般调制信号,FSK,BPSK,PSK,CHIRP,AM等;3.100MHz时具有80dB的信噪比;4.内部有4*到20*的可编程时钟倍频器;5.两个48位频率控制字寄存器,能够实现很高的频率分辨率。

6.两个14位相位偏置寄存器,提供初始相位设置。

7.带有100MHz的8位并行数据传输口或10MHz的串行数据传输口。

AD9852的芯片封装图如下:图4-3 AD9852芯片封装图chart4-3 AD9852 chip encapsulationAD9852有40个程序寄存器,对AD9852的控制就是对这些程序寄存器写数据实现的。

表4-1 AD9852并行接口寄存器功能并行地址寄存器功能默认值0x00 0x01 相位寄存器#1<13:8>(15,14位无效)相位寄存器#1<7:0>0x000x000x02 0x03 相位寄存器#2<13:8>(15,14位无效)相位寄存器#2<7:0>0x000x000x04 0x05 0x06 0x07 0x08 0x09 频率转换字#1<47:40>频率转换字#1<39:32>频率转换字#1<31:24>频率转换字#1<23:16>频率转换字#1<15:8>频率转换字#1<7:0>0x000x000x000x000x000x000x0A 频率转换字#1<47:40> 0x00表4-2 AD9852控制寄存器功能通过并行总线将数据写入程序寄存器时,实际上只是暂存在I/O缓冲区中,只有提供更新信号,这些数据才会更新到程序寄存器。

FEATURES300 MHz internal clock rateFSK, BPSK, PSK, chirp, AM operationDual integrated 12-bit digital-to-analog converters (DACs) Ultrahigh speed comparator, 3 ps rms jitterExcellent dynamic performance80 dB SFDR at 100 MHz (±1 MHz) AOUT4× to 20× programmable reference clock multiplierDual 48-bit programmable frequency registersDual 14-bit programmable phase offset registers12-bit programmable amplitude modulation andon/off output shaped keying functionSingle-pin FSK and BPSK data interfacesPSK capability via input/output interfaceLinear or nonlinear FM chirp functions with single-pin frequency hold functionFrequency-ramped FSK<25 ps rms total jitter in clock generator mode特征300 MHz内部时钟速率支持FSK, BPSK, PSK, chirp, AM调制集成双路12位数/模转换器(DAC)超高速比较器,3个PS RMS抖动出色的动态性能80dB的SFDR在100 MHz(±1 MHz)的AOUT4 ×20×可编程参考时钟倍频器双48位可编程频率寄存器双通道,14位可编程相位偏移寄存器12位可编程振幅调制ON / OFF输出形键控功能单引脚FSK和BPSK的数据接口通过输入/输出接口实现PSK功能单线实现线性或非线性的调频功能频率暂停功能频率ramped的FSK<25 ps的均方根时钟发生器模式的总抖动Automatic bidirectional frequency sweepingSin(x)/x correctionSimplified control interfaces10 MHz serial 2- or 3-wire SPI compatible100 MHz parallel 8-bit programming3.3 V single supplyMultiple power-down functionsSingle-ended or differential input reference clockSmall, 80-lead LQFP or TQFP with exposed padAPPLICATIONSAgile, quadrature LO frequency synthesisProgrammable clock generatorsFM chirp source for radar and scanning systemsTest and measurement equipmentCommercial and amateur RF exciters双向自动扫频sin(x)/ x修正简化的控制接口兼容10 MHz串行2 或3线SPI总线100兆赫并行8位总线3.3 V单电源供电多重省电功能参考时钟可单端或差分输入小型,80引脚LQFP或带有散热焊盘的TQFP封装应用正交LO频率合成可编程时钟发生器调频雷达和扫描系统的线性调频源测试与测量设备商业及业余射频发射器目录特点................................................. .............................................一应用................................................. ......................................一功能框图............................................... ...............一修订历史................................................ ...............................三一般描述................................................ . (4)规格................................................. (5)绝对最大额定值............................................... . (8)热阻................................................ . (8)测验等级说明.............................................. . (8)防静电提示................................................ . (8)引脚配置和功能说明 (9)典型性能特征 (12)典型应用................................................ .. (16)操作原理............................................... .. (19)操作模式............................................... .. (19)使用AD9854 ............................................... (29)内部和外部更新时钟 (29)ON / OFF输出形键控(侨丰) (29)I和Q数模转换器.............................................. .. (30)控制DAC ................................................ . (30)逆Sinc函数............................................... .. (31)REFCLK乘法器 (31)编程AD9854 ............................................... . (32)主复位................................................ (32)并行I / O操作............................................. (34)串行端口I / O操作............................................ .. (34)一般操作的串行接口 (36)指令字节................................................ .. (37)串行接口引脚说明 (37)串口操作的注意事项............................................. (37)的MSB / LSB的转移.............................................. (38)控制寄存器的说明............................................... .. (38)功耗和散热考虑 (40)热阻抗................................................ . (40)结温事项 (40)评价工作条件 (41)热增强型封装安装指南 (41)评估板................................................ . (42)评估板说明............................................... (42)一般操作说明 (42)使用提供的软件.............................................. (44)支持................................................. (44)外形尺寸................................................ .. (52)订购指南................................................ .. (52)GENERAL DESCRIPTIONThe AD9854 digital synthesizer is a highly integrated device that uses advanced DDS technology, coupled with two internal high speed, high performance quadrature DACs to form a digitally programmable I and Q synthesizer function. When referenced to an accurate clock source, the AD9854 generates highly stable, frequency-phase, amplitude-programmable sine and cosine outputs that can be used as an agile LO in communications, radar, and many other applications. The innovative high speed DDS core of the AD9854 provides 48-bit frequency resolution (1 μHz tuning resolution with 300 MHz SYSCLK). Maintaining 17 bits ensures excellent SFDR.概述在AD9854数字频率合成器是一种高度集成的器件,采用先进的DDS技术,具有两个内部耦合高速,高性能正交数模转换器以实现数字可编程的I/Q合成功能。

AD9854应用一.硬件设计 1. 总体框图2. 电源模块(1)单片机供电 : 5V (12V 转5V) 1N4007:稳压二极管1N4007的白色的那一端为正极,但是要利用其反向击穿特性实现稳压,所以要从阴极输入! 测试得,输入VCC12=12.29V , 输出为VCC5=5.05V!(2)AD9854供电:3.3V (5V 转3.3V ) MBR360:肖特基二极管3. 单片机(1)复位(2)晶振(11.0592M )(3)矩阵键盘(4)1602液晶(5)串行下载(6)单片机稳压供电问题参考AD9854的技术文档中的评估板的设计,在VCC5端口并联一个10uF极性电容和8个0.1uF的非极性电容!4. AD9854首先,先仔细阅读AD9854的每个管脚的具体作用的介绍,如下:引脚名称引脚及配置D7-D0 8 位双向并行编程数据输入。

只用于并行编程模式。

DVDD 连接到数字电路的供应电压。

通常为3.3V。

DGND 连接到数字电路的地。

功能同AGND。

NC 无内部连接。

A5-A0 编程寄存器的6位并行地址输入。

只用于并行编程模式。

当使用串行编程模式时A0,A1,A2使用它们各自的另一个功能,如下介绍:A2/IO RESET 串行通讯总线的I/O复位信号。

由于不合适的编程协议而造成无应答就会产生此复位信号。

用这种方式复位串行总线不会影响之前编好的程序,也不会唤醒“默认”编程值。

此脚工作状态为高。

A1/SDO 当使用3线串行通讯模式时的单向串行数据输出。

A0/SDIO 当使用2线串行通讯模式时的双向串行数据输入/输出。

在设计中只用其并型模式。

设计中将其与MSP430F149的P4口相连。

I/O UD CLK 双向I/O刷新时钟。

用作控制寄存器选择方向。

若选择作为输入,则会在上升沿时把I/O端口缓冲器的内容传送到程序寄存器。

若作为输出(默认),则在8个系统时钟周期期间的输出脉冲(低到高)就表明一个内部频率刷新已经发生了。

FEATURES300 MHz internal clock rateFSK, BPSK, PSK, chirp, AM operationDual integrated 12-bit digital-to-analog converters (DACs) Ultrahigh speed comparator, 3 ps rms jitterExcellent dynamic performance80 dB SFDR at 100 MHz (±1 MHz) AOUT4× to 20× programmable reference clock multiplierDual 48-bit programmable frequency registersDual 14-bit programmable phase offset registers12-bit programmable amplitude modulation andon/off output shaped keying functionSingle-pin FSK and BPSK data interfacesPSK capability via input/output interfaceLinear or nonlinear FM chirp functions with single-pin frequency hold functionFrequency-ramped FSK<25 ps rms total jitter in clock generator mode特征300 MHz内部时钟速率支持FSK, BPSK, PSK, chirp, AM调制集成双路12位数/模转换器(DAC)超高速比较器,3个PS RMS抖动出色的动态性能80dB的SFDR在100 MHz(±1 MHz)的AOUT4 ×20×可编程参考时钟倍频器双48位可编程频率寄存器双通道,14位可编程相位偏移寄存器12位可编程振幅调制ON / OFF输出形键控功能单引脚FSK和BPSK的数据接口通过输入/输出接口实现PSK功能单线实现线性或非线性的调频功能频率暂停功能频率ramped的FSK<25 ps的均方根时钟发生器模式的总抖动Automatic bidirectional frequency sweepingSin(x)/x correctionSimplified control interfaces10 MHz serial 2- or 3-wire SPI compatible100 MHz parallel 8-bit programming3.3 V single supplyMultiple power-down functionsSingle-ended or differential input reference clockSmall, 80-lead LQFP or TQFP with exposed padAPPLICATIONSAgile, quadrature LO frequency synthesisProgrammable clock generatorsFM chirp source for radar and scanning systemsTest and measurement equipmentCommercial and amateur RF exciters双向自动扫频sin(x)/ x修正简化的控制接口兼容10 MHz串行2 或3线SPI总线100兆赫并行8位总线3.3 V单电源供电多重省电功能参考时钟可单端或差分输入小型,80引脚LQFP或带有散热焊盘的TQFP封装应用正交LO频率合成可编程时钟发生器调频雷达和扫描系统的线性调频源测试与测量设备商业及业余射频发射器目录特点................................................. .............................................一应用................................................. ......................................一功能框图............................................... ...............一修订历史................................................ ...............................三一般描述................................................ . (4)规格................................................. (5)绝对最大额定值............................................... . (8)热阻................................................ . (8)测验等级说明.............................................. . (8)防静电提示................................................ . (8)引脚配置和功能说明 (9)典型性能特征 (12)典型应用................................................ .. (16)操作原理............................................... .. (19)操作模式............................................... .. (19)使用AD9854 ............................................... (29)内部和外部更新时钟 (29)ON / OFF输出形键控(侨丰) (29)I和Q数模转换器.............................................. .. (30)控制DAC ................................................ . (30)逆Sinc函数............................................... .. (31)REFCLK乘法器 (31)编程AD9854 ............................................... . (32)主复位................................................ (32)并行I / O操作............................................. (34)串行端口I / O操作............................................ .. (34)一般操作的串行接口 (36)指令字节................................................ .. (37)串行接口引脚说明 (37)串口操作的注意事项............................................. (37)的MSB / LSB的转移.............................................. (38)控制寄存器的说明............................................... .. (38)功耗和散热考虑 (40)热阻抗................................................ . (40)结温事项 (40)评价工作条件 (41)热增强型封装安装指南 (41)评估板................................................ . (42)评估板说明............................................... (42)一般操作说明 (42)使用提供的软件.............................................. (44)支持................................................. (44)外形尺寸................................................ .. (52)订购指南................................................ .. (52)GENERAL DESCRIPTIONThe AD9854 digital synthesizer is a highly integrated device that uses advanced DDS technology, coupled with two internal high speed, high performance quadrature DACs to form a digitally programmable I and Q synthesizer function. When referenced to an accurate clock source, the AD9854 generates highly stable, frequency-phase, amplitude-programmable sine and cosine outputs that can be used as an agile LO in communications, radar, and many other applications. The innovative high speed DDS core of the AD9854 provides 48-bit frequency resolution (1 μHz tuning resolution with 300 MHz SYSCLK). Maintaining 17 bits ensures excellent SFDR.概述在AD9854数字频率合成器是一种高度集成的器件,采用先进的DDS技术,具有两个内部耦合高速,高性能正交数模转换器以实现数字可编程的I/Q合成功能。