集成电路制造技术--原理与实践(扫描)第十一章

- 格式:pdf

- 大小:13.25 MB

- 文档页数:13

集成电路的设计与制造技术集成电路是现代电子技术的基础和核心。

集成电路是指将多个电子器件(如晶体管、电容器、电阻器等)在单个晶片上集成形成的一种电路。

集成电路的设计与制造技术是决定集成电路性能和质量的重要因素。

在集成电路的设计与制造技术中,有几个关键环节,分别是电路设计、芯片加工、封装和测试。

电路设计是集成电路制造的第一步。

电路设计师根据电子产品的功能需求和性能要求,设计出一套电路图。

设计电路是一项非常复杂的工作,需要电路设计者有扎实的电子知识和技术基础,并且需要使用各种电路设计软件和模拟工具。

芯片加工是实现电路设计的物理过程。

芯片加工围绕着制作集成电路晶片展开,包括制作晶圆、制作晶片、进行微细加工等。

晶片制作的关键就是利用半导体材料制造芯片。

半导体材料是一类具有特殊电子性质的材料,普遍采用硅和锗。

芯片制造的第一个步骤是将半导体材料制成圆片状(称为晶圆)。

晶圆的直径一般为6英寸、8英寸、12英寸,越大的晶圆可以制造的芯片越多,生产效率也越高。

制作晶片需要采用光刻技术,即通过光刻机把芯片上的电路图形映射到荧光涂料上,然后进行照射显影。

随后,进行电极蒙皮、纳米复合物制备、阵列装配等微细加工后,可制成完整的晶片。

接下来是芯片封装。

将制作好的芯片封装到外壳(或带电芯片、电路板等),保护芯片内部结构和电路,防止其受到外界的干扰和损坏,提高芯片的可靠性和稳定性。

封装技术是集成电路制造中的一个重要环节之一。

最后一个环节是芯片测试。

芯片测试的目的是确保芯片达到事先设定的性能指标。

芯片测试通常包括参数测量、功能测试和环境测试等。

参数测量是衡量芯片基本性能的测试,包括电流、电压、恒流、传输速率等。

功能测试是确保芯片实现了预期的功能。

环境测试是检测芯片在各种温度和湿度条件下工作的能力以及防静电能力等。

综上所述,集成电路的设计制造涉及到许多技术环节,包括电路设计、芯片加工、封装和测试等。

只有在每个环节都精益求精,才能制造出性能优良的集成电路。

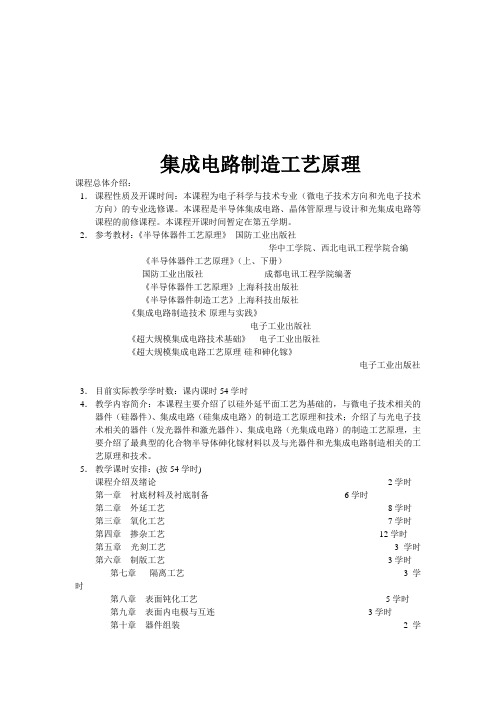

集成电路制造工艺原理课程总体介绍:1.课程性质及开课时间:本课程为电子科学与技术专业(微电子技术方向和光电子技术方向)的专业选修课。

本课程是半导体集成电路、晶体管原理与设计和光集成电路等课程的前修课程。

本课程开课时间暂定在第五学期。

2.参考教材:《半导体器件工艺原理》国防工业出版社华中工学院、西北电讯工程学院合编《半导体器件工艺原理》(上、下册)国防工业出版社成都电讯工程学院编著《半导体器件工艺原理》上海科技出版社《半导体器件制造工艺》上海科技出版社《集成电路制造技术-原理与实践》电子工业出版社《超大规模集成电路技术基础》电子工业出版社《超大规模集成电路工艺原理-硅和砷化镓》电子工业出版社3.目前实际教学学时数:课内课时54学时4.教学内容简介:本课程主要介绍了以硅外延平面工艺为基础的,与微电子技术相关的器件(硅器件)、集成电路(硅集成电路)的制造工艺原理和技术;介绍了与光电子技术相关的器件(发光器件和激光器件)、集成电路(光集成电路)的制造工艺原理,主要介绍了最典型的化合物半导体砷化镓材料以及与光器件和光集成电路制造相关的工艺原理和技术。

5.教学课时安排:(按54学时)课程介绍及绪论2学时第一章衬底材料及衬底制备6学时第二章外延工艺8学时第三章氧化工艺7学时第四章掺杂工艺12学时第五章光刻工艺3学时第六章制版工艺3学时第七章隔离工艺3学时第八章表面钝化工艺5学时第九章表面内电极与互连3学时第十章器件组装2学课程教案:课程介绍及序论(2学时)内容:课程介绍:1 教学内容1.1与微电子技术相关的器件、集成电路的制造工艺原理1.2 与光电子技术相关的器件、集成电路的制造1.3 参考教材2教学课时安排3学习要求序论:课程内容:1半导体技术概况1.1 半导体器件制造技术1.1.1 半导体器件制造的工艺设计1.1.2 工艺制造1.1.3 工艺分析1.1.4 质量控制1.2 半导体器件制造的关键问题1.2.1 工艺改革和新工艺的应用1.2.2 环境条件改革和工艺条件优化1.2.3 注重情报和产品结构的及时调整1.2.4 工业化生产2典型硅外延平面器件管芯制造工艺流程及讨论2.1 常规npn外延平面管管芯制造工艺流程2.2 典型pn隔离集成电路管芯制造工艺流程2.3 两工艺流程的讨论2.3.1 有关说明2.3.2 两工艺流程的区别及原因课程重点:介绍了与电子科学与技术中的两个专业方向(微电子技术方向和光电子技术方向)相关的制造业,指明该制造业是社会的基础工业、是现代化的基础工业,是国家远景规划中置于首位发展的工业。

“集成电路工艺原理”集成电路工艺原理复习2第一章导论半导体产业311 引言1.1 引言微电子学:Microelectronics-微型电子学微电子学是研究在固体(主要是半导体)材料上构成的微小型化电路及系统的电子学分支微电子学:Microelectronics 微型电子学成的微小型化电路及系统的电子学分支。

电子学4核心:集成电路。

微电子学11 引言1.1 引言集成电路:IC Integrated Circuit通过一系列特定的加工工艺,将晶体管、二极管等有源件容等件连集成电路:IC,Integrated Circuit器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体单晶片(如Si 、GaAs)上,封装在个外壳内执行特定电路或系统功能在一个外壳内,执行特定电路或系统功能。

封装后的集成电路511 特征尺寸Common IC Features1.1 特征尺寸Contact HoleLine Width Space关键尺寸(CD):集成电路中半导体器件能够加工的最小尺寸。

它是衡量集成电路设计和制造水平的重要尺度,关键尺寸越小,6它是衡量集成电路设计和制造水平的重要尺度,关键尺寸越小,芯片的集成度越高,速度越快,性能越好11 特征尺寸1.1 特征尺寸关键尺寸(CD)的发展711 特征尺寸晶体管集成数量的发展1.1 特征尺寸1971年,Intel的第一个微处理器4004:10微米工艺,仅包含2300多只晶体管;82010年,Intel的最新微处理器Core i7:32纳米工艺,包含近20亿只晶体管。

12 摩尔定律The Moore’s Law-摩尔定律1.2 摩尔定律Moore定律是在1965年由INTEL 公司的Gd M 提的Gor don M oore提出的,其内容是:硅集成电路按照4年为集成电路按照年为一代,每代的芯片集成度要翻两番、工艺线宽约缩小30% IC 线宽约缩小30%,IC工作速度提高1.5倍等发展规律发展。

第一单元:3.比较硅单晶锭CZ,MCZ和FZ三种生长方法的优缺点。

答:CZ直拉法工艺成熟,可拉出大直径硅棒,是目前采用最多的硅棒生产方法。

但直拉法中会使用到坩埚,而坩埚的使用会带来污染。

同时在坩埚中,会有自然对流存在,导致生长条纹和氧的引入。

直拉法生长多是采用液相掺杂,受杂质分凝、杂质蒸发,以及坩埚污染影响大,因此,直拉法生长的单晶硅掺杂浓度的均匀性较差。

MCZ磁控直拉法,在CZ法单晶炉上加一强磁场,高传导熔体硅的流动因切割磁力线而产生洛仑兹力,这相当于增强了熔体的粘性,熔体对流受阻。

能生长无氧、均匀好的大直径单晶硅棒。

设备较直拉法设备复杂得多,造价也高得多,强磁场的存在使得生产成本也大幅提高。

FZ悬浮区熔法,多晶与单晶均由夹具夹着,由高频加热器产生一悬浮的溶区,多晶硅连续通过熔区熔融,在熔区与单晶接触的界面处生长单晶。

与直拉法相比,去掉了坩埚,没有坩埚的污染,因此能生长出无氧的,纯度更高的单晶硅棒。

6.硅气相外延工艺采用的衬底不是准确的晶向,通常偏离[100]或[111]等晶向一个小角度,为什么?答:在外延生长过程中,外延气体进入反应器,气体中的反应剂气相输运到衬底,在高温衬底上发生化学反应,生成的外延物质沿着衬底晶向规则地排列,生长出外延层。

气相外延是由外延气体的气相质量传递和表面外延两个过程完成的。

表面外延过程实质上包含了吸附、分解、迁移、解吸这几个环节,表面过程表明外延生长是横向进行的,是在衬底台阶的结点位置发生的。

因此,在将硅锭切片制备外延衬底时,一般硅片都应偏离主晶面一个小角度。

目的是为了得到原子层台阶和结点位置,以利于表面外延生长。

7. 外延层杂质的分布主要受哪几种因素影响?答:杂质掺杂效率不仅依赖于外延温度、生长速率、气流中掺杂剂的摩尔分数、反应室的几何形状等因素,还依赖于掺杂剂自身的特性。

另外,影响掺杂效率的因素还有衬底的取向和外延层结晶质量。

硅的气相外延工艺中,在外延过程中,衬底和外延层之间存在杂质交换现象,即会出现杂质的再分布现象,主要有自掺杂效应和互扩散效应两种现象引起。

可编辑修改精选全文完整版集成电路实习报告艰辛而又充满意义的实习生活又告一段落了,想必都收获了成长和成绩,是时候回头总结这段时间的实习生活了。

你所见过的实习报告应该是什么样的?下面是小编帮大家整理的集成电路实习报告(通用6篇),仅供参考,大家一起来看看吧。

集成电路实习报告1一:实习目的1、学习焊接电路板的有关知识,熟练焊接的具体操作。

2、看懂收音机的原理电路图,了解收音机的基本原理,学会动手组装和焊接收音机。

3、学会调试收音机,能够清晰的收到电台。

4、学习使用protel电路设计软件,动手绘制电路图。

二:焊接的技巧或注意事项焊接是安装电路的基础,我们必须重视他的技巧和注意事项。

1、焊锡之前应该先插上电烙铁的插头,给电烙铁加热。

2、焊接时,焊锡与电路板、电烙铁与电路板的夹角最好成45度,这样焊锡与电烙铁夹角成90度。

3、焊接时,焊锡与电烙铁接触时间不要太长,以免焊锡过多或是造成漏锡;也不要过短,以免造成虚焊。

4、元件的腿尽量要直,而且不要伸出太长,以1毫米为好,多余的可以剪掉。

5、焊完时,焊锡最好呈圆滑的圆锥状,而且还要有金属光泽。

三:收音机的原理本收音机由输入回路高放混频级、一级中放、二级中放、前置低放兼检波级、低放级和功放级等部分组成接收频率范围为535千赫1065千赫的中段。

1、具体原理如下原理图所示:2、安装工艺要求:动手焊接前用万用表将各元件测量一下,做到心中有数,安装时先安装低矮和耐热元件(如电阻),然后再装大一点的元件(如中周、变压器),最后装怕热的元件(如三极管)。

电阻的安装:将电阻的阻值选择好后根据两孔的距离弯曲电阻脚可采用卧式紧贴电路板安装,也可以采用立式安装,高度要统一。

瓷片电容和三极管的脚剪的长短要适中,它们不要超过中周的高度。

电解电容紧贴线路板立式焊接,太高会影响后盖的安装。

、棒线圈的四根引线头可直接用电烙铁配合松香焊锡丝来回摩擦几次即可自动上锡,四个线头对应的焊在线路板的铜泊面。

《集成电路原理与设计》重点内容总结引言集成电路(Integrated Circuit, IC)作为现代电子工程的核心,其设计和制造技术的发展极大地推动了信息技术的进步。

《集成电路原理与设计》课程涵盖了IC设计的基础理论、工艺技术、设计流程和应用实例,对于电子工程领域的学生和专业人士具有重要意义。

第一部分:集成电路基础1.1 集成电路概述集成电路是将大量电子元件(如晶体管、电阻、电容等)集成在一块半导体材料(通常是硅)上的微型电子器件。

IC的出现极大地减小了电子设备的体积,提高了性能,降低了成本。

1.2 半导体物理基础半导体物理是IC设计的基础。

重点内容包括:半导体材料的特性,如硅和锗的电子结构。

PN结的形成和特性。

载流子(电子和空穴)的行为。

半导体中的扩散和漂移现象。

1.3 晶体管原理晶体管是IC中最基本的放大和开关元件。

重点内容包括:双极型晶体管(BJT)和金属氧化物半导体场效应晶体管(MOSFET)的工作原理。

晶体管的电流-电压特性。

晶体管的开关时间和速度。

第二部分:集成电路设计2.1 设计流程IC设计包括前端设计和后端设计两个主要阶段。

重点内容包括:系统规格定义和功能模块划分。

逻辑设计和电路设计。

物理设计,包括布局、布线和验证。

2.2 设计工具和方法IC设计涉及多种计算机辅助设计(CAD)工具和方法。

重点内容包括:硬件描述语言(如VHDL和Verilog)的使用。

逻辑综合和优化技术。

时序分析和仿真。

2.3 工艺技术IC的制造工艺对设计有重要影响。

重点内容包括:CMOS工艺流程。

工艺参数对IC性能的影响。

新型工艺技术,如FinFET和SOI。

第三部分:集成电路应用3.1 数字集成电路数字IC是实现数字逻辑功能的核心。

重点内容包括:门电路和触发器的设计。

算术逻辑单元(ALU)和微处理器的设计。

存储器的设计,如SRAM、DRAM和Flash。

3.2 模拟集成电路模拟IC用于处理模拟信号。

重点内容包括:放大器、滤波器和振荡器的设计。