【精品课件】数字电子技术第三章习题

- 格式:ppt

- 大小:540.50 KB

- 文档页数:25

数字电子技术题目第三章第三章组合逻辑电路一.填空题1.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A2A1A0=100时,输出Y7’Y6’Y5’Y4’Y3’Y2’Y1’Y0’应为。

2.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A2A1A0=101时,输出Y7’Y6’Y5’Y4’Y3’Y2’Y1’Y0’应为。

3.数字电路按照是否有记忆功能通常可分为两类:和。

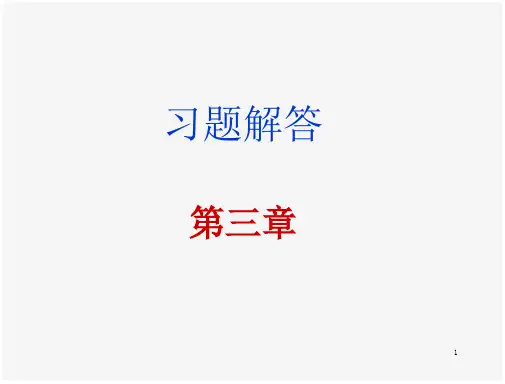

4.16选1数据选择器,其地址输入端有个5.8选1数据选择器有____________条地址控制线。

二.选择题1.在下列逻辑电路中,不是组合逻辑电路的是A.译码器B.编码器C.全加器D.寄存器2.三十二路数据选择器,其地址输入端有个A.16B.2C.5D.83.数据选择器是具有通道的器件A.多输入单输出B.多输入多输出C.单输入单输出D.单输入多输出4.欲对全班54个同学以二进制代码编码表示,最少需要二进制的位数是()A.5B.6C.10D.535.已知A、B为逻辑门的输入端,F为输出端,其输入、输出波形如图1所示。

试判断这是哪种逻辑门的波形。

图1A.与非门B.与门C.或非门D.或门三.分析与设计1.将逻辑函数F=A’B’+A’C’+ABC转化为与非-与非表达式,并画出只由与非门实现的逻辑电路图。

2.将逻辑函数Y=AB+BC+CA化为与非-与非形式,并画出只由与非门实现的逻辑电路图。

3.用8选1数据选择器74HC151实现函数F=A’C’+A’B’C+AB’C’+ABC。

74HC1514.用8选1数据选择器74HC151实现逻辑函数F=A’C’+A’B’+ABC。

74HC1515.用8选1数据选择器实现函数F=AC+A’BC’+A’B’C。

74HC1516.用译码器74HC138实现函数F=AC+A’BC’+A’B’C。

要求写出设计过程。

7.译码器74HC138的逻辑符号如图8所示。

用译码器74HC138实现逻辑函数F=AC+A’BC+A’B’。

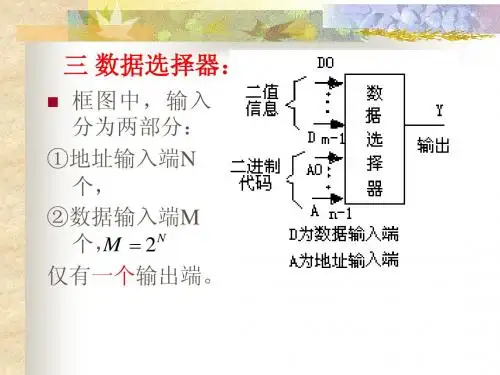

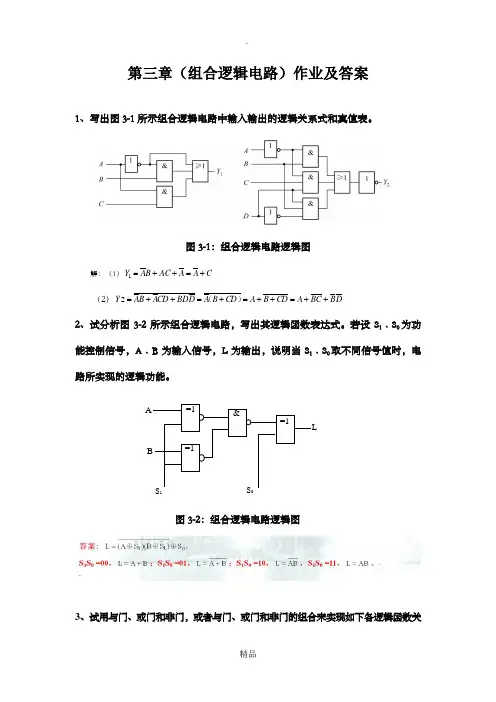

第三章(组合逻辑电路)作业及答案1、写出图3-1所示组合逻辑电路中输入输出的逻辑关系式和真值表。

图3-1:组合逻辑电路逻辑图解:(1)C A A AC B AY +=++=1(2)D B C B A CD B A CD B A D BD CD A B A Y ++=++=+=++=)(2 2、试分析图3-2所示组合逻辑电路,写出其逻辑函数表达式。

若设S 1﹑S 0为功能控制信号,A ﹑B 为输入信号,L 为输出,说明当S 1﹑S 0取不同信号值时,电路所实现的逻辑功能。

图3-2:组合逻辑电路逻辑图3、试用与门、或门和非门,或者与门、或门和非门的组合来实现如下各逻辑函数关ABS 1S=1=1&=1系,画出相应的逻辑电路图。

(1)1Y AB BC=+(2)2Y A C B=+()(3)3Y ABC B EF G=++()&&1≥Y1.1ABC.&1≥Y2.1ABC&1≥1≥&&1ABC.EFG.Y3...4、试用门电路设计4线-2线优先编码器,输入、输出信号都是高电平有效,要求任一按键按下时,G S为1,否则G S=0;还要求没有按键按下时,E O信号为1,否则为0。

5、试用逻辑门电路设计一个2选1数据选择器,输入信号为A、B,选择信号为S,输出信号为Y,要求写出真值表、逻辑函数表达式和画出逻辑电路图。

6、某公司3条装配线各需要100kW电力,采用两台发电动机供电,一台100kW,另外一台是200kW,3条装配线不同时开工,试设计一个发电动机控制电路,可以按照需求启动发电动机以达到节电的目的。

7、图3-3是由3线/8线译码器74LS138和与非门构成的组合逻辑电路,试写出P和P2的逻辑表达式,并列出真值表,说明其逻辑功能。

1BIN/OCT01201234567B AC 10074LS138P 1P 2图3-3 组合逻辑电路图8、试用3线-8线译码器74LS138和与非门实现以下多输出函数:1F AB C AB BC AC =++(,,) ∑=),,,(),,(75422m C B A F9、图3-4是由八选一数据选择器74LS151构成的组合逻辑电路,试写出当G 1G 0为各种不同取值时输出Y 与输入A 、B 的逻辑函数表达式。

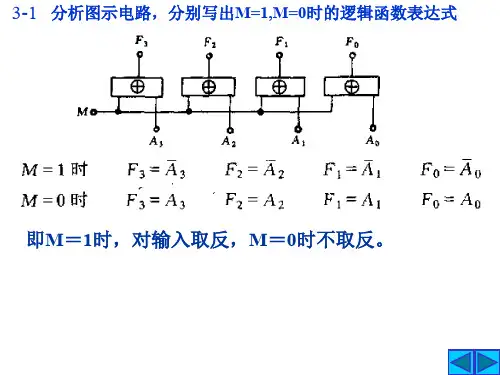

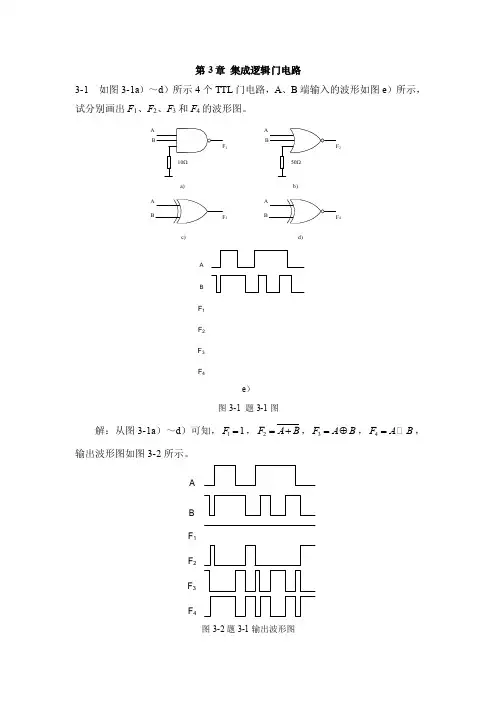

第3章集成逻辑门电路3-1 如图3-1a)~d)所示4个TTL门电路,A、B端输入的波形如图e)所示,试分别画出F1、F2、F3和F4的波形图。

A1A234a)b)c)d)F1F2F3F4BAe)图3-1 题3-1图解:从图3-1a)~d)可知,11F=,2F A B=+,3F A B=⊕,4F A B= ,输出波形图如图3-2所示。

F1F2F3F4AB图3-2题3-1输出波形图3-2 电路如图3-3a )所示,输入A 、B 的电压波形如图3-3b )所示,试画出各个门电路输出端的电压波形。

1A 23b)a)AB图3-3 题3-2图解:从图3-3a )可知,1F AB =,2F A B =+,3F A B =⊕,输出波形如图3-4所示。

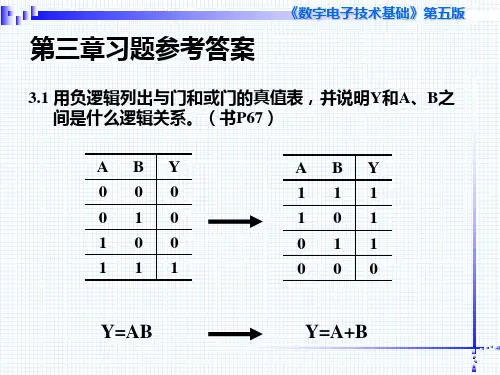

F 1F 2F 3AB图3-4 题3-2输出波形3-3在图3-5a )所示的正逻辑与门和图b )所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F 和A 、B 之间是什么逻辑关系。

b)a)图3-5 题3-3图解:(1)图3-5a )负逻辑真值表如表3-1所示。

表3-1 与门负逻辑真值表F 与A 、B 之间相当于正逻辑的“或”操作。

(2)图3-5b )负逻辑真值表如表3-2所示。

表3-2 或门负逻辑真值表F 与A 、B 之间相当于正逻辑的“与”操作。

3-4试说明能否将与非门、或非门和异或门当做反相器使用?如果可以,各输入端应如何连接?解:与非门、或非门和异或门经过处理以后均可以实现反相器功能。

1)与非门:将多余输入端接至高电平或与另一端并联; 2)或非门:将多余输入端接至低电平或与另一端并联;3) 异或门:将另一个输入端接高电平。

3-5为了实现图3-6所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

b)a)AB=A B=+A BC DABC D图3-6 题3-5图解:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b )多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

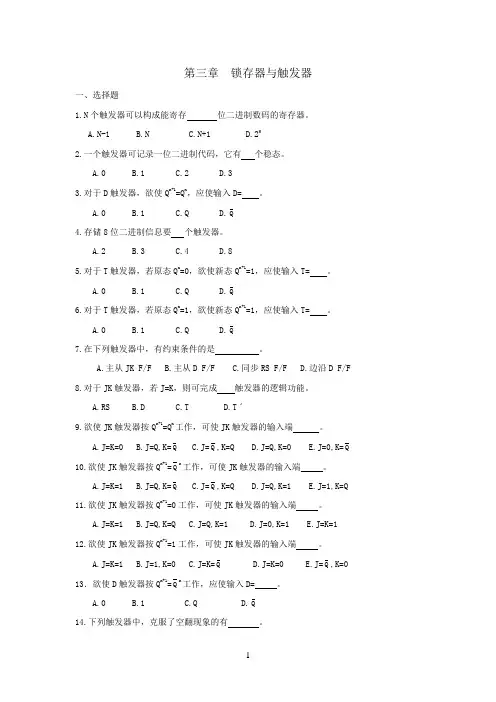

第三章锁存器与触发器一、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.33.对于D触发器,欲使Q n+1=Q n,应使输入D= 。

A.0B.1C.QD.Q4.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q7.在下列触发器中,有约束条件的是。

A.主从JK F/FB.主从D F/FC.同步RS F/FD.边沿D F/F8.对于JK触发器,若J=K,则可完成触发器的逻辑功能。

A.RSB.DC.TD.Tˊ9.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=0B.J=Q,K=QC.J=Q,K=QD.J=Q,K=0E.J=0,K=Q10.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=QD.J=Q,K=1E.J=1,K=Q11.欲使JK触发器按Q n+1=0工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=1D.J=0,K=1E.J=K=112.欲使JK触发器按Q n+1=1工作,可使JK触发器的输入端。

A.J=K=1B.J=1,K=0C.J=K=QD.J=K=0E.J=Q,K=0 13.欲使D触发器按Q n+1=Q n工作,应使输入D= 。

A.0B.1C.QD.Q14.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从RS触发器C.同步RS触发器D.主从JK触发器15.下列触发器中,没有约束条件的是。

A.基本RS触发器B.主从RS触发器C.同步RS触发器D.边沿D触发器16.为实现将JK触发器转换为D触发器,应使。

第三章集成逻辑门电路一、选择题1. 三态门输出高阻状态时,()是正确的说法。

A.用电压表测量指针不动B.相当于悬空C.电压不高不低D.测量电阻指针不动2. 以下电路中可以实现“线与”功能的有()。

A.与非门B.三态输出门C.集电极开路门D.漏极开路门3.以下电路中常用于总线应用的有()。

A.TSL门B.OC门C. 漏极开路门D.CMOS与非门4.逻辑表达式Y=AB可以用()实现。

A.正或门B.正非门C.正与门D.负或门5.TTL电路在正逻辑系统中,以下各种输入中()相当于输入逻辑“1”。

A.悬空B.通过电阻2.7kΩ接电源C.通过电阻2.7kΩ接地D.通过电阻510Ω接地6.对于TTL与非门闲置输入端的处理,可以()。

A.接电源B.通过电阻3kΩ接电源C.接地D.与有用输入端并联7.要使TTL与非门工作在转折区,可使输入端对地外接电阻RI()。

A.>RONB.<ROFFC.ROFF<RI<ROND.>ROFF8.三极管作为开关使用时,要提高开关速度,可( )。

A.降低饱和深度B.增加饱和深度C.采用有源泄放回路D.采用抗饱和三极管9.CMOS数字集成电路与TTL数字集成电路相比突出的优点是()。

A.微功耗B.高速度C.高抗干扰能力D.电源范围宽10.与CT4000系列相对应的国际通用标准型号为()。

A.CT74S肖特基系列B. CT74LS低功耗肖特基系列C.CT74L低功耗系列D. CT74H高速系列11.电路如图(a),(b)所示,设开关闭合为1、断开为0;灯亮为1、灯灭为0。

F 对开关A、B、C的逻辑函数表达式()。

F1F2 (a)(b)A.C AB F =1 )(2B A C F += B.C AB F =1 )(2B A C F +=C. C B A F =2 )(2B A C F +=12.某TTL 反相器的主要参数为IIH =20μA ;IIL =1.4mA ;IOH =400μA ;水IOL =14mA ,带同样的门数( )。

[题3.1] 分析P3.1电路的逻辑功能,写出Y 1、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

答案:12()Y ABC A B C AB AC BC ABC ABC Y AB BC AC=+++∙++=++=++由真值表可见,这是一个全加器电路。

A 、B 、C 为加数、被加数和来自低位的进位,Y 1是和,Y 2是进位输出。

[题3.3] 用或非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其它状态时输出为0。

答案:Y ABCD ABCD ABCD ABCD ABCDABC ABD ACD BCD ABC ABD ACD BCD=++++=+++=+++[题3.7] 某医院有一、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

现要求当一号病室的按钮按下时,无论其它病室的按钮是否按下,只有一号灯亮。

当一号病室的按钮没有按下而二号病室的按钮按下时,无论三号、四号病室的按钮是否按下,只有二号灯亮。

当一号、二号病室的按钮没有按下而三号病室的按钮按下时,无论四号病室的按钮是否按下,只有三号灯亮。

只有在一号、二号、三号病室的按钮均未按下而四号病室的按钮按下时,四号灯才亮。

试用优先编码器74LS148和门电路设计满足以上控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。

答案:以1234A A A A 、、、分别表示按下一、二、三、四号病室按钮给出的低电平信号,以1234Y Y Y Y 、、、表示一、二、三、四号灯亮的信号。

电路如图A3.7。

[题3.8] 写出图P3.8中Z 1、Z 2、Z 3的逻辑函数式,并化简为最简的与-或表达式。

译码器74LS42的逻辑图见图3.3.10。

答案: 1147Z Y Y Y M N PQ M N PQ M NPQ ==++ 2258Z Y Y Y M NPQ M N PQ M N PQ ==++3369Z Y Y Y M NPQ M NPQ M N PQ ==++[题3.10] 试画出用3线-8线译码器74LS138(见图3.3.8)和门电路产生如下多输出逻辑函数的逻辑图。