数字电子技术第三章

- 格式:ppt

- 大小:1.53 MB

- 文档页数:96

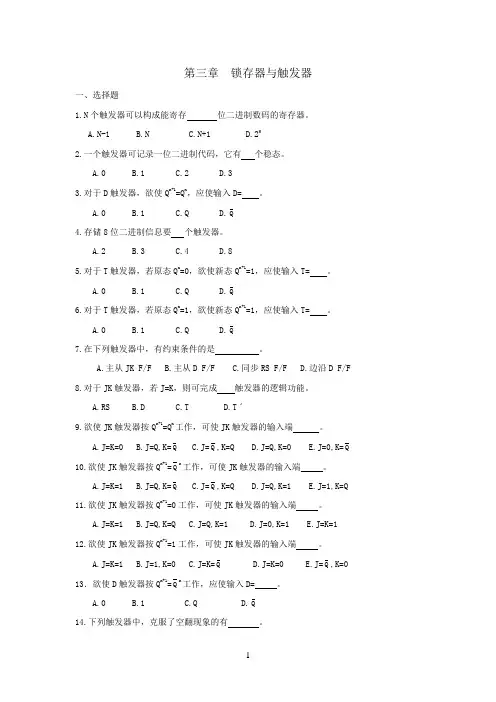

第三章锁存器与触发器一、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.33.对于D触发器,欲使Q n+1=Q n,应使输入D= 。

A.0B.1C.QD.Q4.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q7.在下列触发器中,有约束条件的是。

A.主从JK F/FB.主从D F/FC.同步RS F/FD.边沿D F/F8.对于JK触发器,若J=K,则可完成触发器的逻辑功能。

A.RSB.DC.TD.Tˊ9.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=0B.J=Q,K=QC.J=Q,K=QD.J=Q,K=0E.J=0,K=Q10.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=QD.J=Q,K=1E.J=1,K=Q11.欲使JK触发器按Q n+1=0工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=1D.J=0,K=1E.J=K=112.欲使JK触发器按Q n+1=1工作,可使JK触发器的输入端。

A.J=K=1B.J=1,K=0C.J=K=QD.J=K=0E.J=Q,K=0 13.欲使D触发器按Q n+1=Q n工作,应使输入D= 。

A.0B.1C.QD.Q14.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从RS触发器C.同步RS触发器D.主从JK触发器15.下列触发器中,没有约束条件的是。

A.基本RS触发器B.主从RS触发器C.同步RS触发器D.边沿D触发器16.为实现将JK触发器转换为D触发器,应使。

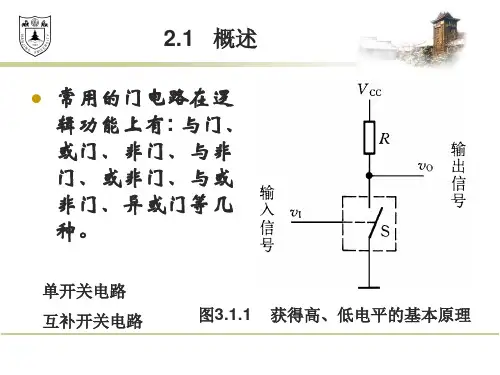

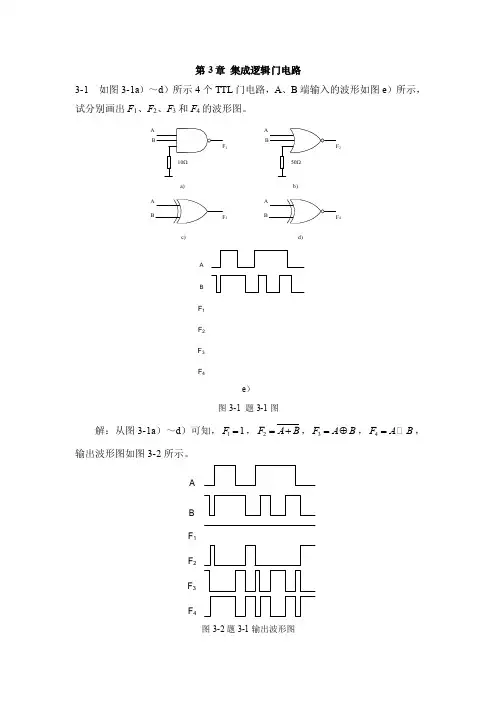

第3章集成逻辑门电路3-1 如图3-1a)~d)所示4个TTL门电路,A、B端输入的波形如图e)所示,试分别画出F1、F2、F3和F4的波形图。

A1A234a)b)c)d)F1F2F3F4BAe)图3-1 题3-1图解:从图3-1a)~d)可知,11F=,2F A B=+,3F A B=⊕,4F A B= ,输出波形图如图3-2所示。

F1F2F3F4AB图3-2题3-1输出波形图3-2 电路如图3-3a )所示,输入A 、B 的电压波形如图3-3b )所示,试画出各个门电路输出端的电压波形。

1A 23b)a)AB图3-3 题3-2图解:从图3-3a )可知,1F AB =,2F A B =+,3F A B =⊕,输出波形如图3-4所示。

F 1F 2F 3AB图3-4 题3-2输出波形3-3在图3-5a )所示的正逻辑与门和图b )所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F 和A 、B 之间是什么逻辑关系。

b)a)图3-5 题3-3图解:(1)图3-5a )负逻辑真值表如表3-1所示。

表3-1 与门负逻辑真值表F 与A 、B 之间相当于正逻辑的“或”操作。

(2)图3-5b )负逻辑真值表如表3-2所示。

表3-2 或门负逻辑真值表F 与A 、B 之间相当于正逻辑的“与”操作。

3-4试说明能否将与非门、或非门和异或门当做反相器使用?如果可以,各输入端应如何连接?解:与非门、或非门和异或门经过处理以后均可以实现反相器功能。

1)与非门:将多余输入端接至高电平或与另一端并联; 2)或非门:将多余输入端接至低电平或与另一端并联;3) 异或门:将另一个输入端接高电平。

3-5为了实现图3-6所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

b)a)AB=A B=+A BC DABC D图3-6 题3-5图解:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b )多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。