数字电子技术讲义 第三章 组合逻辑电路

- 格式:doc

- 大小:2.44 MB

- 文档页数:11

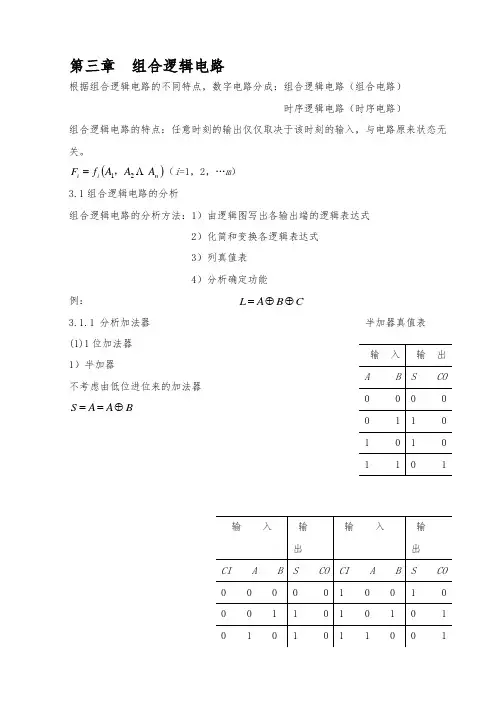

第三章 组合逻辑电路根据组合逻辑电路的不同特点,数字电路分成:组合逻辑电路(组合电路)时序逻辑电路(时序电路)组合逻辑电路的特点:任意时刻的输出仅仅取决于该时刻的输入,与电路原来状态无关。

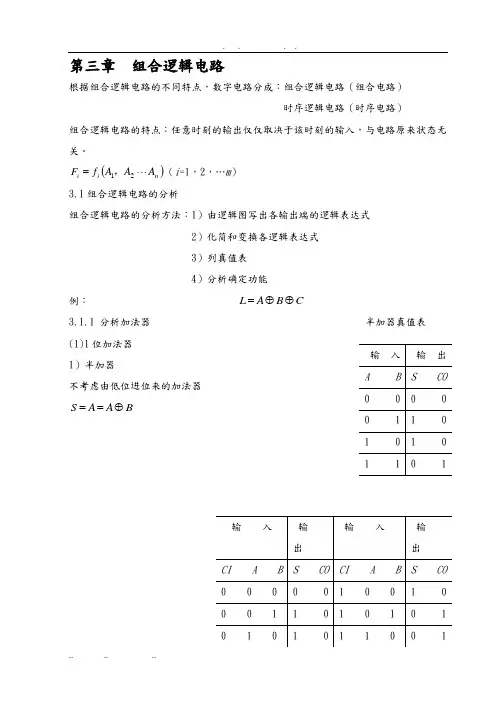

()n i i A A A f F Λ21,=(i =1,2,…m )3.1组合逻辑电路的分析组合逻辑电路的分析方法:1)由逻辑图写出各输出端的逻辑表达式2)化简和变换各逻辑表达式 3)列真值表 4)分析确定功能例: C B A L ⊕⊕=3.1.1 分析加法器 半加器真值表 (1)1位加法器 1)半加器不考虑由低位进位来的加法器B A A S ⊕==AB Co =2)全加器考虑低位进位的加法器CI B A CI AB CI B A BCI A S +++= 全加器真值表 CI B B A CI A CO ++=S “奇数个1时,S 为1”CI “两个以上1时,CI 为1”A(2)多位加法器1、并行相加串行进位的加法器例如:四位二进制数A 3 A 2A 1A 0和B 3 B 3 B 3 B 3相加CICO ΣCICO ΣCICO ΣCICO ΣCOS 1S 0S 2S 3A 0B 0A 1B 1A 2B 2A 3B 3每位进位信号作为高位的输入信号――串行进位故任一位的加法运算必须在低一位的运算完成后才能进行――速度慢 2、超前进位每位的进位只由加数和被加数决定,而与低位的进位无关。

1-⊕⊕=i i i i C B A S ()1-⊕+=i i i i i i C B A B A C3.1.2 分析数据选择器数据分配器:将公共数据线上的信号送往不同的通道 数据选择器:将不同通道的信号送往公共数据线74LS153为例:通过给定不同的地址代码,即可从4个输入数据中选出所要得输出 函数式:()()()()[]01130112011101101A A D A A D A A D A A D Y +++= 总结:1、数据选择器可将多通道输入的数据有选择的传送到输出端2、数据选择器还可作为一般的逻辑函数产生器,一个2n选一的数据选择器可以产生n 或少于n 个输入变量的逻辑函数3、构成逻辑函数产生器的关键是确定常量输入端的逻辑值。

第三章 组合逻辑电路根据组合逻辑电路的不同特点,数字电路分成:组合逻辑电路(组合电路)时序逻辑电路(时序电路)组合逻辑电路的特点:任意时刻的输出仅仅取决于该时刻的输入,与电路原来状态无关。

()n i i A A A f F 21,=(i =1,2,…m )3.1组合逻辑电路的分析组合逻辑电路的分析方法:1)由逻辑图写出各输出端的逻辑表达式2)化简和变换各逻辑表达式 3)列真值表 4)分析确定功能例: C B A L ⊕⊕=3.1.1 分析加法器 半加器真值表 (1)1位加法器 1)半加器不考虑由低位进位来的加法器B A A S ⊕==2)全加器考虑低位进位的加法器CI B A CI AB CI B A BCI A S +++= 全加器真值表 CI B B A CI A CO ++=S “奇数个1时,S 为1”CI “两个以上1时,CI 为1”A(2)多位加法器1、并行相加串行进位的加法器例如:四位二进制数A 3 A 2A 1A 0和B 3 B 3 B 3 B 3相加CICO ΣCICO ΣCICO ΣCICO ΣCOS 1S 0S 2S 3A 0B 0A 1B 1A 2B 2A 3B 3每位进位信号作为高位的输入信号――串行进位故任一位的加法运算必须在低一位的运算完成后才能进行――速度慢 2、超前进位每位的进位只由加数和被加数决定,而与低位的进位无关。

1-⊕⊕=i i i i C B A S ()1-⊕+=i i i i i i C B A B A C3.1.2 分析数据选择器数据分配器:将公共数据线上的信号送往不同的通道 数据选择器:将不同通道的信号送往公共数据线74LS153为例:通过给定不同的地址代码,即可从4个输入数据中选出所要得输出 函数式:()()()()[]01130112011101101A A D A A D A A D A A D Y +++= 总结:1、数据选择器可将多通道输入的数据有选择的传送到输出端2、数据选择器还可作为一般的逻辑函数产生器,一个2n选一的数据选择器可以产生n 或少于n 个输入变量的逻辑函数3、构成逻辑函数产生器的关键是确定常量输入端的逻辑值。

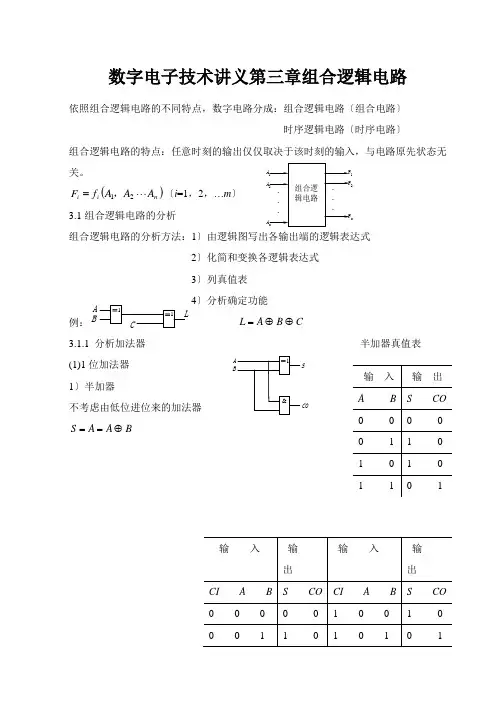

数字电子技术讲义第三章组合逻辑电路依照组合逻辑电路的不同特点,数字电路分成:组合逻辑电路〔组合电路〕时序逻辑电路〔时序电路〕组合逻辑电路的特点:任意时刻的输出仅仅取决于该时刻的输入,与电路原先状态无关。

()n i i A A A f F 21,=〔i =1,2,…m 〕3.1组合逻辑电路的分析组合逻辑电路的分析方法:1〕由逻辑图写出各输出端的逻辑表达式2〕化简和变换各逻辑表达式 3〕列真值表4〕分析确定功能例:C B A L ⊕⊕=3.1.1 分析加法器 半加器真值表 (1)1位加法器 1〕半加器不考虑由低位进位来的加法器 B A A S ⊕==A B BAB Co =2〕全加器考虑低位进位的加法器CI B A CI AB CI B A BCI A S +++= 全加器真值表 CI B B A CI A CO ++=S 〝奇数个1时,S 为1〞CI 〝两个以上1时,CI 为1〞A(2)多位加法器1、并行相加串行进位的加法器例如:四位二进制数A 3 A 2A 1A 0和B 3 B 3 B 3 B 3相加CICO ΣCICO ΣCICO ΣCICO ΣCOS 1S 0S 2S 3A 0B 0A 1B 1A 2B 2A 3B 3每位进位信号作为高位的输入信号――串行进位故任一位的加法运算必须在低一位的运算完成后才能进行――速度慢 2、超前进位00011011 0 1A BCI01011100011011 01A BCI 00100111每位的进位只由加数和被加数决定,而与低位的进位无关。

1-⊕⊕=i i i i C B A S ()1-⊕+=i i i i i i C B A B A C3.1.2 分析数据选择器数据分配器:将公共数据线上的信号送往不同的通道 数据选择器:将不同通道的信号送往公共数据线74LS153为例:通过给定不同的地址代码,即可从4个输入数据中选出所要得输出 函数式:()()()()[]01130112011101101A A D A A D A A D A A D Y +++= 总结:1、数据选择器可将多通道输入的数据有选择的传送到输出端2、数据选择器还可作为一样的逻辑函数产生器,一个2n 选一的数据选择器能够产生n 或少于n 个输入变量的逻辑函数3、构成逻辑函数产生器的关键是确定常量输入端的逻辑值。

第三章 组合逻辑电路根据组合逻辑电路的不同特点,数字电路分成:组合逻辑电路(组合电路)时序逻辑电路(时序电路)组合逻辑电路的特点:任意时刻的输出仅仅取决于该时刻的输入,与电路原来状态无关。

()n i i A A A f F Λ21,=(i =1,2,…m )3.1组合逻辑电路的分析组合逻辑电路的分析方法:1)由逻辑图写出各输出端的逻辑表达式2)化简和变换各逻辑表达式 3)列真值表4)分析确定功能例:C B A L ⊕⊕=3.1.1 分析加法器 半加器真值表 (1)1位加法器 1)半加器不考虑由低位进位来的加法器B A A S ⊕==A B BAB Co =2)全加器考虑低位进位的加法器CI B A CI AB CI B A BCI A S +++= 全加器真值表 CI B B A CI A CO ++=S “奇数个1时,S 为1”CI “两个以上1时,CI 为1”A(2)多位加法器1、并行相加串行进位的加法器例如:四位二进制数A 3 A 2A 1A 0和B 3 B 3 B 3 B 3相加CICO ΣCICO ΣCICO ΣCICO ΣCOS 1S 0S 2S 3A 0B 0A 1B 1A 2B 2A 3B 3每位进位信号作为高位的输入信号――串行进位故任一位的加法运算必须在低一位的运算完成后才能进行――速度慢 2、超前进位00011011 0 1A BCI01011100011011 01A BCI 00100111每位的进位只由加数和被加数决定,而与低位的进位无关。

1-⊕⊕=i i i i C B A S ()1-⊕+=i i i i i i C B A B A C3.1.2 分析数据选择器数据分配器:将公共数据线上的信号送往不同的通道 数据选择器:将不同通道的信号送往公共数据线74LS153为例:通过给定不同的地址代码,即可从4个输入数据中选出所要得输出 函数式:()()()()[]01130112011101101A A D A A D A A D A A D Y +++= 总结:1、数据选择器可将多通道输入的数据有选择的传送到输出端2、数据选择器还可作为一般的逻辑函数产生器,一个2n 选一的数据选择器可以产生n 或少于n 个输入变量的逻辑函数3、构成逻辑函数产生器的关键是确定常量输入端的逻辑值。

可由导出的最小项或真值表获得。

3.1.3 分析多路分配器D A A D 010= D A A D 011= D A A D 012= A A D 013= A A D3.1.4 分析数值比较器 (1)1位数值比较器两个数AB 比较(A >B ,A <B ,A=B )312A AB A Y =,A B A B A Y B A =+==⊙B ,B A Y =AB 1(A >B )2(A <B )3(A =B )(2)多位数值比较器由高位比较,若不相等则作为比较结果;若相等,在依次比较低位;当比较到最低位均相等则两数相等。

3.2 组合逻辑电路的设计组合逻辑电路设计的一般步骤:1)根据要求列出真值表2)由真值表写出表达式 3)简化和变换表达式 4)画出逻辑图例:三人简单表决电路,多数赞成,通过,灯亮;否则,灯不亮。

COMPA 0A 1A 2A 3B 3B 1B 0B 2A <BA =B A <B ><=Y (A >B )Y (A =B )Y (A <B )I (A <B )I (A =B )I (A >B )ABC3.2.1 设计编码器(1)普通编码器3位二进制编码器的设计 765476542I I I I I I I I Y =+++=763276321I I I I I I I I Y =+++=7531I I I I I I I I Y =+++=(2)二-十进制优先编码器(下图74LS147)00011011 0 1A BC 00100111012I I I I I I I I 102当编码器的多个输入端同时有效时,输出编码是按事先编好的次序输出的。

98642198643986598790I I I I I I I I I I I I I I I I I I I Y ++++++++= 98542985439869871I I I I I I I I I I I I I I I I Y +++++++= 9849859869872I I I I I I I I I I I I Y +++++++= 983I I Y +=3.2.2 设计译码器 1、二进制译码器的设计 3线-8线为例 真值表由真值表写出逻辑表达式:0120A A A Y =,0121A AA Y =,0122A A A Y =,0123A A A Y =,0124A A A Y =,0125A A A Y =, 0126A A A Y =,0127A A A Y =由逻辑表达式画出逻辑图(书54页) 2、二-十进制译码器 真值表(下页)由真值表写出逻辑表达式:01230A A A A Y =,01231A A A A Y =,01232A A A A Y =,01233A A A A Y =01234A A A A Y =,01235A A A A Y =,01236A A A A Y =,01237A A A A Y = 01238A A A A Y =,01239A A A A Y =由逻辑表达式画出逻辑图(书55页)3、七段字形显示译码器的设计数码显示器(数码管):用来显示数字,文字或符号的器件 显示方式:字形重叠式-不同字符重叠 分段式-若干断发光的笔划组成点阵式-发光点阵组成按发光物质:半导体显示器-发光二极管荧光数码管-荧光粉 液体显示器-液晶 气体放电显示器-当将数码管所代表的数显示出来,须将数码经译码器译出,然后驱动点亮对应的段。

例:显示8421码的0010,对应的十进制数2,则应译码驱动使a,d,e,g 段点亮。

即:对应某一组数码,译码器应有确定的几个输出。

3.3 组合逻辑电路中的竞争和冒险以前所述的组合逻辑电路,设0=pd t ,实际上0≠pd t 。

由于由输入到输出,不同的路径所需时间不同,可能使逻辑电路产生错误输出,此现象称为竞争冒险。

3.3.1 产生竞争冒险原因LAA两个输入信号分别由两个路径在不同时刻到达的现象-竞争-由此而产生输出干扰脉冲的现象称为冒险。

C BC B AC L += 当A=B =1时,L 应为“1”与C 无关,但当01→=C 时,输出出现负跳变冒 险现象。

由上可知,当电路中存在由反相器产生的互补信号,且在互补信号的状态发生变化时可能出现冒险现象。

3.3.2 消除竞争冒险的方法 1、发现并消去互补变量()()C A B A F ++=当B=C =0时,A A F =变为BC B A AC F ++=消去A A2、增加乘积项C B AC L +=当A=B =1时,C C L +=变为AB C B AC L ++=3、接入滤波电容因为竞争冒险产生的输出跳变脉冲很窄,所以当电路工作速度不太高时,可在输出端并联电容(4~20u F )使输出波形上升沿和下降沿变化较平缓。

A3.4用MSI 器件设计组合逻辑电路A BC CB C LAC AC B3.4.1 用数据选择器设计其他逻辑电路1、要实现的逻辑函数变量个数=数据选择器地址输入端个数,直接实现。

例:用74LS153(双4选1)实现()B A B A B A F +=,解:输出函数为()()()()[]01130112011101101A A D A A D A A D A A D Y +++=, 则有:D 10=0,D 11=1,D 12=1,D 13=0,A 1=A ,A 0=B ,Y 1=F2、要实现的逻辑函数变量个数>数据选择器地址输入端个数,分离变量。

例:用74LS151(8选1)实现()AB C B A BC A C B A F ++=,, 解:()C AB ABC C B A BC A C B A F +++=,, 输出函数:ABC D C AB D C B A D C B A D BC A D C B A D C B A D C B A D Y 76543210+++++++=得:D 0=D 1=D 2=D 4=0,D 3=D 5=D 6=D 7=1例:用74LS153(双4选1)实现ABC C B A BC A C B A F +++= 解:F 的最小项表达式:C AB C B A C B A C B A F )()()()(+++= 选择器输出函数:()()()()[]01130112011101101A A D A A D A A D A A D Y +++= 则有:A 1=A ,A 0=B ,C D =10,D 11=1 ,D 12=0 ,D 13=C ,Y 1=F 3.4.2 用译码器设计其他逻辑电路 1、用译码器实现逻辑函数001230m A A A A Y ==,101231m A A A A Y ==,201232m A A A A Y ==301233m A A A A Y ==,401234m A A A A Y ==,501235m A A A A Y ==, 601236m A A A A Y ==,701237m A A A A Y ==,801238m A A A A Y ==,901239m A A A A Y ==A B C……………………………………………………………精品资料推荐…………………………………………………11例:用74LS138实现()BC C B A C B A F +=,, 解:()ABC BC A C B A C B A F ++=,,()731731,,m m m m m m C B A F =++=例:用74LS138实现一个多输出的组合逻辑电路,输出函数为:()ABC C B A C B A C B A C B A Y +++=,,1,()ABC C B A C AB BC A C B A Y +++=,,2解:()742174211,,m m m m m m m m ABC C B A C B A C B A C B A Y =+++=+++=()765376532,,m m m m m m m m ABC C B A C AB BC A C B A Y =+++=+++=2B 122、用译码器作多路分配器用74LS138实现多路分配器的功能。

解:3210120S S S A A A Y =,3210121S S S A A A Y =,3210122S S S A A A Y =,3210123S S S A A A Y =,3210124S S S A A A Y =,3210125S S S A A A Y =, 3210126S S S A A A Y =,3210127S S S A A A Y =D。