Verilog硬件描述语言参考手册

- 格式:pdf

- 大小:196.00 KB

- 文档页数:17

SystemVerilog标准手册一、概述SystemVerilog是一种硬件描述和验证语言,它结合了Verilog HDL和VHDL的特性,并增添了许多新的功能和特性。

SystemVerilog的标准手册是SystemVerilog语言的权威参考资料,它详细说明了SystemVerilog的语法、语义和用法规范。

二、内容1. 语言基础SystemVerilog标准手册包含了SystemVerilog语言的基础知识,如数据类型、变量定义、控制结构、函数和任务等。

在这一部分,读者可以了解到SystemVerilog的基本语法和语言特性,为后续的学习和应用打下坚实的基础。

2. 对象和类SystemVerilog引入了面向对象的编程思想,允许用户定义自定义类型、类和对象。

SystemVerilog标准手册详细介绍了对象和类的定义、成员函数、继承和多态等相关内容,为用户提供了丰富的编程工具和技巧。

3. 验证方法SystemVerilog不仅可以用于硬件描述,还可以用于硬件验证。

SystemVerilog标准手册介绍了SystemVerilog的验证方法和工具,包括assertion、coverage、constrained randomization等内容,帮助用户编写高效且可靠的验证代码。

4. 高级特性除了基本的语言特性外,SystemVerilog还提供了许多高级的功能和特性,如接口、多线程、并发控制等。

SystemVerilog标准手册深入介绍了这些高级特性的用法和原理,帮助用户更好地理解和应用SystemVerilog语言。

5. 应用实例除了语法和特性的介绍外,SystemVerilog标准手册还提供了大量的实际应用示例,包括硬件描述、验证代码和仿真模型等。

这些应用实例可以帮助用户更直观地了解SystemVerilog语言的实际应用场景,加深对SystemVerilog的理解和掌握。

三、重要性SystemVerilog标准手册是学习和使用SystemVerilog语言的重要参考资料。

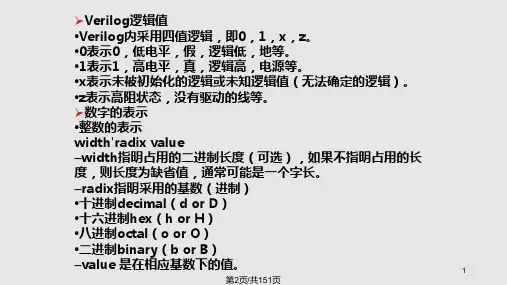

Verilog HDL硬件描述语言2.1 Verilog HDL概述2.1.1 Verilog HDL的特点Verilog HDL和VHDL一样,是目前大规模集成电路设计中最具代表性、使用最广泛的硬件描述语言之一。

作为硬件描述语言,Verilog HDL具有如下特点:1. 能够在不同的抽象层次上,如系统级、行为级、RTL(Register Transfer Level)级、门级和开关级,对设计系统进行精确而简练的描述;2. 能够在每个抽象层次的描述上对设计进行仿真验证,及时发现可能存在的设计错误,缩短设计周期,并保证整个设计过程的正确性;3. 由于代码描述与具体工艺实现无关,便于设计标准化,提高设计的可重用性。

如果有C语言的编程经验,只需很短的时间内就能学会和掌握Verilog HDL,因此,Verilog HDL可以作为学习HDL设计方法的入门和基础。

2.1.2 Verilog HDL的基本结构Verilog HDL描述是由模块(module)构成的,每个模块对应的是硬件电路中的逻辑实体。

因此,每个模块都有自己独立的功能或结构,以及用于与其它模块之间相互通信的端口。

例如,一个模块可以代表一个简单的门,一个计数器,一个存储器,甚至是计算机系统等。

例2-1-1 加法器的verilog描述module adder (in1, in2, sum);input in1,in2;output [1:0] sum;wire in1,in2;reg [1:0] sum;always @ (in1 or in2)beginsum=in1+in2;endendmodule从这个例子中可以看出,一段完整的代码主要由以下几部分组成:可以了解到一些基本信息,如代码中加法器的主要功能、设计工程师、完成的日期及版本。

例2-1-1的模块名是adder,有两个输入端口in1,in2和一个输出端口sum。

其中,输入信号是一位的,其数据类型声明为连线型(wire);输出是两位的寄存器类型。

verilog_ieee官方标准手册

Verilog是一种硬件描述语言(HDL),是用于电子设计自动化(EDA)的语言之一。

Verilog从20世纪80年代开始发展,最初由Gateway Design Automation 公司开发,后来被Cadence Design Systems收购。

Verilog被广泛应用于数字电路的设计和仿真。

IEEE标准的全称是IEEE Std 1364,是Verilog的官方标准手册。

这个标准由IEEE Verilog标准工作组制定,其中包含了Verilog语言的语法和语义规范。

这个标准包含了3个部分:

1. Verilog语言参考手册:这个部分包含了Verilog语言的语法和语义规范。

其中包含了Verilog的基本语法、数据类型、运算符、控制结构、模块和端口等方面的内容,对于初学者来说非常重要。

2. Verilog模拟器标准接口:这个部分定义了与Verilog编译器和模拟器交互的标准接口。

如果你想自己实现一个Verilog编译器或模拟器,那么这个部分非常重要。

3. Verilog验证标准接口:这个部分定义了与Verilog验证工具交互的标准接口。

如果你想自己实现一个Verilog验证工具,那么这个部分非常重要。

总的来说,IEEE标准是Verilog语言的权威参考,所有的Verilog编译器和模拟器都应该遵循这个标准。

如果你想深入学习Verilog语言,那么这个标准是不可或缺的。

----------------------------------------------------------------------------System task and function系统任务和函数Verilog语言包含一些很有用的系统命令和函数。

用户可以像自己定义的函数和任务一样调用它们。

所有符合IEEE标准的Verilog工具中一定都会有这些系统命令和函数。

CADENCE公司的Verilog 工具中还有另外一些常用的系统任务和函数,它们虽并不是标准的一部分,但在一些仿真工具中也经常见到。

请注意,各种不同的 Veriog 仿真工具可能还会加入一些厂商自己特色的系统任务和函数。

用户也可以通过编程语言接口(PLI)把用户自定义的系统任务和函数加进去,以便于仿真和调试。

所有的系统任务和系统函数的名称(包括用户自定义的系统任务),前面都要加$以区别于普通的任务和函数。

下面是Verilog 工具中常用的系统任务和函数的摘要。

详细资料在后面介绍。

--------------------------------------------------------------------------标准的系统任务和函数Verilog HDL的IEEE标准中包括下面的系统任务和函数:y$display, $monitor, $strobe, $write 等用于把文本送到标准输出和或写入一个或多个文件中的系统任务。

详细说明在后面介绍。

y$fopen 和$fclose$fopen(“FileName”); {Return an integer}$fclose(Mcd);$fopen 是一个系统函数,它可以打开文件为写文件做准备。

而$fclose也是一个系统函数,它关闭由 $fopen 打开的文件。

有关的详细说明在后面介绍。

y$readmemb 和 $readmemh$readmemb(“File”, MemoryName [,StartAddr[,FinishAddr]]);$readmemh(“File”, MemoryName [,StartAddr[,FinishAddr]]);把文本文件中的数据赋值到存储器中。

使用Verilog进行硬件描述硬件描述语言(Hardware Description Language,简称HDL)是专门用于描述数字电路的语言,其中Verilog是一种常用的HDL。

本文将介绍如何使用Verilog进行硬件描述。

一、Verilog简介Verilog是一种硬件描述语言,用于描述和设计数字电路。

它具有丰富的语法和功能,可以灵活地描述各种类型的电路。

Verilog分为Verilog HDL和Verilog-A两种,本文主要介绍Verilog HDL。

二、Verilog的基本语法1. 模块声明Verilog中,通过使用`module`关键字进行模块声明。

模块由输入(Input)、输出(Output)和内部信号(Wire)组成。

例如:```module adder(input a, input b, output sum);// 模块的具体实现endmodule```2. 信号赋值Verilog中,使用`assign`关键字进行信号赋值。

例如:```assign sum = a + b;```3. 运算符Verilog支持各种运算符,包括算术运算符(+、-、*、/)、比较运算符(>、<、==、!=)和逻辑运算符(&&、||、!)。

例如:```assign c = a & b;```4. 时钟信号在Verilog中,时钟信号通常使用`always`关键字进行描述。

例如:```always @(posedge clk)begin// 在时钟上升沿执行的操作end```三、Verilog的应用1. 组合逻辑电路Verilog可以用于描述各种组合逻辑电路,如加法器、多路选择器等。

例如,下面的代码描述了一个4位全加器:```module full_adder(input a, input b, input c_in, output sum, output c_out);assign sum = a ^ b ^ c_in;assign c_out = (a & b) | (b & c_in) | (a & c_in);endmodule```2. 时序逻辑电路Verilog还可以描述时序逻辑电路,如触发器、时钟分频器等。

sv标准手册SV(SystemVerilog)是一种硬件描述语言(HDL),用于设计和验证集成电路。

为了更好地使用和理解SV语言,掌握SV的标准手册是至关重要的。

本文将全面介绍SV标准手册的内容和应用。

一、SV标准手册概述SV标准手册是SV语言的权威指南,为用户提供了详细的语法和语义规范。

其主要分为以下几个部分:1. 语法定义:包括关键字、数据类型、运算符等基本语法元素的定义和用法。

掌握这些基础知识对于编写正确的SV代码至关重要。

2. 模块和接口:介绍了如何使用SV语言构建模块和接口。

模块是SV设计的基本组成单元,而接口则用于模块之间的通信。

手册详细讲解了模块和接口声明、端口连接、模块实例化等内容。

3. 时序建模:探讨了时钟、复位、延迟、事件等时序相关的特性和建模技巧。

理解和应用这些时序建模的知识将使SV设计更加准确和可靠。

4. 并发控制:介绍了多线程和进程控制的方法和机制。

SV提供了丰富的并发控制语法,包括多线程、fork-join模型等。

手册对这些并发控制的技术进行了详细的说明。

5. 断言和覆盖率:讲解了如何使用断言和覆盖率工具进行SV代码的验证。

断言可以用于检测设计中的错误和异常情况,覆盖率工具则用于评估设计测试的完整性。

二、SV标准手册的应用SV标准手册的应用范围非常广泛,下面列举几个典型的应用场景:1. SV学习和教学:对于初学者和教育者来说,SV标准手册是学习SV语言的重要参考资料。

通过学习手册的内容,可以掌握SV的基本语法和使用方法。

2. 开发和调试SV代码:在实际的SV项目中,开发人员经常需要查找和解决代码中的问题。

SV标准手册提供了详细的语法规范和用例,可以帮助开发人员快速定位和解决问题。

3. 验证SV设计:在验证工程师的工作中,SV标准手册是必不可少的工具。

手册中的断言和覆盖率相关内容可以帮助验证工程师设计和执行有效的验证方案。

4. 优化SV代码:为了提高SV代码的性能和效率,开发人员需要了解SV标准手册中的一些高级特性和优化技巧。