硬件描述语言Verilog_HDL基础新

- 格式:ppt

- 大小:1.31 MB

- 文档页数:43

硬件描述语言硬件描述语言(HardwareDescriptionLanguage,HDL),是一种特殊的编程语言,旨在帮助设计人员(称作HDL程序员)创建电子系统的软硬件。

它支持现在最先进的电子系统,并能够提供开发方案,以更快地实现目标,更有效地使用更少的资源,并且更稳定地完成任务。

HDL是一种高级程序设计语言,由若干种编程语言构成,其中包括Verilog,VHDL, SystemVerilog等。

HDL语言描述技术主要用于描述单片机或模拟集成电路(IC)中的复杂电路结构和功能。

它以硬件参数、原语和结构描述为基础,能够描述逻辑系统的底层电路,比如门逻辑、触发器、多路选择器、比较器等。

HDL具有许多优点,能够极大地降低电路设计的困难程度,同时简化设计的复杂性和过程,可以提高设计效率和提升最终产品的性能。

HDL提供方便的调试和测试功能,可以支持电路设计过程管理,减少产品设计和开发的工作量。

此外,HDL能够提供标准、可重用的描述,以及可读性好的语法,可以显著简化设计过程。

HDL的另一个重要优点是,它可以帮助HDL程序员创建更复杂、更现代化的电路设计,而不需要编译器和其它复杂的程序设计开发工具。

HDL可以提供电路设计过程中所需的所有功能,包括定义电路功能,输入输出管理,系统级构建,网络结构,状态机控制,信号处理,数据传输等。

它还利用可视化技术以及带有标准和完善的接口,能够更快地识别和定位问题,大大降低了调试产品的时间。

HDL的另一个优点在于,它具有许多可扩展性,无需为每个项目开发新的硬件。

HDL能够有效地管理工厂现有的系统设计,例如将新的硬件模块添加到已有的电路框架中,并且能够有效地利用已有的硬件,尽可能减少更改硬件布局的时间。

当今,HDL已经成为电子行业中最专业化的编程语言,并被广泛应用于微处理器、嵌入式系统、数字信号处理(DSP)、模拟信号处理(ASP)、网络交换、存储器系统,以及其它领域。

HDL在加速设计过程、改善产品质量、减少产品成本方面十分有用,是现今许多企业进行电子产品设计的重要工具。

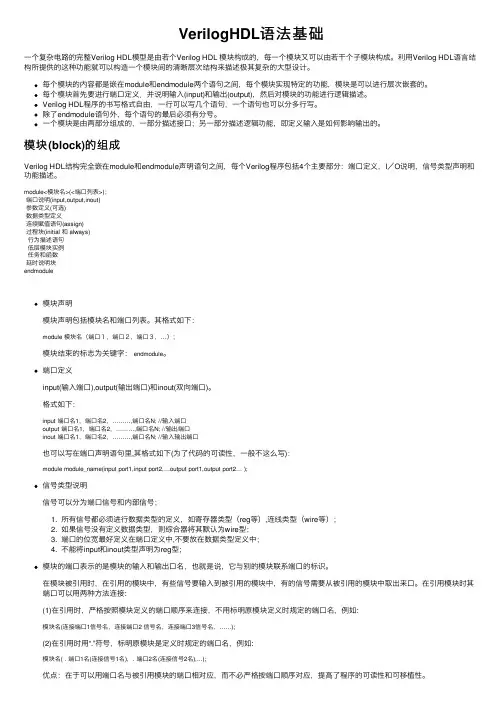

VerilogHDL语法基础⼀个复杂电路的完整Verilog HDL模型是由若个Verilog HDL 模块构成的,每⼀个模块⼜可以由若⼲个⼦模块构成。

利⽤Verilog HDL语⾔结构所提供的这种功能就可以构造⼀个模块间的清晰层次结构来描述极其复杂的⼤型设计。

每个模块的内容都是嵌在module和endmodule两个语句之间,每个模块实现特定的功能,模块是可以进⾏层次嵌套的。

每个模块⾸先要进⾏端⼝定义.并说明输⼊(input)和输出(output),然后对模块的功能进⾏逻辑描述。

Verilog HDL程序的书写格式⾃由,⼀⾏可以写⼏个语句,⼀个语句也可以分多⾏写。

除了endmodule语句外,每个语句的最后必须有分号。

⼀个模块是由两部分组成的,⼀部分描述接⼝;另⼀部分描述逻辑功能,即定义输⼊是如何影响输出的。

模块(block)的组成Verilog HDL结构完全嵌在module和endmodule声明语句之间,每个Verilog程序包括4个主要部分:端⼝定义,I/O说明,信号类型声明和功能描述。

module<模块名>(<端⼝列表>);端⼝说明(input,output,inout)参数定义(可选)数据类型定义连续赋值语句(assign)过程块(initial 和 always)⾏为描述语句低层模块实例任务和函数延时说明块endmodule模块声明模块声明包括模块名和端⼝列表。

其格式如下:module 模块名(端⼝1,端⼝2,端⼝3,…);模块结束的标志为关键字:endmodule。

端⼝定义input(输⼊端⼝),output(输出端⼝)和inout(双向端⼝)。

格式如下:input 端⼝名1,端⼝名2,………,端⼝名N; //输⼊端⼝output 端⼝名1,端⼝名2,………,端⼝名N; //输出端⼝inout 端⼝名1,端⼝名2,………,端⼝名N; //输⼊输出端⼝也可以写在端⼝声明语句⾥,其格式如下(为了代码的可读性,⼀般不这么写):module module_name(input port1,input port2,…output port1,output port2… );信号类型说明信号可以分为端⼝信号和内部信号;1. 所有信号都必须进⾏数据类型的定义,如寄存器类型(reg等),连线类型(wire等);2. 如果信号没有定义数据类型,则综合器将其默认为wire型;3. 端⼝的位宽最好定义在端⼝定义中,不要放在数据类型定义中;4. 不能将input和inout类型声明为reg型;模块的端⼝表⽰的是模块的输⼊和输出⼝名,也就是说,它与别的模块联系端⼝的标识。

hdl硬件描述语言

HDL是Hardware Description Language的缩写,即硬件描述语言。

它是一种用于描述数字电路的语言,包括了数字电路的功能、结构和行为等方面。

HDL 通常用于设计和模拟数字电路,以帮助工程师更好地理解数字电路的功能和性能,并在设计电路时提供一种有效的工具。

在HDL中,通常使用的是高级语言来描述电路的功能和行为,比如Verilog和VHDL。

这些语言提供了一些强大的特性,如模块化设计、层次结构、波形仿真等,使得电路的设计和测试变得更加高效、方便和准确。

HDL的设计流程通常包括以下几个步骤:首先,需要将所需的电路功能转化为模块化的设计,比如将复杂的电路分解为多个子模块;其次,需要使用HDL语言编写每个模块的描述,包括模块端口定义、内部逻辑和功能描述等;接下来,需要进行波形仿真以验证电路的功能和性能;最后,需要将HDL代码转化为实际的硬件电路,比如使用FPGA或ASIC等技术将代码烧入硬件芯片中。

总之,HDL是一种用于描述数字电路的语言,它可以帮助工程师更好地理解和设计数字电路,提高电路设计和测试的效率和准确性。

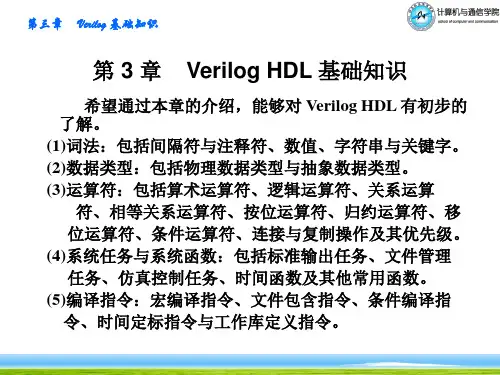

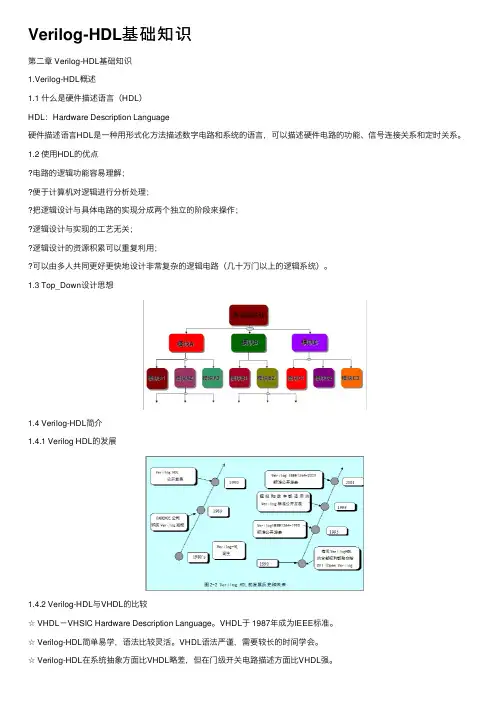

Verilog-HDL基础知识第⼆章 Verilog-HDL基础知识1.Verilog-HDL概述1.1 什么是硬件描述语⾔(HDL)HDL:Hardware Description Language硬件描述语⾔HDL是⼀种⽤形式化⽅法描述数字电路和系统的语⾔,可以描述硬件电路的功能、信号连接关系和定时关系。

1.2 使⽤HDL的优点电路的逻辑功能容易理解;便于计算机对逻辑进⾏分析处理;把逻辑设计与具体电路的实现分成两个独⽴的阶段来操作;逻辑设计与实现的⼯艺⽆关;逻辑设计的资源积累可以重复利⽤;可以由多⼈共同更好更快地设计⾮常复杂的逻辑电路(⼏⼗万门以上的逻辑系统)。

1.3 Top_Down设计思想1.4 Verilog-HDL简介1.4.1 Verilog HDL的发展1.4.2 Verilog-HDL与VHDL的⽐较☆ VHDL-VHSIC Hardware Description Language。

VHDL于 1987年成为IEEE标准。

☆ Verilog-HDL简单易学,语法⽐较灵活。

VHDL语法严谨,需要较长的时间学会。

☆ Verilog-HDL在系统抽象⽅⾯⽐VHDL略差,但在门级开关电路描述⽅⾯⽐VHDL强。

1.4.3 Verilog-HDL 的应⽤ASIC和FPGA设计师可⽤它来编写可综合的代码。

描述系统的结构,做⾼层次的仿真。

验证⼯程师编写各种层次的测试模块对具体电路设计⼯程师所设计的模块进⾏全⾯细致的验证。

库模型的设计:可以⽤于描述ASIC 和FPGA的基本单元(Cell)部件,也可以描述复杂的宏单元(Macro Cell)。

1.4.4 Verilog-HDL的抽象级别⽤Verilog-HDL描述的电路设计就是该电路的Verilog HDL模型,这些模型可以是实际电路的不同级别的抽象,这些抽象的级别和它们对应的模型类型共有以下五种:?系统级(system): ⽤⾼级语⾔结构实现设计模块的外部性能的模型。

VERILOGHDL语⾔基础第1节 Verilog HDL语⾔简介Verilog HDL语⾔简介Verilog HDL和VHDL是⽬前世界上最流⾏的两种硬件描述语⾔(HDL:Hardware Description Language),均为IEEE标准,被⼴泛地应⽤于基于可编程逻辑器件的项⽬开发。

⼆者都是在20世纪80年代中期开发出来的,前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发,后者由美国军⽅研发。

HDL语⾔以⽂本形式来描述数字系统硬件结构和⾏为,是⼀种⽤形式化⽅法来描述数字电路和系统的语⾔,可以从上层到下层来逐层描述⾃⼰的设计思想。

即⽤⼀系列分层次的模块来表⽰复杂的数字系统,并逐层进⾏验证仿真,再把具体的模块组合由综合⼯具转化成门级⽹表,接下去再利⽤布局布线⼯具把⽹表转化为具体电路结构的实现。

⽬前,这种⾃顶向下的⽅法已被⼴泛使⽤。

概括地讲,HDL语⾔包含以下主要特征:* HDL语⾔既包含⼀些⾼级程序设计语⾔的结构形式,同时也兼顾描述硬件线路连接的具体结构。

* 通过使⽤结构级⾏为描述,可以在不同的抽象层次描述设计。

HDL语⾔采⽤⾃顶向下的数字电路设计⽅法,主要包括3个领域5个抽象层次。

* HDL语⾔是并⾏处理的,具有同⼀时刻执⾏多任务的能⼒。

这和⼀般⾼级设计语⾔(例如C 语⾔等)串⾏执⾏的特征是不同的。

* HDL语⾔具有时序的概念。

⼀般的⾼级编程语⾔是没有时序概念的,但在硬件电路中从输⼊到输出总是有延时存在的,为了描述这⼀特征,需要引⼊时延的概念。

HDL语⾔不仅可以描述硬件电路的功能,还可以描述电路的时序。

2.1.1 Verilog HDL语⾔的历史1983年,Gateway Design Automation(GDA)硬件描述语⾔公司的Philip Moorby⾸创了Verilog HDL。

后来Moorby成为Verilog HDL-XL的主要设计者和Cadence公司的第⼀合伙⼈。

《Verilog HDL硬件描述语言》实验教学大纲

课程代码:MICR3001

课程名称:Verilog HDL硬件描述语言

英文名称:Verilog HDL

实验室名称:微电子实验室

课程学时:72实验学时:18

一、本课程实验教学目的与要求

通过实验要求学生掌握用Verilog HDL硬件描述语言进行集成电路设计的流程和方法。

学会使用Max+plusⅡ,QuartusⅡ设计软件,掌握从HDL源代码的输入→编译→仿真→管脚锁定→下载全过程。

学会用ModelSim设计软件,用Verilog HDL编写测试码对设计模块进行仿真。

二、主要仪器设备及现有台套数

PC,现有35台; EDA实验箱,25套;

1、实验报告:有设计代码,仿真结果,管脚排列,验证结果。

2、考核方式:

(1)实验课的考核方式:教师验收评定成绩。

(2)实验课考核成绩:根据实验完成情况和实验报告是否完整确定,实验课成绩占课程总成绩的10%。

五、实验教材、参考书

1、教材:在编

2、参考书:J.Bhasker著,夏宇闻等译《Verilog HDL入门》.北京航空航天大学出版社.2008出版。

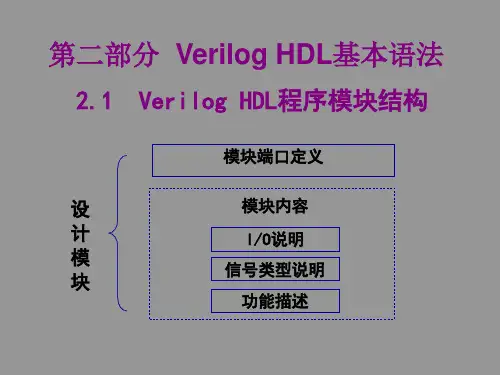

Verilog HDL硬件描述语言2.1 Verilog HDL概述2.1.1 Verilog HDL的特点Verilog HDL和VHDL一样,是目前大规模集成电路设计中最具代表性、使用最广泛的硬件描述语言之一。

作为硬件描述语言,Verilog HDL具有如下特点:1. 能够在不同的抽象层次上,如系统级、行为级、RTL(Register Transfer Level)级、门级和开关级,对设计系统进行精确而简练的描述;2. 能够在每个抽象层次的描述上对设计进行仿真验证,及时发现可能存在的设计错误,缩短设计周期,并保证整个设计过程的正确性;3. 由于代码描述与具体工艺实现无关,便于设计标准化,提高设计的可重用性。

如果有C语言的编程经验,只需很短的时间内就能学会和掌握Verilog HDL,因此,Verilog HDL可以作为学习HDL设计方法的入门和基础。

2.1.2 Verilog HDL的基本结构Verilog HDL描述是由模块(module)构成的,每个模块对应的是硬件电路中的逻辑实体。

因此,每个模块都有自己独立的功能或结构,以及用于与其它模块之间相互通信的端口。

例如,一个模块可以代表一个简单的门,一个计数器,一个存储器,甚至是计算机系统等。

例2-1-1 加法器的verilog描述module adder (in1, in2, sum);input in1,in2;output [1:0] sum;wire in1,in2;reg [1:0] sum;always @ (in1 or in2)beginsum=in1+in2;endendmodule从这个例子中可以看出,一段完整的代码主要由以下几部分组成:可以了解到一些基本信息,如代码中加法器的主要功能、设计工程师、完成的日期及版本。

例2-1-1的模块名是adder,有两个输入端口in1,in2和一个输出端口sum。

其中,输入信号是一位的,其数据类型声明为连线型(wire);输出是两位的寄存器类型。