常用基本数字集成电路-图文

- 格式:docx

- 大小:41.24 KB

- 文档页数:9

常用数字集成电路常用数字集成电路是指在数字电子技术中常用的各种电路,用于实现数字信号的处理、存储和传输。

这些电路广泛应用于计算机、通信、控制系统等领域,是现代数字系统的核心组成部分。

本文将从数字电路的基本组成、常见的数字集成电路和其应用等方面进行阐述。

数字电路由数字元件、数字线路和数字设备组成。

数字元件包括逻辑门、触发器、计数器、移位寄存器等。

逻辑门是实现逻辑运算的基本元件,包括与门、或门、非门等。

触发器是用于存储和传输二进制信息的元件,常见的有RS触发器、D触发器、JK触发器等。

计数器用于计数和计时,常见的有二进制计数器、BCD计数器等。

移位寄存器用于数据的移位和存储,常见的有移位寄存器、移位寄存器等。

常见的数字集成电路包括门电路、触发器电路、计数器电路、显示器电路等。

门电路由逻辑门组成,可以实现与、或、非等逻辑运算。

触发器电路用于存储和传输信息,可以实现时序逻辑功能。

计数器电路可以实现计数和计时功能,广泛应用于时钟、频率分频等领域。

显示器电路用于将数字信号转化为可视化的信号,常见的有数码管显示器、液晶显示器等。

数字集成电路在各个领域有着广泛的应用。

在计算机中,数字集成电路用于实现中央处理器、存储器、输入输出设备等。

在通信系统中,数字集成电路用于实现编解码器、调制解调器、数字滤波器等。

在控制系统中,数字集成电路用于实现控制器、传感器、执行器等。

数字集成电路的应用使得数字系统具备了高速、高精度、高可靠性的特点。

总结起来,常用数字集成电路是数字电路中的重要组成部分,用于实现数字信号的处理、存储和传输。

它们由数字元件、数字线路和数字设备组成,包括逻辑门、触发器、计数器、移位寄存器等。

常见的数字集成电路有门电路、触发器电路、计数器电路、显示器电路等。

它们在计算机、通信、控制系统等领域有着广泛的应用。

数字集成电路的发展使得数字系统具备了高速、高精度、高可靠性的特点,推动了数字技术的不断进步。

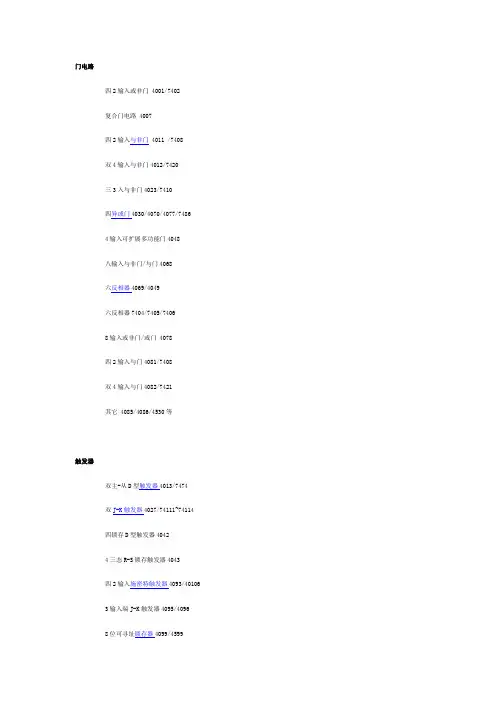

门电路四2输入或非门 4001/7402复合门电路 4007四2输入与非门 4011 /7408双4输入与非门4012/7420三3入与非门4023/7410四异或门4030/4070/4077/74864输入可扩展多功能门4048八输入与非门/与门4068六反相器4069/4049六反相器7404/7405/74068输入或非门/或门 4078四2输入与门4081/7408双4输入与门4082/7421其它 4085/4086/4530等触发器双主-从D型触发器4013/7474双J-K触发器4027/74111~74114四锁存D型触发器40424三态R-S锁存触发器4043四2输入施密特触发器4093/401063输入端J-K触发器4095/40968位可寻址锁存器4099/4599六锁存D型触发器40174/40175双4位锁存D型触发器 4508六锁存D型触发器74174/741758D锁存器74273/74373时基延时分频电路通用定时电路555无稳态/单稳态多谐振荡器4047“N”分频计数器4059二进制比例乘法器 408924级分频器4521BCD比例乘法器4527单稳态多谐振荡器74121~74123单稳态多谐振荡器74221其它 MM5369/MN6041/MC14451计数器脉冲分配器/计数器 4017、4022二进制串行计数器 4020、4024、4040、4060;74161、74162、74163;可预置4位二进制/BCD加减计数器 4029可预置4位BCD/二进制计数器40161、40162、40163;可预置4位可逆计数器40192、40193;74190-74193可预置4位可逆计数器4510、4516双4 位BCD/二进制同步加计数器4518、4520可预置同步1/N计数器 4522、4526BCD计数器7490、74196译码器BCD-十进制译码器4028BCD-7段译码/液晶驱动器4055/4056BCD- 7段译码驱动器4511/45474线-16线译码器4514/4515/74154BCD-七段锁存译码,驱动器4543/4544/4558双二进制四选一译码器/分离器4555/4556三位BCD计数器译码器4553BCD-七段锁存译码,驱动器7447~7449双二-四线译码器74139BCD- 7段译码驱动器74141/74142模拟开关数据选择器四与或选择器4019八选一模拟开关4051双4选1模拟开关4052三组二路模拟开关4053四传输门4016/406616选1模拟开关4067双路八选一模拟开关4097八路数据选择器 4512双四路/单八路模拟开关4529寄存器18位串入/串出移位寄存器40068位串入/并入-串出移位寄存器4014双4位串入/并出移位寄存器40154位并入/串入-并出/串出移位寄存40354位并入/串入-并出/串出移位寄存40194/40195/74194/741954位移位寄存7494运算电路通用运算放大器LM3244电压比较器LM3934位超前进位全加器40084位数值比较器4585/4063编码电路编译码配对电路音调解码器LM5678位优先编码器4532/7434810-4线编码器40147/741478-8线优先编码器74147/74149编译码配对电路MC145026/45027/45028/45030编译码配对电路PT2262/2272编译码配对电路PT2248/2249/2250编译码配对电路VD5012/5013/5014编译码配对电路VD5102/5103/5104编译码配对电路VD5026/5027/5028遥控电路遥控配对电路BA5104/5204遥控配对电路MC14457/14458遥控配对电路TC9148/9149/9150频率合成电路锁相环频率合成4046锁相环频率合成MC145152/45156锁相环频率合成MC145146点线显示驱动器LM3914/3915大功率反相驱动器ULN20039011 NPN 30V 30mA 400mW 150MHz 放大倍数20-80 9012 PNP 50V 500mA 600mW 低频管放大倍数30-909013 NPN 20V 625mA 500mW 低频管放大倍数40-1109014 NPN 45V 100mA 450mW 150MHz 放大倍数20-908050 NPN 25V 700mA 200mW 150MHz 放大倍数30-1008550 PNP 40V 1500mA 1000mW 200MHz 放大倍数40-140详情如下:90系列三极管参数90系列三极管大多是以90字为开头的,但也有以ST90、C或A90、S90、SS90、UTC90开头的,它们的特性及管脚排列都是一样的。

几种常见集成电路的电路结构图及说明本文简单介绍了四种基本集成电路。

数字电路数字电路处理的是离散的非连续的电信号(称为数字信号)。

研究数字电路就是要研究数字信号的产生,放大、整形、传送、控制、记忆和计数等问题。

数字电路主要有以下两个特点:第一,数字电路的工作信号是不连续的数字信号,它在电路中只表现为信号的有、无或电平的高,低。

所以,数字电路中的晶体管多工作在开关状态,即晶体管要么是"饱和",要么是"截止",而"放大"只是过渡状态。

由于数字电路工作时只要求能可靠地判别信号的有、无或电平的高、低两种状态,因此电路对精度的要求不高,适于集成化。

第二,数字电路研究的对象是电路的输出与输入之间的逻辑关系,其处理的主要波形如下图:模拟电路模拟电路是研究在时间上数值大小其过程是连续的一种物理量。

主要应用在完成信号放大处理的驱动终端负载等领域。

主要方法是工作点的设置。

工具有图解法及结算法。

通过对模拟电路的设计又以完成对各种信号的处理需求:如宇宙飞船发回的信号进行数万倍的放大,其要处理波形如下图:微分电路电路结构如图,微分电路可把矩形波转换为尖脉冲波,此电路的输出波形只反映输入波形的突变部分,即只有输入波形发生突变的瞬间才有输出。

而对恒定部分则没有输出。

输出的尖脉冲波形的宽度与R*C有关(即电路的时间常数),R*C越小,尖脉冲波形越尖,反之则宽。

此电路的R*C必须远远少于输入波形的宽度,否则就失去了波形变换的作用,变为一般的RC耦合电路了,一般R*C少于或等于输入波形宽度的1/10就可以了。

积分电路电路结构如图,积分电路可将矩形脉冲波转换为锯齿波或三角波,还可将锯齿波转换为抛物波。

电路原理很简单,都是基于电容的冲放电原理,这里就不详细说了,这里要提的是电路的时间常数R*C,构成积分电路的条件是电路的时间常数必须要大于或等于10倍于输入波形的宽度。

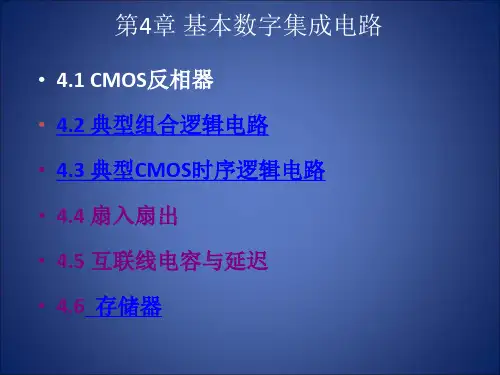

§4-2 集成门电路

常用的数字集成电路: 分为两大类

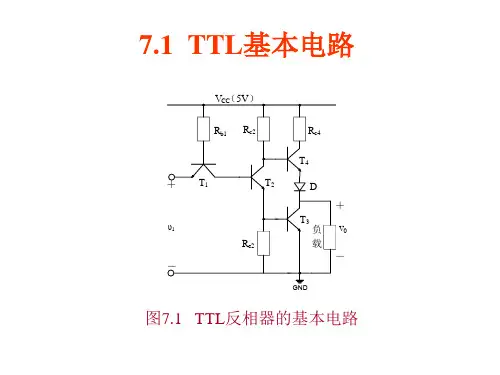

※TTL(Transistor-Transistor Logic)

晶体管-晶体管逻辑电路

分为:74、74H、74S、74LS、74AS和74ALS系列※CMOS(Complementary Metal-Oxide Semiconductor)

互补的金属氧化物半导体电路

分为:4000、HC(HCT) 、AC(ACT)等系列

第4章组合逻辑电路

五、CMOS数字集成电路简介

CMOS集成电路具有功耗低、抗干扰能力强等突出优点。

高速和超高速系列CMOS产品中大部分器件的逻辑功能和引脚排列与LS系列TTL电路兼容。

CMOS集成电路与TTL集成电路相比具有以下特点:(1)功耗低

(2)电源电压范围宽

(3)输出逻辑电平摆幅大

(4)抗干扰能力强,噪声容限大

(5)输入阻抗高,扇出系数大

(6)温度稳定性好,工作温度范围宽

第4章组合逻辑电路。

常用基本数字集成电路-图文1常用基本数字集成电路概述数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。

根据数字集成电路中包含的门电路或元、器件数量,可将数字集成电路分为小规模集成(SSI)电路、中规模集成MSI电路、大规模集成(LSI)电路、超大规模集成VLSI电路和特大规模集成(ULSI)电路。

小规模集成电路包含的门电路在10个以内,或元器件数不超过100个;中规模集成电路包含的门电路在10~100个之间,或元器件数在100~1000个之间;大规模集成电路包含的门电路在100个以上,或元器件数在10~10个之间;超大规模集成电路包含的门电路在1万个以上,或元器件数在10~10之间;特大规模集成电路的元器件数在10~10之间。

2门电路构成的多谐振荡器的基本原理非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。

电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT时,门的输出状态即发生变化。

因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。

2.1不对称多谐振荡器非对称型多谐振荡器的输出波形是不对称的,当用TTL与非门组成时,输出脉冲宽度tw1=RC,tw2=1.2RC,T=2.2RC调节R和C值,可改变输出信号的振荡频率,通常用改变C实现输出频率的粗调,改变电位器R实现输出频率的细调。

2.1.2对称型多谐振荡器电路完全对称,电容器的充放电时间常数相同,故输出为对称的方波。

改变R和C的值,可以改变输出振荡频率。

非门3用于输出波形整形。

一般取R≤1KΩ,当R1=R2=1KΩ,C1=C2=100pf~100μf时,f可在几Hz~MHz变化。

脉冲宽度tw1=tw2=0.7RC,T=1.4RC.2.1.3门电路多谐振荡器仿真图3非门内部电路图4不对称多谐振荡器2图5对称多谐振器3555定时器构成的多谐振荡器3.1555定时器(1)基本原理及其组成由电阻分压器、电压比较器、基本RS触发器、输出缓冲反相器、集电极开路输出三极管组成。

其内部结构如图(A)及管脚排列如图(B)所示。

A∞A∞3.2用555定时器组成多谐振荡器工作原理:1)电路第一暂态,输出为1。

电容充电,电路转换到第二暂态,输出为02)电路第二暂稳态,电容放电,电路转换到第一暂态。

3图5用555定时器组成多谐振荡器的原理图工作波形与振荡频率计算:tPL=R2C1n2≈0.7R2CtpH=(R1+R2)C1n2≈0.7(R1+R2)Cf11.43tPLtPH(R12R2)CvC2V3CC1V3CCOvOtR1R2vCCVCC8473555651v0.01FtPLOtPHt3.3用555定时器组成占空比可的调多谐振荡器tpH=RAC1n2≈0.7RACtPL=RBC1n2≈0.7RBCRAtpH11.43tpL(RARB)CVCCR1R27D1628555143vOfRBR3vC+CD2-50.01F4Aq(%)100%RARBR3.4555振荡器仿真555芯片构成的如图9所示。

输出脉冲波的高电平持续时间TW1=0.7(R1+R2)C1.图9555多谐振荡器555多谐振荡器电路的仿真结果:54N进制计数器(1)计数器概述计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器可以用来显示产品的工作状态,一般来说主要是用来表示产品已经完成了多少份的折页配页工作。

它主要的指标在于计数器的位数,常见的有3位和4位的。

很显然,3位数的计数器最大可以显示到999,4位数的最大可以显示到9999。

(2)计数器原理分析与设计参数计算计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,6同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等计数器按计数进制不同,可分为二进制计数器、十进制计数器、其他进制计数器和可变进制计数器,若按计数单元中各触发器所接收计数脉冲和翻转顺序或计数功能来划分,则有异步计数器和同步计数器两大类,以及加法计数器、减法计数器、加/减计数器等,如按预置和清除方式来分,则有并行预置、直接预置、异步清除和同步清除等差别,按权码来分,则有“8421”码,“5421”码、余“3”码等计数器,按集成度来分,有单、双位计数器等等,其最基本的分类如下:同步计数器1、结构异步计数器计数器的种类加法计数器2、功能减法计数器可逆计数器二进制计数器3、进制十进制计数器N进制计数器1、用D触发器构成异步二进制加/减计数器图3.8.1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D触发器接成T'触发器,再由低位触发器的Q端和高一位的CP端相连接。

图3.8.1四位二进制异步加法计数器72、中规模集成计数器74LS161是四位二进制可预置同步计数器,由于它采用4个主从JK触发器作为记忆单元,故又称为四位二进制同步计数器,其集成芯片管脚如图3.8.2所示管脚符号说明Vcc:电源正端,接+5VR:异步置零(复位)端DCP:时钟脉冲LD:预置数控制端A、B、C、D:数据输入端QA、QB、QC、QD:输出端RCO:进位输出端图3.8.274LS161管脚图该计数器由于内部采用了快速进位电路,所以具有较高的计数速度。

各触发器翻转是靠时钟脉冲信号的正跳变上升沿来完成的。

时钟脉冲每正跳变一次,计数器内各触发器就同时翻转一次,74LS161的功能表如表3.8.1所示:表3.8.174LS161逻辑功能表输入RD输出B某b某某某C某c某某某D某d某某某QALaQBLbQCLcQDLdLDET某某HL某EP某某H某LCP某A某a某某某LHHHH 某LHHH计数保持保持某某83、计数器的级联使用若所要求的进制已超过16,则可通过几个74LS161进行级联来实现,在满足计数条件的情况下有如下方法:1)同步联接法:CP是共同的,只是把第一级的进位输出RCO接到下一级的ET端即可,平时RCO=0则计数器2不能工作,当第一级计满时,RCO=1,最后一个CP使计数器1清零,同时计数器2计一个数,这种接法速度不快,不论多少级相联,CP的脉宽只要大于每一级计数器延迟时间即可。

其框图如图3.8.32)异步联接法:把第一级的进位输出端RCO接到下一级的CP端,平时RCO=0则计数器2因没有计数脉冲而不能工作,当第一级计满时,RCO=1,计数器2产生第一个脉冲,开始计第1个数,这种接法速度慢,若多级相联,其总的计数时间为各个计数器延迟时间之和。

其框图如图3.8.4所示图3.8.3同步联接法框图图3.8.4异步联接法框图4、实现任意进制计数器由于74LS161的计数容量为16,即计16个脉冲,发生一次进位,所以可以用它构成16进制以内的各进制计数器,实现的方法有两种:置零法(复位法)和置数法(置位法)。

(1)用复位法获得任意进制计数器假定已有N进制计数器,而需要得到一个M进制计数器时,只要M<N,用复位法使计数器计数到M时置“0”,即获得M进制计数器。

(2)利用预置功能获M进制计数器置位法与置零法不同,它是通过给计数器重复置入某个数值的的跳越N-M个状态,从而获得M进制计数器的,如图所法。

置数操作可以在电路的任何一个9状态下进行。

这种方法适用于有预置功能的计数器电路。

图3.8.5为上述二种方法的原理示意图例如:利用两片十进制计数器74LS161接成35进制计数器?本例可以采用整体置零方式进行。

首先将两片74LS161以同步级联的方式接成16某16=256进制的计数器。

当计数器从全0状态开始计数时,计入了35个脉冲时,经门电路译码产生一个低电平信号立刻将两片74LS161同时置零,于是便得到了35进制计数器。

电路连接图如图3.8.6所示SN-3SSM-2SN-1SN-1SM-2Si+2S0S1S2S3S0S1Si+1SN-2SN-2SN-3(b)SjSj-1(a)3.8.5获得任意进制计数器的两种方法(a)置零法(b)置数法图3.8.6二片74LS161构成35进制计数器电路连接图5.3仿真电路由三位的十进制计数器74LS160构成0—999的计数器,K1为计数时钟按钮,每按下一次,产生一个计数时钟,K2为异步清零时钟。

10图120—999的计数器仿真结果:5总结在做实验前,一定要将课本上的知识吃透,因为这是做实验的基础,否则,在老师讲解时就会听不懂,这将使你在做实验时的难度加大,浪费做实验的宝贵时间.做实验时,一定要亲力亲为,务必要将每个步骤,每个细节弄清楚,弄明白,实验后,还要复习,思考,这样,你的印象才深刻,记得才牢固,否则,过后不久你就会忘得一干二净,这还不如不做.老师将一些课本上没有的知识教给我们,拓宽我们的眼界,使我们认识到这门课程在生活中的应用是那么的广泛.通过这次测试技术的实验,使我学到了不少实用的知识,更重要的是,做实验的过程,思考11问题的方法,这与做其他的实验是通用的,真正使我们受益匪浅.在实验的过程中我们要培养自己的独立分析问题,和解决问题的能力。

培养这种能力的前题是你对每次实验的态度。

如果你在实验这方面很随便,抱着等老师教你怎么做,拿同学的报告去抄,尽管你的成绩会很高,但对将来工作是不利的。

比如在做回转机构实验中,经老师检查,我们的时域图波形不太合要求,我首先是改变振动的加速度,发现不行,再改变采样频率及采样点数,发现有所改善,然后不断提高逼近,最后解决问题,兴奋异常。

在写实验报告,对于思考题,有很多不懂,于是去问老师,老师的启发了我,其实答案早就摆在报告中的公式,电路图中,自己要学会思考。

(六)参考文献1、数字电子技术基础(阎石主编)2、集成电路原理及应用(钱为康编)3、电子技术课程设计(杨志忠等编)4、TTL集成电路设计手册12。