第六章 微处理器8086的总线结构和时序PPT课件

- 格式:ppt

- 大小:452.00 KB

- 文档页数:18

8086微处理器的功能与结构四、80x86微处理器的结构和功能(一)80x86微处理器1.8086/8088主要特征(1)16位数据总线(8088外部数据总线为8位)。

(2)20位地址总线,其中低16位与数据总线复用。

可直接寻址1MB存储器空间。

(3)24位操作数寻址方式。

(4)16位端口地址线可寻址64K个I/O端口。

(5)7种基本寻址方式。

有99条基本指令。

具有对字节、字和字块进行操作的能力。

(6)可处理内部软件和外部硬件中断。

中断源多达256个。

(7)支持单处理器、多处理器系统工作。

2.8086微处理器内部结构8086微处理器的内部结构由两大部分组成,即执行部件EU(Execution Unit)和总线接口部件BIU(Bus Interface Unit)。

和一般的计算机中央处理器相比较,8086的EU相当于运算器,而BIU则类拟于控制器。

3.8086最小模式与最大模式及其系统配置最小模式在结构上的特点表现为:系统中的全部控制信号直接来自8086CPU。

与最小模式相比,最明显的不同是系统中的全部控制信息号不再由8086直接提供,而是由一个专用的总线控制器8288输出的。

4.8087与8089处理机简述(1)8087协处理机8087协处理机与8086组合在一起工作,以弥补8086在数值运算能力方面的不足,所以它又称为协处理机。

(2)8089I/O处理机8089是一个带智能的I/O接口电路,相当于大型机中的通道,它将CPU的处理能力与DMA控制器结合在一起。

它具有52条基本指令,1MB的寻址能力,包含两个DMA通道。

8089也可以与8086联合在一起工作,执行自己的指令,进行I/O 操作,只在必需时才与8086进行联系。

在8089的控制下,可以进行外设与存储器之间、存储器与存储器之间以及外设与外设之间的数据传输。

同时,8089还可以设定多种终止数据传输的方式。

5.总线时序一个基本的总线周期包括4个时钟周期,即4个时钟状态T 1 、T2 、T3 和T4 。

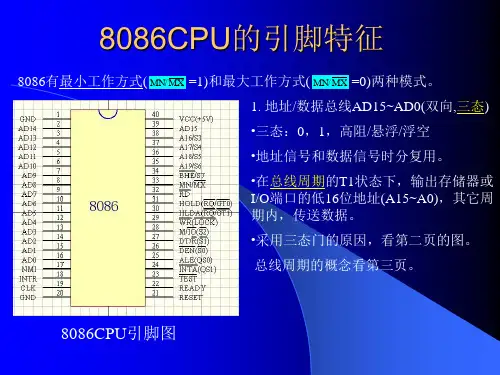

第五讲8086/8088微处理器引脚功能、总线结构和时序第一节、8086/8088引脚信号和功能第二节、8086/8088最小模式和最大模式第三节、8086/8088主要操作第四节、8086存储器的分体结构第一节8086/8088引脚信号和功能一、8086/8088的两种工作模式二、8086/8088引脚信号和功能一、8086/8088的两种工作模式8086/8088CPU有两种模式:最小模式和最大模式。

y最小模式系统中只有8086/8088一个微处理器(单处理器模式)。

所有的总线控制信号都直接由8086/8088产生。

总线控制逻辑电路被减少到最小。

适合于较小规模的系统。

y最大模式包含两个(以上)微处理器,其中一个主处理器是8086/8088,其他的处理器称为协处理器,协助主处理器工作。

适合于中等规模或大型的8086/8088系统中。

系统的控制总线由总线控制器8288来提供:¾8288增强了8088CPU总线的驱动能力;¾将8086的状态信号(S2~S0)进行译码,提供8086对存储器、I/O接口进行控制所需的信号。

最小模式与最大模式的主要区别8086/8088外部引脚图(括号内为最大模式时引脚名)8088地A14A13A12A11A10A9A8AD7AD6AD5AD4AD3AD2AD1AD0NMI INTR CLK 地Vcc(5V)A15A16/S3A17/S4A18/S5A19/S6SS0(HIGH)MN/MX RDHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LOCK M/IO DT/R(S1)DEN(S0)ALE(QS0)INTA(QS1)TEST READY RESETVcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086(1)地址/数据复用引脚(AD15~AD0 )是分时复用①在总线周期来输出要访问的存储器地址或口地址A15~A②在总线周期的其他时间内,作为双向数据总线:对8086就是(对8088地AD14AD13Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MXRDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TESTREADYRESET8861.两种模式下公共引脚(2) 地址/状态复用引脚A19/S6~ A16/S3分时复用引脚,输出,三态。

第6章 微处理器8086的总线结构和时序6.1 学习指导本章是本课硬件部分的开始。

硬件部分不太容易接受,但却是理解微机工作原理的关键。

只有搞懂了几个主要硬件部分的工作原理,再结合第三章的微处理器的功能结构及其与存储器的组织,综合理解,方可真正体会出复杂的微机工作原理。

本章是在第三章的基础之上再进一步介绍8086微处理器的总线结构和时序,从而可完整地了解微处理器的工作原理。

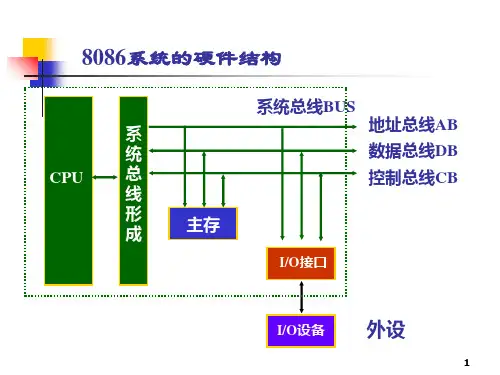

主要有两大部分内容:1. 8086引脚定义和系统总线结构2. 8086的系统总线时序每一部分又从最大系统和最小系统两个方面来介绍,其中最小系统是重点,最大系统可通过与最小系统比较异同来掌握。

具体要求搞懂并记住重点信号如RESET、RD、WR、ALE、DEN、DT/R、M/IO、READY等,并学会构成系统总线;时序中的读、写时序是重点,在学会画的同时,要结合总线结构理解微处理器执行一条指令的过程,即微处理器的工作原理。

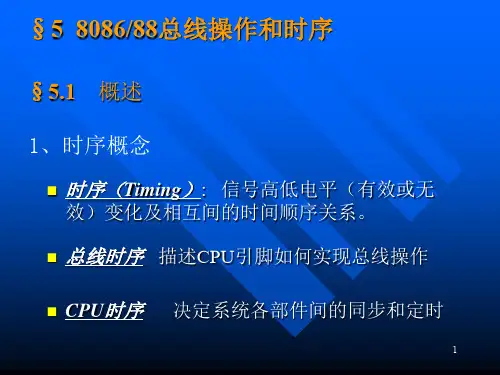

6.2 补充知识1.部分概念小结:一个时钟周期:控制微处理器工作的时钟信号的一个周期(一负脉冲与一正脉冲的时间和)。

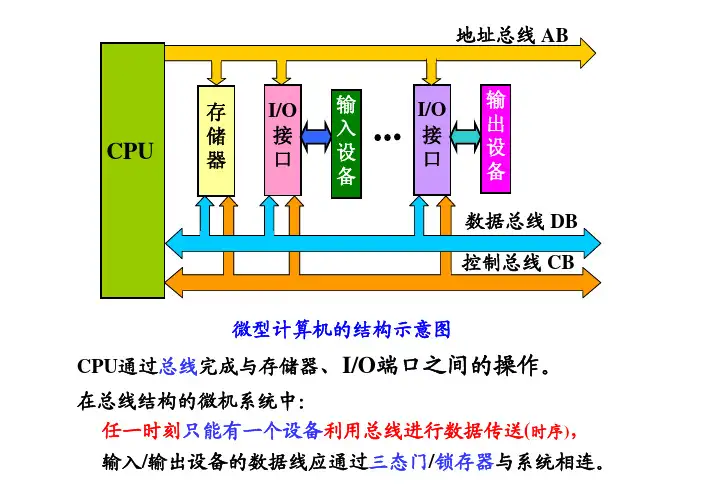

一个总线周期:8086CPU通过总线对外部(存储器或I/O接口)进行一次访问所需的时间。

一个指令周期:CPU执行某一条指令所需的时间(包括取指令的总线周期和执行指令所代表的具体操作所需的时间)。

一个基本的总线周期包括4个时钟周期,即T1、T2、T3和T4,又称为4个T状态。

读写总线周期在这4个T状态下完成的工作是不同的,于是就有了读总线周期和写总线周期。

一个实际的总线周期除4个T状态外还可能在T3和T4之间插入若干个等待周期Tw。

典型的总线周期是在CPU的BIU需要取指令来填补指令队列的空缺或当EU在执行指令过程中需要申请一个总线周期时,BIU才会进入执行总线周期的工作状态。

处于两个总线周期之间可能存在若干的空闲状态,简称T1状态。

2.P230页的图6.11中断响应周期时序中,要注意CPU是从数据总线AD7~AD0上读入接受中断响应的接口提供的中断类型码的。