DDR3走线规则

- 格式:pdf

- 大小:1.30 MB

- 文档页数:32

DDR3布局布线规则与实例DDR3 布局布线译自飞思卡尔官方文档Hardware Development Guidefor i.MX 6Quad, 6Dual,6DualLite, 6Solo Families of Applications ProcessorsIMX6 Serial Layout Recommendations2 / 343 / 344 / 341.DDR 原理性连接框图图 1、图 2 为 I.MX6DQ/SDL 与 DDR 连接框图,连接示意一目了然。

图 1 DDR3 与 i.MX6DQ/SDL 连接示意图5 / 34图 2 LPDDR2 与 i.MX6DQ/SDL 连接示意图2.DDR 布局布线规则DDR3 在布线中十分重要,它必须考虑阻抗匹配问题,通常单端为 50Ω,差分 100Ω。

图 3 给出了 DDR 及其去耦电容的最终布局,其中左图是顶层布局,右图为底层布局,共计 4 片 DDR3 芯片,顶层、底层各两片。

DDR 应该尽量靠近 CPU,这样可以减小寄生参数和传播延时。

6 / 34图 3 DDR 和去耦电容的布局DDR3 的有两种布线形式:一种是所有信号线等长,另一种是以字节为单位分组等长。

所有信号线等长布线,该种布线方式在信号完整性上是最理想的,在设置约束规则上是简单的,但由于布线空间,使得这种方法耗时费力,甚至设计无法实现,在此只是提及一下,并不推荐使用该种方法。

各信号线布线长度要求如表 1 所示。

表 1 所有信号线等长的布线方式7 / 34以字节为单位分组等长布线,该种布线方式以“小组”为单位作等长处理,实际工程当中等长处理容易实现,但是这种方式约束规则较为复杂,毕竟每“小组”都需要一个约束规则。

表 2 给出了以字节为单位分组等长布线要求。

表 2 以字节为单位分组等长8 / 349 / 341. Clock(min): Clock 的最短长度,因为它有一个±5mil 的容差最后,还有一个需要注意的是阻抗匹配问题,推荐单端 50Ω,差分 100Ω。

DDR3DIMM布线约束总结1.总体约束DDR3 DIMM在布线过程中,根据其工作频率的不同,布线要求将有所降低。

各种电源的布线要求请参考DDR3 DIMM的控制器件(如DSP、ARM、CPU或FPGA)的具体要求。

不同信号线的特征阻抗也会随着不同的控制芯片、不同的工作频率有所不同。

比如,Altera的FPGA要求单端信号线阻抗50欧姆,差分信号线阻抗100欧姆;而Xilinx的FPGA要求单端信号线阻抗在低工作频率下为50欧姆,高工作频率下为40欧姆(1333Mb/s及以上);差分信号线阻抗在低工作频率下为100欧姆,高工作频率下为80欧姆(1333Mb/s及以上)。

以下主要总结走线长度约束。

1)同一组DQS/DQS#、DQ、DM之间的布线延时控制在±5ps以内,比如DQS0/DQS0#、DQ0~7、DM0之间控制在±5ps以内。

2)CK/CK#和所有的地址、命令、控制线之间的延时控制在±25ps 以内。

3)CK/CK#的布线延时必须大于任何DQS/DQS#的延时。

4)最大的DQS及其对应CK的总延时,减去最小的DQS及其对应CK的总延时必须小于1个CK时钟周期。

5)同一组DQS、DQ和DM在同一层走线。

6)CK和CKE远离地址线。

7)地址命令控制线远离DQS、DQ和DM线。

8)DQ/DQS/DM布线时需参考GND平面。

9)时钟、控制、地址和命令线在布线时需参考电源平面,如1.5V 或1.35V。

其他注意事项,如单端信号线、差分信号线的布线方法遵循高速信号线的布线要求即可。

2.补充说明针对第3、4条约束,需要做进一步说明。

当使用DIMM时,数据及选通信号(DQ/DQS/DM)、时钟线和地址控制命令线的布线长度需考虑DIMM本身的布线延时。

以RAW CARD A类DIMM为例,其时钟线和地址控制命令线到每个颗粒的布线延时是基本相等的,在DIMM上都进行了正确的补偿。

DDR布线规范1、DDR3管脚定义》CK/CK# 全局差分时钟,所有控制和地址输⼊信号在CK上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQS、DQS#)参考与CK 和CK#的交叉点。

》CKE为时钟使能信号,使能(⾼)和禁⽌(低)内电路和DRAM上的时钟。

由DDR3 SDRAM配置和操作模式决定特定电路被使能和禁⽌。

CKE为低时,提供预充电和⾃刷新操作(所有Bank都处于空闲),或有效掉电(在任何Bank⾥的⾏有效)。

CKE与掉电状态的进⼊、退出以及⾃刷新的进⼊同步。

CKE与⾃刷新的退出异步,输⼊Buffer(除了CKE、CK#、RESET#和ODT)在掉电期间被禁⽌。

输⼊Buffer(除了CKE和RESET#)在⾃刷新期间被禁⽌。

CKE的参考值是VREFCA。

》CS#为⽚选信号,使能(低)和禁⽌(⾼)命令译码,⼤部分CS#为⾼时,所有命令被屏蔽、CS#提供了多Bank系统的Bank选择功能,CS#是命令代码的⼀部分,CS#的参考值是VREFCA。

》ODT⽚上终端使能。

ODT使能(⾼)和禁⽌(低)⽚内终端电阻,在正常操作使能时,ODT仅对下⾯的引脚有效:DQ[7:0]、DQS、DQS#和DM。

如果通过LOAD MODE命令禁⽌,OTD输⼊被忽略。

OTD的参考值是VREFCA。

》BA0、BA1、BA2为BANK地址输⼊,⽤来确定当前的命令操作对哪个BANK有效。

BA[2:0]定义在LOAD MODE命令器件哪个模式(MR0、MR1、MR2)被装载,BA[2:0]的参考值是VREFCA.》A0~A9、A10/AP、A11、A12/BC#、A13为地址总线,为有效命令提供⾏地址,同时为读、写命令提供列地址和⾃动预充电位(A10),以便从某个Bank的内存阵列⾥选出⼀个位置。

LOAD MODE命令器件,地址输⼊提供⼀个操作码。

地址输⼊的参考值是VRECA。

A12/BC#是在模式寄存器(MR)使能时,A12在读和写命令期间被采样,已决定burst chop(on-the-fly)是否被执⾏(HIGH=BL8执⾏burst chop)或者LOW-BC4不执⾏burst chop。

DDR3布线技巧DDR3布线技巧DDR3是电子系统中极其重要的一种芯片。

它可以在时钟线的上升沿和下降沿分别对数据进行读取操作。

故有着很高的读写速率。

但正是这高速的读写速率是的DDR3的系统在布局布线上有着很高的要求。

正确的布局布线不仅可以使的DDR3存储系统可以正常的工作。

并且可以很大程度上减少电磁干扰。

下面是一些关于DDR3的布线规则和建议:1:最少三层信号线,最好四层2:使用FBGA封装的DDR器件,要求DQ,DQS,DM和时钟信号线以Vss为参考。

地址,命令,控制线以VDD为参考。

为了保证良好的电源供电,通常的方法是在PCB外层信号层铺上VDD。

3:减小信号返回路径的长度,减小传输电流和电磁辐射。

Micron要求把Vdd和Vss相邻近放置。

4:Vref的建议:低电感去耦电容离Vref引脚越近越好。

Vref的线越粗短越好。

为了减少耦合,Vref离信号线最少2cm。

5:对于轻载,(小于四个DDR3器件)可以通过简单的电阻分压产生Vref。

这样Vref可以跟踪到VddQ的任何电压变化。

6:对于器件非常多,负载特别重的情况下。

用一个电源IC就可以了。

常用的DDR3比如Micron成功的使用了很多内置MOSFET的开关电源。

7:这些电源可以为VTT电路提供3A的电流,并且有一个独立的线性的可提供3ma的Vref。

8:ref设计准则:最小20-25mil宽,以减小线上的电感。

和其他邻近的信号线最少有15-25mil 的间距。

Vref和VddQ之间放置0.1uf的去耦电容。

Vref和VssQ之间放置0.1uf的去耦电容。

放置去耦电容以去耦。

9:在设计DDR存储器的时候,电源需要认真的考虑。

因为DDR需要3个精准的电压。

1:VddQ,Vtt和Vref。

VTT是存储器总线端接电压所需电压值是VddQ/2.10:VDD和VDDQ有着很高的电流,用于给DDR内核和器件的IO口供电。

Vref大小为Vdd的一半,用于和DDR内部信号做比对。

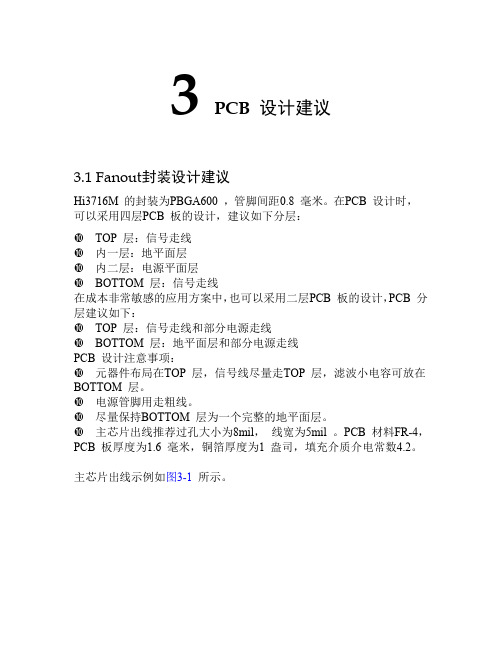

3 PCB 设计建议3.1 Fanout封装设计建议Hi3716M 的封装为PBGA600 ,管脚间距0.8 毫米。

在PCB 设计时,可以采用四层PCB 板的设计,建议如下分层:❿ TOP 层:信号走线❿ 内一层:地平面层❿ 内二层:电源平面层❿ BOTTOM 层:信号走线在成本非常敏感的应用方案中,也可以采用二层PCB 板的设计,PCB 分层建议如下:❿ TOP 层:信号走线和部分电源走线❿ BOTTOM 层:地平面层和部分电源走线PCB 设计注意事项:❿ 元器件布局在TOP 层,信号线尽量走TOP 层,滤波小电容可放在BOTTOM 层。

❿ 电源管脚用走粗线。

❿ 尽量保持BOTTOM 层为一个完整的地平面层。

❿ 主芯片出线推荐过孔大小为8mil,线宽为5mil 。

PCB 材料FR-4,PCB 板厚度为1.6 毫米,铜箔厚度为1 盎司,填充介质介电常数4.2。

主芯片出线示例如图3-1 所示。

图3-1 主芯片出线示例图3.2 DDR SDRAM接口电路设计建议Hi3716M 内部集成了32 位宽的DDR2//DDR3 兼容接口控制器。

3.2.1 DDR2 接口设计DDR2 SDRAM 容量要求为256MB 时,DDR2 接口推荐外接2 片16bit 数据位宽的DDR2 SDRAM 颗粒;两个16bit 数据位宽的数据总线DDRA_DQ[0:15]和DDRB_DQ[0:15]拼成一个32bit 数据位宽的数据总线。

DDRB_DQ[0:15]对应32bit 位宽数据总线DQ[16:31]。

容量要求为512MB 时,DDR2 接口推荐外接4 片8bit 位宽的DDR2 SDRAM颗粒。

外接4 片8bit 数据位宽的DDR2 颗粒时,需要采用至少4 层PCB 板的设计。

外接16bit 数据位宽DDR2 SDRAM 颗粒的情况下,DDR2 SDRAM 接口连接如图3-2 所示。

图3-2 DDR2 SDRAM 16 位接口示意图在外接8bit 数据位宽DDR2 SDRAM 颗粒的情况下,DDR2 SDRAM 接口连接如图3-3 所示。

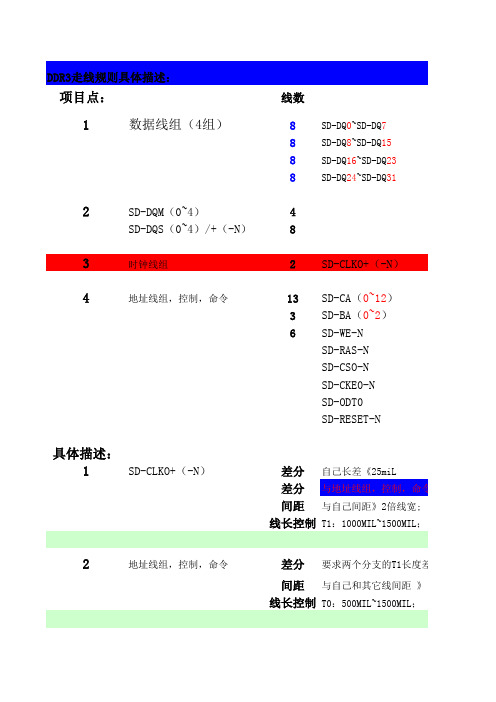

项目点:线数1数据线组(4组)8SD-DQ0~SD-DQ78SD-DQ8~SD-DQ158SD-DQ16~SD-DQ238SD-DQ24~SD-DQ312SD-DQM(0~4)4SD-DQS(0~4)/+(-N)83时钟线组2SD-CLKO+(-N)4地址线组,控制,命令13SD-CA(0~12)3SD-BA(0~2)6SD-WE-NSD-RAS-NSD-CSO-NSD-CKE0-NSD-ODT0SD-RESET-N具体描述:1SD-CLKO+(-N)差分差分间距线长控制2地址线组,控制,命令差分间距线长控制T1:1000MIL~1500MIL; T 要求两个分支的T1长度差《与地址线组,控制,命令差与自己间距》2倍线宽; 自己长差《25miLT0:500MIL~1500MIL; T1与自己和其它线间距 》 10DDR3走线规则具体描述:3数据线组(4组)差分间距4SD-DQS(0~4)/+(-N)差分间距线长控制张才四 2011-04-09四组之间差分《50miL每组间距是》 10miL与自己间距》1.5倍线宽; 1000MIL~2500MIL与 每组数据线(4组)差分第3,4层; T2:500MIL~1000MIL: T3:〈200MIL (如右图)度差《20miL (如右图)命令差分《500miL ; 与其它线间距》16miL;; T1:500MIL~1000MIL: T2:〈200MIL(如右图)》 10miL同组同层第1,3,4层)差分《25miL宽; 与其它线间距》16miL;。

DDR3布局布线译自飞思卡尔官方文档Hardware Development Guidefor i.MX 6Quad, 6Dual, 6DualLite,6Solo Families ofApplications ProcessorsIMX6 Serial Layout Recommendations目录1.DDR原理性连接框图 (3)2. DDR布局布线规则 (4)3. DDR布线细节 (5)3.1 数据线的交换 (6)3.2 DDR3(64bits)T型拓扑介绍 (6)3.3 DDR3(64bits)Fly-by型拓扑介绍 (6)3.4 2GB DDR布局布线建议 (6)3.5 4GB DDR布局布线建议 (7)4. DDR布局布线实例 (8)4.1 4片DDR T型拓扑实例 (8)4.2 8片DDR Fly-by型拓扑实例 (12)5. 高速信号布线建议 (19)6. 地平面设计建议 (19)7. DDR POWER布线建议 (21)8. 参考 (23)9. 声明 (23)1.DDR原理性连接框图图1、图2为I.MX6DQ/SDL与DDR连接框图,连接示意一目了然。

图1 DDR3与i.MX6DQ/SDL连接示意图图2 LPDDR2与i.MX6DQ/SDL连接示意图2. DDR布局布线规则DDR3在布线中十分重要,它必须考虑阻抗匹配问题,通常单端为50Ω,差分100Ω。

图3给出了DDR及其去耦电容的最终布局,其中左图是顶层布局,右图为底层布局,共计4片DDR3芯片,顶层、底层各两片。

DDR应该尽量靠近CPU,这样可以减小寄生参数和传播延时。

图3 DDR和去耦电容的布局DDR3的有两种布线形式:一种是所有信号线等长,另一种是以字节为单位分组等长。

所有信号线等长布线,该种布线方式在信号完整性上是最理想的,在设置约束规则上是简单的,但由于布线空间,使得这种方法耗时费力,甚至设计无法实现,在此只是提及一下,并不推荐使用该种方法。

1. DDR3走线总结

DDR3模块的时钟频率为800M,因此走线要求非常严格,为最大限度的减小DDR3信号线之间的时序,串扰,反射等信号完整性问题,本文走线前先将DDR3线分为11组,8个数据线、对应的DQS差分对及DM为一组(11根)共8组DDR3_DATA0~ DDR3_DATA7,地址线和控制线为一组(28根)DDR3_ADD&CON,差分时钟对为一组(1对)DDR3_CLK,其它线为一组(5根)DDR3_OTHER 。

本文DDR3走线采用的原则:

1)数据组同组走线始终保持在同一层。

线与线间距等于4mil的距离不得超过1250mil且保证同组线等长,误差±50mil。

DQS差分对间距4mil,等长误差为±5mil,减少串扰,保证时序正确。

2)地址线和控制线颗粒由于走的是Fly_by拓步结构,一般需走2至3层,插槽走的是点对点结构,一般走4到5层,同组线要求等长,误差±50mil,间距尽量保证3倍线宽(3W原则),最大限度减少串扰。

3)时钟差分对长度要求等长误差为±5mil,差分间距4mil,其它线与其间距保持在20mil以上,防止时钟信号抖动,造成读写时序错误。

4)DDR3走线的层临近的平面层应当完全对称,以便控制微带线阻抗,一般DDR3走线单端阻抗控制在60欧左右,差分阻抗90欧左右[35],减小线之间的反射。

5)VREFSST信号走线要保持线宽至少20mil,保证其能承受足够大的电流。

6)每根线所有过孔数不超过3个,且数量一致,便于控制阻抗,减少反射。

DDR3布线详解DDR3布线的那些事儿(二)DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例):数据(DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间不需要考虑等长;地址、控制、时钟信号:地址、控制信号以时钟作参考,误差控制在100MIL以内,Address、Control与CLK归为一组,因为Address、Control是以CLK的下降沿触发的由DDR控制器输出,DDR颗粒由CLK的上升沿锁存Address、Control总线上的状态,所以需要严格控制CLK与Address/Command、Control之间的时序关系,确保DDR颗粒能够获得足够的建立和保持时间。

关注等长的目的就是为了等时,绕等长时需要注意以下几点:1.确认芯片是否有Pin-delay,绕线时要确保Pin-delay开关已经打开;2.同组信号走在同层,保证不会因换层影响实际的等时;同样的换层结构,换层前后的等长要匹配,即时等长;不同层的传播延时需要考虑,如走在表层与走在内层,其传播速度是不一样的,所以在走线的时候需要考虑,表层走线尽量短,让其差别尽量小(这也是为什么Intel的很多GUIDE上面要求,表层的走线长度不超过250MIL等要求的原因);3. Z轴的延时:在严格要求的情况下,需要把Z轴的延时开关也打开,做等长时需要考虑(ALLEGRO中层叠需要设置好,Z轴延时才是对的)。

4.蛇形绕线时单线按3W,差分按5W绕线(W为线宽)。

且保证各BUS信号组内间距按3H,不同组组间间距为5H (H为到主参考平面间距),DQS和CLK 距离其他信号间距做到5H以上。

单线和差分绕线方式如下图1所示:图1.单线和差分绕线方式示例而另一个核心重点便是电源处理。

DDR3中有三类电源,它们是VDD(1.5V)、VTT (0.75V)、VREF(0.75V,包括VREFCA和VREFDQ)。

1. VDD(1.5V)电源是DDR3的核心电源,其引脚分布比较散,且电流相对会比较大,需要在电源平面分配一个区域给VDD(1.5V);VDD的容差要求是5%,详细在JEDEC 里有叙述。

项目点:线数1数据线组(4组)8SD-DQ0~SD-DQ78SD-DQ8~SD-DQ158SD-DQ16~SD-DQ238SD-DQ24~SD-DQ312SD-DQM(0~4)4SD-DQS(0~4)/+(-N)83时钟线组2SD-CLKO+(-N)4地址线组,控制,命令13SD-CA(0~12)3SD-BA(0~2)6SD-WE-NSD-RAS-NSD-CSO-NSD-CKE0-NSD-ODT0SD-RESET-N具体描述:1SD-CLKO+(-N)差分差分间距线长控制2地址线组,控制,命令差分间距线长控制要求两个分支的T1长度差《与自己和其它线间距 》 10 T0:500MIL~1500MIL; T1图)DDR3走线规则具体描述:自己长差《25miL与地址线组,控制,命令差与自己间距》2倍线宽;T1:1000MIL~1500MIL; T右图)3数据线组(4组)差分间距4SD-DQS(0~4)/+(-N)差分间距线长控制张才四 2011-04-09与 每组数据线(4组)差分与自己间距》1.5倍线宽; 1000MIL~2500MIL四组之间差分《50miL每组间距是》 10miL第3,4层同组同层度差《20miL (如右图)》 10miL ; T1:500MIL~1000MIL: T2:〈200MIL(如右第1,3,4层命令差分《500miL ; 与其它线间距》16miL;; T2:500MIL~1000MIL:T3:〈200MIL (如)差分《25miL宽; 与其它线间距》16miL;。