第5章 集成触发器

- 格式:ppt

- 大小:2.31 MB

- 文档页数:64

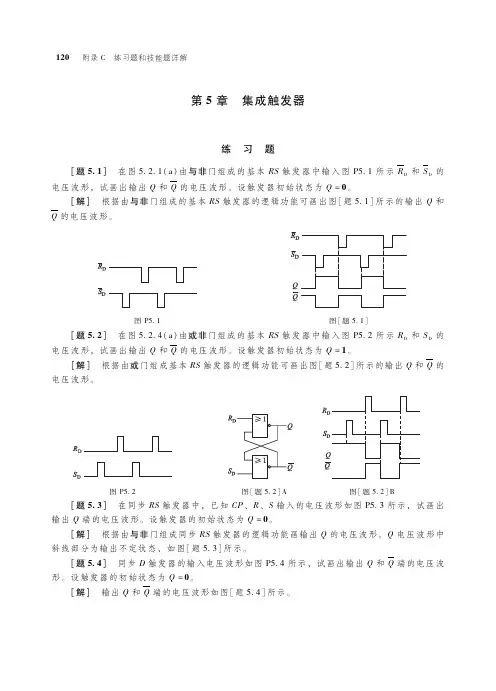

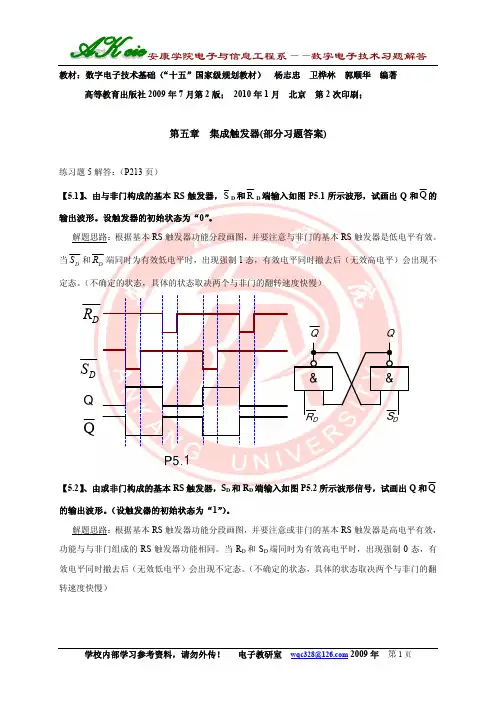

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第五章 集成触发器(部分习题答案)练习题5解答:(P213页)【5.1】、由与非门构成的基本RS 触发器,S D 和R D 端输入如图P5.1所示波形,试画出Q 和Q 的输出波形。

设触发器的初始状态为“0”。

解题思路:根据基本RS 触发器功能分段画图,并要注意与非门的基本RS 触发器是低电平有效。

当D S 和D R 端同时为有效低电平时,出现强制1态,有效电平同时撤去后(无效高电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ【5.2】、由或非门构成的基本RS 触发器,S D 和R D 端输入如图P5.2所示波形信号,试画出Q 和Q 的输出波形。

(设触发器的初始状态为“1”)。

解题思路:根据基本RS 触发器功能分段画图,并要注意或非门的基本RS 触发器是高电平有效,功能与与非门组成的RS 触发器功能相同。

当R D 和S D 端同时为有效高电平时,出现强制0态,有效电平同时撤去后(无效低电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ1≥1≥【5.4】、已知同步RS 触发器的输入CP,R 和S 的电压波形如题P5-4图所示的波形,试画出Q 和Q 的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步钟控RS 触发器是电位型触发器(高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,n 1n Q R S Q+=+,约束条件:RS=0,R=S=1时出现1Q Q 1n 1n ==++。

CPSQR【5.5】、已知同步D 触发器CP 和D 端的输入电压波形如P5.5图所示,试画出Q 端的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步式触发器是电位型触发器(假定高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,D Q1n =+。

第一章数制与编码1、二、八、十、十六进制数的构成特点及相互转换;2、有符号数的编码;3、格雷码的特点;各种进制如何用BCD码表示;4、有权码和无权码有哪些?例:一、选择题1、(1100110)B=()8421BCD=()D=()H=()O (178)10=()2=()8421BCD=()16=()82、将数1101.11B转换为十六进制数为( A )A. D.C HB. 15.3HC. 12.E HD. 21.3H3、在下列一组数中,最大数是()。

A.(258)DB.(100000001 )BC.(103)HD.(001001010111 )8421BCD4、若用8位字长来表示,(-62)D=( )原5、属于无权码的是()A.8421 码B.余3 码C.2421 码D.自然二进制码6、分别用842lBCD码表示(10011000)2为()A.230B.98C.9807、十进制数33的余3码为()。

A.00110110B.110110C.01100110D.1001008、数字电路中使用的数制是()。

A.二进制B.八进制C.十进制D.十六进制9、二进制数[101101]2和下列数中()相等A.[46]10B.[2D]16C.[54]8D.[101101]BCD10、在时间和数值上都断续变化的离散信号叫做()。

A.数字信号B.断续信号C.模拟信号D.连续信号二、判断题1、格雷码具有任何相邻码只有一位码元不同的特性。

()2、8421BCD码、5421BCD码、2421BCD码都是有权的二-十进制编码。

()3、BCD码是一种人为选定的0~9十个数字的代码,可以有许多种。

()4、8421BCD码是有权的二-十进制编码。

( )第二章逻辑代数基础1、基本逻辑运算和复合逻辑运算的运算规律、电路符号;2、逻辑代数的基本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简(有约束的和无约束的)。

第一章绪论一、填空题1、根据集成度的不同,数字集成电路分位以下四类:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路。

2、二进制数是以2为基数的计数体制,十六体制数是以16为基数的计数体制。

3、二进制数只有0和1两个数码,其计数的基数是2,加法运算的进位规则为逢二进一。

4、十进制数转换为二进制数的方法是:整数部分用除2取余法,小数部分用乘2取整法,十进制数23。

75对应的二进制数为10111.11。

5、二进制数转换为十进制数的方法是各位加权系数之和,二进制数10110011对应的十进制数为179。

6、用8421BCD码表示十进制时,则每位十进制数可用四位二进制代码表示,其位权值从高位到低位依次为8、4、2、1。

7、十进制数25的二进制数是11001,其对应的8421BCD码是00100101。

8、负数补码和反码的关系式是:补码=反码+1。

9、二进制数+1100101的原码为01100101,反码为01100101,补码为01100101。

-1100101的原码为11100101,反码为10011010,补码为10011011。

10、负数-35的二进制数是—100011,反码是1011100,补码是1011101。

二、判断题1、二进制数有0~9是个数码,进位关系为逢十进一。

()2、格雷码为无权码,8421BCD码为有权码。

(√)3、一个n位的二进制数,最高位的权值是2^n+1. (√)4、十进制数证书转换为二进制数的方法是采用“除2取余法”. (√)5、二进制数转换为十进制数的方法是各位加权系之和。

(√)6、对于二进制数负数,补码和反码相同。

()7、有时也将模拟电路称为逻辑电路。

()8、对于二进制数正数,原码、反码和补码都相同. (√)9、十进制数45的8421BCD码是101101。

()10、余3BCD码是用3位二进制数表示一位十进制数. ( )三、选择题1、在二进制技术系统中,每个变量的取值为(A )A、0和1B、0~7C、0~10D、0~F2、二进制权值为(B )A、10的幂B、2的幂C、8的幂D、16的幂3、连续变化的量称为( B )A、数字量B、模拟量C、二进制量D、16进制量4、十进制数386的8421BCD码为(B )A、0011 0111 0110B、0011 1000 0110C、1000 1000 0110D、0100 1000 01105、在下列数中,不是余3BCD码的是( C )A、1011B、0111C、0010D、10016、十进制数的权值为(D )A、2的幂B、8的幂C、16的幂D、10的幂7、负二进制数的补码等于(D )A、原码B、反码C、原码加1D、反码加18、算术运算的基础是(A )A、加法运算B、减法运算C、乘法运算D、除法运算9、二进制数-1011的补码是(D )A、00100B、00101C、10100D、1010110、二进制数最高有效位(MSB)的含义是( A )A 、最大权值B 、最小权值C 、主要有效位D 、中间权值第二章 逻辑代数基础一、填空题1、逻辑代数中三种最基本的逻辑运算是与运算、或运算、非运算。