第5章-触发器自测练习与习题

- 格式:doc

- 大小:225.50 KB

- 文档页数:8

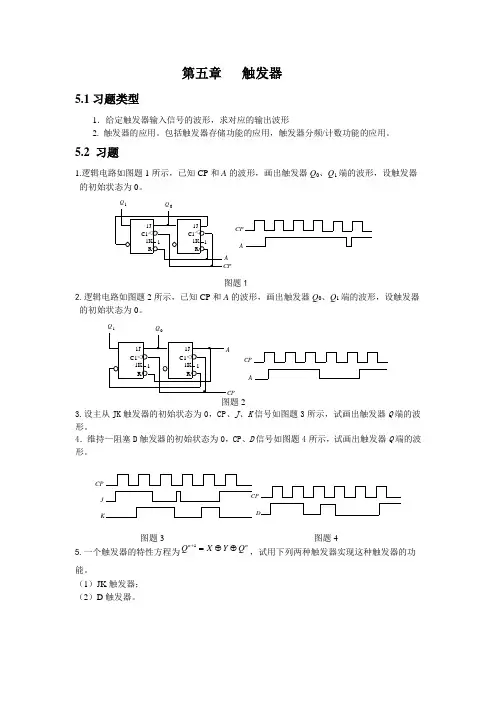

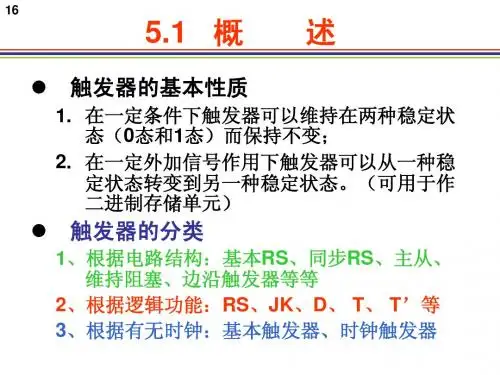

第五章 触发器5.1习题类型1.给定触发器输入信号的波形,求对应的输出波形2. 触发器的应用。

包括触发器存储功能的应用,触发器分频/计数功能的应用。

5.2 习题1.逻辑电路如图题1所示,已知CP 和A 的波形,画出触发器Q 0、Q 1端的波形,设触发器的初始状态为0。

图题12.逻辑电路如图题2所示,已知CP 和A 的波形,画出触发器Q 0、Q 1端的波形,设触发器的初始状态为0。

图题23.设主从JK 触发器的初始状态为0,CP 、J 、K 信号如图题3所示,试画出触发器Q 端的波形。

4.维持—阻塞D 触发器的初始状态为0,CP 、D 信号如图题4所示,试画出触发器Q 端的波形。

CP J K5.一个触发器的特性方程为nn Q Y X Q ⊕⊕=+1,试用下列两种触发器实现这种触发器的功能。

(1)JK 触发器; (2)D 触发器。

1Q Q CPAAQ CP A图题3CPD图题45.3 习题答案1. Q 0、Q 1端的波形见图解1。

CP A Q Q 1A CP Q1Q 0图解1 图解22. Q 0、Q 1端的波形见图解2。

3. Q 端的波形见图解3。

J K CP Q图解3 图解4 4. Q 端的波形见图解4。

5. 解:(1)JK 触发器:将JK 触发器的J 、K 端相并,再由输入端T 加以控制,则可以构成T 触发器,其特性方程为:nn Q T Q ⊕=+1。

若要实现特性方程为n n Q Y X Q⊕⊕=+1的功能,只要使:Y X T ⊕=,对应的逻辑电路见图解5(a )。

XYQQ(a ) (b )图解5(2)D 触发器:先将D 触发器转变成T 触发器,其特性方程为:n n Q T Q⊕=+1。

若要实现特性方程n n Q Y X Q ⊕⊕=+1的功能,只要使:Y X T ⊕=,对应的逻辑电路见图解5(b )。

CP D Q。

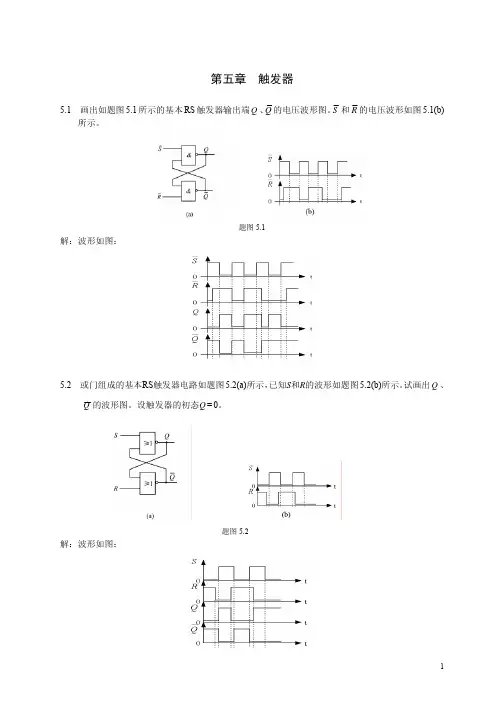

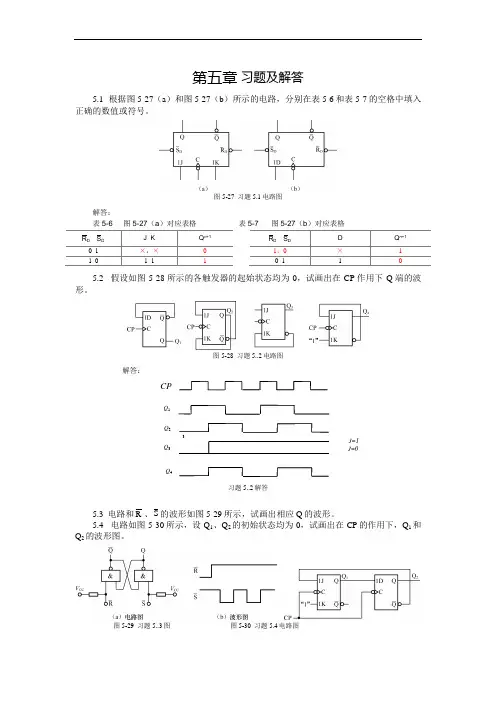

第五章触发器5.1 画出如题图5.1所示的基本RS触发器输出端、Q Q的电压波形图。

S和R的电压波形如图5.1(b)所示。

题图5.1解:波形如图:5.2 或门组成的基本RS触发器电路如题图5.2(a)所示,已知S和R的波形如题图5.2(b)所示。

试画出、Q Q的波形图。

设触发器的初态Q=0。

题图5.2解:波形如图:5.3 题图5.3所示为一个防抖动输出开关电路。

当拨动开关K时,由于开关接通瞬间发生振颤,R和S的波形如图中所示,请画出和Q Q端的对应波形。

题图5.3解:波形如图:5.4有一时钟RS触发器如题图5.4所示,试画出它的输出端的波形。

初态Q Q=0。

题图5.4解:波形如图:5.5 设具有异步端的主从JK 触发器的初始状态Q = 0,输入波形如题图5.5所示,试画出输出端Q 的波形。

题图5.5解:波形如图:5.6 设题图5.6的初始状态为2Q 1Q 0Q = 000,在脉冲CLK 作用下,画出、、的波形(所用器件都是CD4013)。

S 0Q 1Q 2Q D 、R D 分别是CD4013高电平有效的异步置1端,置0端。

题图5.6解:波形如图:5.7 设题图5.7电路两触发器初态均为0,试画出、波形图。

1Q 2Q题图5.7解:波形如图:5.8 已知CMOS 边沿触发结构JK 触发器CD4207各输入端的波形如题图5.8所示,试画出、Q Q 端的对应波形,设初态Q = 0。

S D 为高电平置1端,R D 为高电平置0端,电路为CLK 上升沿触发。

题图5.8解:波形如图:5.9 如题图5.9所示,利用CMOS 边沿触发器和同或门组成的脉冲分频器。

试分析它在一系列CLK脉冲作用下的、和Y 的波形(初始状态1Q 2Q 120Q Q ==)。

题图5.9解:波形如图:5.10 设题图5.10中各个触发器的初始状态皆为Q = 0,试画出每个触发器Q 端波形。

题图5.10解:波形如图:5.11 题图5.11示出了一个单稳态电路和它的工作波形,试分析其工作原理(初态Q=0)。

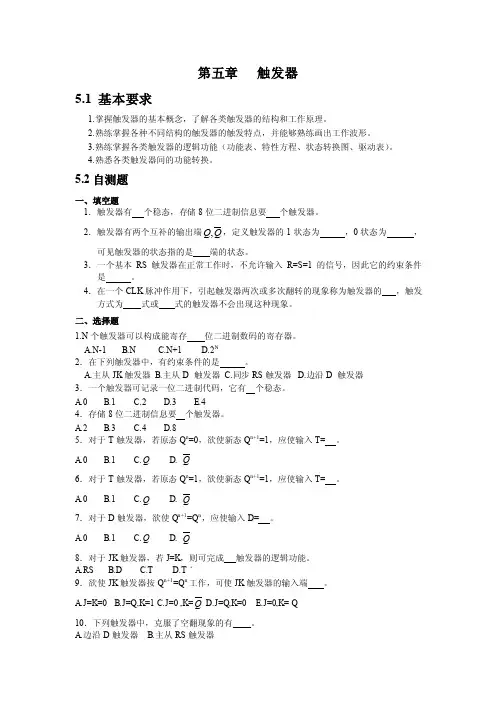

第五章触发器5.1 基本要求1.掌握触发器的基本概念,了解各类触发器的结构和工作原理。

2.熟练掌握各种不同结构的触发器的触发特点,并能够熟练画出工作波形。

3.熟练掌握各类触发器的逻辑功能(功能表、特性方程、状态转换图、驱动表)。

4.熟悉各类触发器间的功能转换。

5.2自测题一、填空题1.触发器有个稳态,存储8位二进制信息要个触发器。

Q,,定义触发器的1状态为,0状态为,2.触发器有两个互补的输出端Q可见触发器的状态指的是端的状态。

3.一个基本RS触发器在正常工作时,不允许输入R=S=1的信号,因此它的约束条件是。

4.在一个CLK脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的,触发方式为式或式的触发器不会出现这种现象。

二、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.在下列触发器中,有约束条件的是。

A.主从JK触发器B.主从D 触发器C.同步RS触发器D.边沿D 触发器3.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.3E.44.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD. Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD. Q7.对于D触发器,欲使Q n+1=Q n,应使输入D= 。

A.0B.1C.QD. Q8.对于JK触发器,若J=K,则可完成触发器的逻辑功能。

A.RSB.DC.TD.Tˊ9.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=0B.J=Q,K=1C.J=0 ,K=QD.J=Q,K=0E.J=0,K= Q10.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从RS触发器C.同步RS 触发器D.主从JK 触发器11.描述触发器的逻辑功能的方法有 。

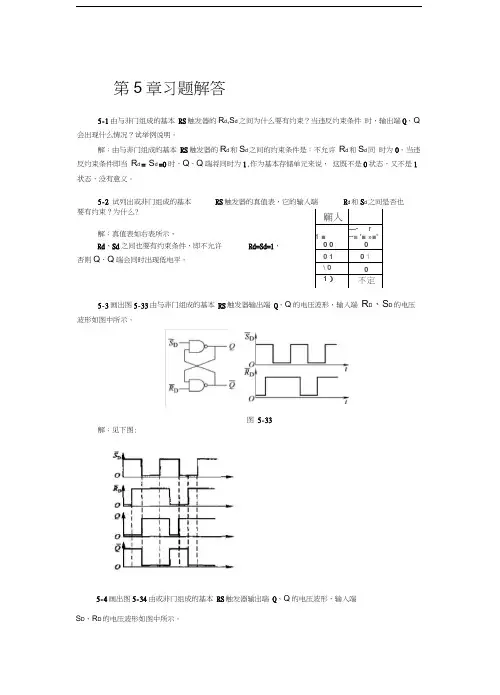

第5章习题解答5-1由与非门组成的基本RS触发器的R d,S d之间为什么要有约束?当违反约束条件时,输出端Q、Q 会出现什么情况?试举例说明。

解:由与非门组成的基本RS触发器的R d和S d之间的约束条件是:不允许R d和S d同时为0。

当违反约束条件即当R d = S d =0时,Q、Q端将同时为1,作为基本存储单元来说,这既不是0状态,又不是1状态,没有意义。

5-2 试列出或非门组成的基本RS触发器的真值表,它的输入端R d和S d之间是否也要有约束?为什么?解:真值表如右表所示、Rd、Sd之同也要有约束条件,即不允许Rd=Sd=1,否则Q、Q端会同时出现低电平。

5-3画出图5-33由与非门组成的基本RS触发器输出端Q、Q的电压波形,输入端R D、S D的电压波形如图中所示。

解:见下图:5-4画出图5-34由或非门组成的基本RS触发器输出端Q、Q的电压波形,输入端S D、R D的电压波形如图中所示。

廟人1 ■0 0—-r--■ '■ »■'0 10 1\ 001 )」不定图5-335-5图5-35所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通瞬间发生振颤,R D、S D的电压波形如图中所示。

试画出Q、Q端对应的电压波形。

图5-35解:见下图:图5-34解:见下图:5-6 在图5-36电路中、若CP、S、R的电压波形如图中所示,试画出Q、Q端与之对应的电压波形。

假定触发器的初始状态为Q = 0。

图解:见下图:5-7在图5-37(a)所示的主从RS触发器中,CP、R、S的波形如图5-37(b)所示,试画出相应的Q m、Q m、Q和Q的波形图。

图5-37解:主从RS触发器的工作过程是:在CP= I期间主触发器接收输入信号,但输出端并不改变状态,只有当CP下降沿到来时从触发器甚才翻转,称为下降沿触发。

根据主从RS 触发器状态转换图可画出波形图如下图所示。

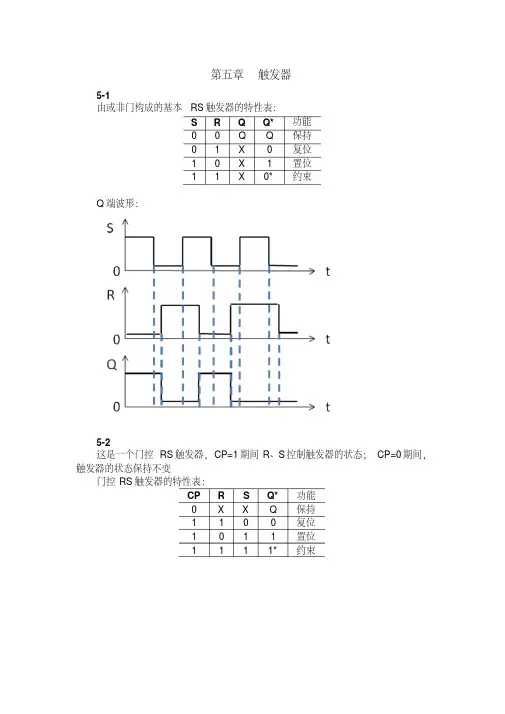

第五章触发器5-1由或非门构成的基本RS触发器的特性表:S R Q Q* 功能0 0 Q Q 保持0 1 X 0 复位1 0 X 1 置位1 1 X 0* 约束Q端波形:5-2这是一个门控RS触发器,CP=1期间R、S控制触发器的状态;CP=0期间,触发器的状态保持不变门控RS触发器的特性表:CP R S Q* 功能0 X X Q 保持1 1 0 0 复位1 0 1 1 置位1 1 1 1* 约束5-3(a) RS触发器的输入S=AQ,R=BQ,代入RS触发器的特性方程Q*=S+R Q 中,得:Q*=S+R Q=AQ+(BQ) Q=AQ+(B+Q)Q=AQ+B Q(b) RS触发器的输入S=CQ,R=DQ,代入RS触发器的特性方程Q*=S+R Q 中,得:Q*=S+R Q=CQ+(DQ) Q=CQ+(B+Q)Q=CQ+Q=C+Q5-4与非门构成的基本RS触发器的特性表:R S Q* 功能0 0 1* 约束0 1 0 复位1 0 1 置位1 1 Q 保持5-5根据主从结构同步RS触发器的特性表,可画出波形如下(设正脉冲有效)5-6将S=A,R=A代入RS触发器的特性方程Q*=S+R Q中,得:Q*=A+AQ=A——该电路实现的是D触发器5-7RS触发器的输入S=(AQ),R=(BQ),代入RS触发器的特性方程,图中的RS触发器的R、S为低有效,故特性方程为:Q*=S+RQ中,代入后得:Q*=S+RQ=((AQ))+(BQ)Q=AQ+(B+Q)Q=AQ+B Q5-8由图中可知,当R D=0时,Q1*=Q2*=0;当R D=1时,在时钟脉冲的下降沿,Q1*=D,Q2*=JQ2+K Q2= Q1Q2,画出波形图:5-9主从结构和边沿触发的触发器都是无空翻现象的触发器,这里选用边沿触发的RS触发器。

T触发器的特性方程为Q*= TQ+ T Q,与RS触发器的特性方程Q*=S+R Q,并考虑RS触发器的约束条件RS=0,将T触发器的特性方程化为:Q*= TQ+ (T+Q)Q,故S= TQ,R=(T+Q)=TQ,逻辑电路图如下:5-10触发器上升沿触发,特性方程:Q1*=D1=A,Q2*=D2= Q1,B=( Q2Q1),C=( Q2Q1),波形如下:5-11R D=0时,两个触发器的异步复位端都有效,即:Q1=Q2=0;R D=1时,Q1*=J1Q1+K1Q1= Q1+ Q1Q1=1,下降沿触发Q2*=J2Q2+K2Q2= Q2+ Q2Q2=1,CP上升沿时,触发器的时钟输入端有下降沿出现,即:CP上升沿时触发器有动作波形如下:5-12两个触发器的J=K=1,且都是下降沿触发;故:触发器(1)在CP下降沿翻转;触发器(2)在Q1的下降沿时翻转;输出F=Q1Q2,波形如下(设初态为0):5-13R D=0时,两个触发器的异步复位端都有效,即:Q1=Q2=0;R D=1时:Q1*=D1=Q2,A的上升沿触发Q2*=D2=Q1,B的上升沿触发波形如下:5-14JK触发器的特性方程Q*= JQ+K Q,与T触发器的特性方程Q*= TQ+T Q 进行比较,得:J=K=T,即可构成T触发器。

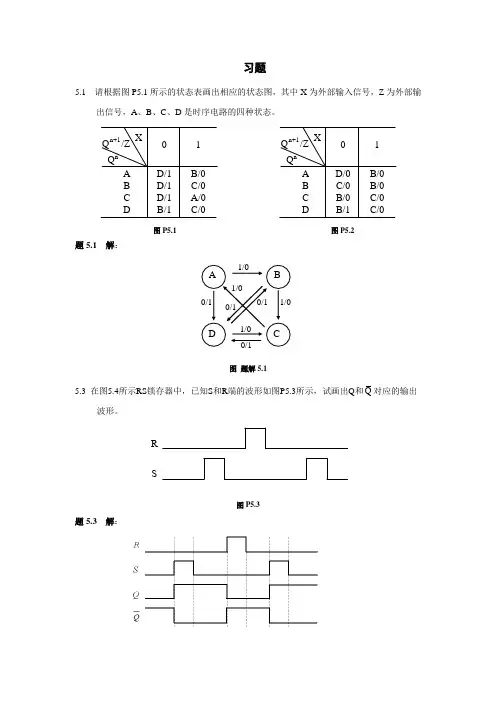

习题5.1 请根据图P5.1所示的状态表画出相应的状态图,其中X 为外部输入信号,Z 为外部输出信号,A 、B 、C 、D 是时序电路的四种状态。

A B C DD/1D/1D/1B/1Q n+1/Z Q nXB/0C/0A/0C/001 A B C DD/0C/0B/0B/1Q n+1/Z Q nXB/0B/0C/0C/001图P5.1 图P5.2题5.1 解:图 题解5.15.3 在图5.4所示RS 锁存器中,已知S 和R 端的波形如图P5.3所示,试画出Q 和Q 对应的输出波形。

R S图P5.3题5.3 解:5.5 在图5.10所示的门控D 锁存器中,已知C 和D 端的波形如图P5.5所示,试画出Q 和Q 对应的输出波形。

图P5.5题5.5 解:图 题解5.55.7 已知主从RS 触发器的逻辑符号和CLK 、S 、R 端的波形如图P5.7所示,试画出Q 端对应的波形(设触发器的初始状态为0)。

(a)CLK S R(b)图P5.7题5.7 解:CLK S R Q5.9 图P5.9为由两个门控RS 锁存器构成的某种主从结构触发器,试分析该触发器逻辑功能,要求:(1)列出特性表; (2)写出特性方程; (3)画出状态转换图; (4)画出状态转换图。

图 题解5.9题5.9 解:(1)特性表为:(2) 特性方程为:1n nnQXQ YQ +=+(3) 状态转换图为:X=1X=0Y=X=Y=1X=×Y=0图 题解5.9(3)(4)该电路是一个下降边沿有效的主从JK 触发器。

5.11 在图P5.11(a )中,FF 1和FF 2均为负边沿型触发器,试根据P5.11(b )所示CLK 和X 信号波形,画出Q 1、Q 2的波形(设FF 1、FF 2的初始状态均为0)。

(a)X(b)CLK图P5.11题5.11 解:CLK X Q 1Q 2图 题解5.115.13 试画出图P5.13所示电路在连续三个CLK 信号作用下Q 1及Q 2端的输出波形(设各触发器的初始状态均为0)。

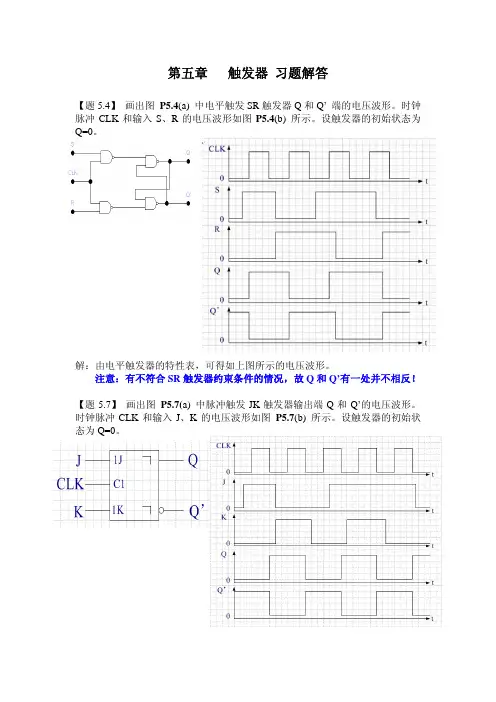

第五章触发器习题解答【题5.4】画出图 P5.4(a) 中电平触发SR触发器Q和Q’ 端的电压波形。

时钟脉冲CLK和输入S、R的电压波形如图P5.4(b) 所示。

设触发器的初始状态为Q=0。

解:由电平触发器的特性表,可得如上图所示的电压波形。

注意:有不符合SR触发器约束条件的情况,故Q和Q’有一处并不相反!【题5.7】画出图P5.7(a) 中脉冲触发JK触发器输出端Q和Q’的电压波形。

时钟脉冲CLK和输入J、K的电压波形如图P5.7(b) 所示。

设触发器的初始状态为Q=0。

解:由脉冲触发JK触发器的特性表,可得如上图所示的电压波形。

【题5.8】画出图P5.8(a) 中脉冲触发JK触发器输出端Q和Q’的电压波形。

时钟脉冲CLK和输入J、K的电压波如图P5.8(b) 所示。

设触发器的初始状态为Q=0。

解:同脉冲触发JK触发器特性表,可得如上图所示的电压波形。

【题5.11】图P5.11(a) 是带有异步清零端的上升沿触发D触发器,CLK和D 端的电压波形如图P5.11(b) 中所给出。

试画出触发器输出端Q对应的电压波形。

解:Rd=1时,触发器被置0,即Q=0时,由边沿触发D触发器的特性表,可得如上图所示的电压波形。

【题5.13】画出图P5.13(a) 中两个D触发器FF1和FF2的输出端Q1’和Q2’的电压波形。

时钟脉冲CLK和输入端D的电压波形如图P5.13(b)所示。

设触发器的初始状态均为Q=0。

解:FF1触发器发生在CLK下降沿触发;FF2触发器发生在CLK上升沿触发,则电压波形如上图所示。

【题5.14】画出图P5.14(a) 中两个JK触发器FF1和FF2的输出端Q1和Q2的电压波形。

时钟脉冲CLK和输入端J、K的电压波形如图P5.14(a) 所示。

设触发器的的初始状态均为Q=0。

解:FF1触发器发生在CLK下降沿触发;FF2触发器发生在CLK上升沿触发,则Q1、Q2的电压波形如上图所示。

第5章 触发器5.1 画出图5-1由与非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D ′、R D ′的电压波形如图中所示。

图5-1解:波形图如图5-2所示。

图5-25.2 画出图5-3由或非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D 、R D 的电压波形如图中所示。

图5-3解:波形图如图5-4所示。

图5-45.3 试分析图5-5所示电路的逻辑功能,列出真值表,写出逻辑函数式。

图5-5解:当CLK=0时,S、R的值不能加到或非门,此时Q的状态保持不变。

当CLK=1时,Q的状态随SR的不同而发生变化,真值表如表5-1所示。

表5-1卡诺图如图5-6所示。

图5-6化简得n1+=+Q S R'QSR=。

5.4 图5-7所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通瞬间发生振颤,S D′和R D′的电压波形如图中所示,试画出Q、Q′端对应的电压波形。

图5-7解:Q 、Q′端对应的电压波形如图5-8所示。

图5-85.5 在图5-9所示电路中,若CLK 、S 、R的电压波形如图中所示,试画出Q 和Q′端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图5-9解:当CLK =0时,SR 的值不能加到或非门,此时Q 的状态保持不变。

当CLK =1时,成为与非门组成的SR 触发器。

Q 和Q′端对应的电压波形如图5-10所示。

图5-105.6 若将电平触发SR 触发器的Q 与R 、Q′与S 相连,如图5-11所示,试画出在CLK 信号作用下Q 和Q′端的电压波形。

已知CLK 信号的宽度t W =4t pd 。

t pd 为门电路的平均传输延迟时间,假定t pd ≈t PHL≈t PLH 。

设触发器的初始状态为Q =0。

图5-11解:当CLK =0时,触发器输出保持不变;当CLK =1时,输出随SR 触发器变化。

脉冲的上升沿到来时,S =1,经过G 1门和G 3门的时延,Q 被置1;同时,经过G 2门的时延,G 2门输出为1。

第5章 触发器一、选择题1.为了使钟控RS触发器的次态为1,RS的取值应为()。

A.RS=0B.RS=01C.RS=10D.RS=11【答案】B【解析】当S=l,R=0时,Q=1、Q'=O。

在SD=1;当S=0,R=1时,Q=0,Q'=l;当S=R=0时,电路维持原来的状态不变。

2.4级移位寄存器,现态为0111,经右移一位后其次态为()。

A.0011或1011B.1111或1110C.1011或1110D.0011或1111【答案】B【解析】实际上移位可以看做小数点做移动,右移相当于小数点右移,应该是前三位为111,最后一位不确定,在阎石教科书中所举的例子从左到右是低位到高位进行的变换。

3.用n个触发器构成计数器,可得到的最大计数长度为()。

A.nB.2nC.n3D.2n【答案】D【解析】每个触发器可以计数为0或1两个不同的状态,这些状态彼此独立,最大计数长度为2n。

4.设计一“00001111”串行序列发生器,最少需要触发器个数是()A.4个B.3个C.5个D.8个【答案】B【解析】设有三个不同的变量Q2Q1Q0,前三个状态可以确定下一个状态,比如Q2Q1Q0=000确定输出状态为1,001的时候为1,依次类推,八个输出需要计数器至少有8个不同的状态。

5.图5-1所示电路是()。

A.无稳态触发器B.单稳态触发器C .双稳态触发器D .多谐振荡器图5-1【答案】B【解析】首先该电路有输入端,一定不会是多谐振荡器。

若以555定时器的V I2端作为触发信号的输入端,并将由T D 和R 组成的反相器输出电压v OD 接至V I1端,同时在V I1对地接入电容C ,则构成单稳态触发器。

6.为将D 触发器转换为T 触发器,图5-2所示电路的虚线框内应是( )。

A .或非门B .与非门C .异或门D .同或门图5-2【答案】D【解析】由T 触发器和D 触发器的触发方程可得:Q n +1=D ;Q n +1=T ’Q n +TQ n ’,需要令输入D =T ’Q n +TQ n ’,与Q n ’作同或运算,与Q n 作异或运算。

参考书《数字电子技术》佘新平主编华中科技大学出版社自测练习汇编(版权所有,未经允许不得复制)第1章数制与编码自测练习:1.二进制是()为基数的数制。

2.对于二进制数来说,位是指()。

3.11010是以()为基数。

4.基数为2的数制被称为()。

5.基数为10的数制被称为()。

6.十进制数的权值为()。

(a) 10的幂(b) 2的幂(c) 等于数中相应的位7.二进制数的权值为()。

(a) 10的幂(b) 2的幂(c) 1或0,取决于其位置8.二进制计数系统包含()。

(a) 一个数码(b) 没有数码(c) 两个数码9.二进制计数系统中的一位称为()。

(a) 字节(b) 比特(c) 2的幂10.2的5次方等于()。

(a) 5个2相加(b) 5个2相乘(c) 2乘以511.二进制整数最右边一位的权值为()。

(a) 0 (b) 1 (c) 212.二进制数中的最低有效位(LSB)总是位于()。

(a) 最右端(b) 最左端(c) 取决于实际的数13.二进制数()。

(a) 只能有4位(b) 只能有2位(c) 可能有任意位14.MSB的含义是()。

(a) 最大权值(b) 主要位(c) 最高有效位15.LSB的含义是()。

(a) 最小权值(b) 次要位(c) 最低有效位16.1011102 + 110112 = ()。

17.10002–1012 = ()。

18.10102× 1012 = ()。

19.101010012÷ 11012= ()。

20.基数为8的数制被称为()。

21.八进制计数系统包含()。

(a) 8个数码(b) 16个数码(c) 10个数码22.列出八进制中的8个符号()。

23.基数为16的数制被称为()。

24.列出十六进制中的16个符号()。

25.十六进制计数系统包含()。

(a) 6个数码(b) 16个数码(c) 10个数码自测练习:1.10100102= ()8。

2.110111101.101012= ()8。

第五章触发器一、填空题1、触发器具有个稳定状态,它可存储位二进制信息。

若要存储8位二进制信息时,需要个触发器。

2、触发器有两个互补输出端Q 和Q ,当0,1Q Q ==时,触发器处于状态;当1,0Q Q ==时,触发器处于状态;可见,触发器的状态是指端的状态。

3、同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为。

4、D 触发器的次态由时钟脉冲CP 上升沿到达时刻D 的状态决定,所以它是。

5、边沿JK 触发器的次态由时钟脉冲CP 下降沿到达时刻输入信号决定。

6、在基本RS 触发器暗中,输入端D R 或D R 能使触发器处于状态,输入端D S 或D S 能使触发器处于状态。

7、同步RS 触发器状态的改变是与信号同步的。

8、同步D 触发器的特性方程为。

9、在CP 脉冲和输入信号作用下,JK 触发器能够具有、、和的逻辑功能。

10、在CP 脉冲有效期间,D 触发器的次态方程1n Q+=,JK 触发器的次态方程1n Q +=。

11、对于JK 触发器,当CP 脉冲有效期间,若0J K ==时,触发器状态;若J K =时,触发器或;若1J K ==时,触发器状态。

12、对于JK 触发器,若J K =,则可完成触发器的逻辑功能。

13、对于JK 触发器,若J K =,则可完成触发器的逻辑功能。

14、将D 触发器的D 端与Q 端直接相连时,D 触发器可转换成触发器。

15、触发器具有稳定状态,其输出状态由触发器的和状态决定。

16、基本RS 触发器有、、三种可使用的功能,对于由与非门组成的基本RS 触发器,在1,0==D D R S 时,触发器;在1,1==D D R S 时,触发器;在0,1==D D R S 时,触发器;不允许时0,0==D D R S 存在,排除这种情况出现的约束条件是。

17、触发器的特性方程是用以表示与、之间关系的方程式。

18、边沿JK 触发器具有、、、功能,其特性方程为。

第5章

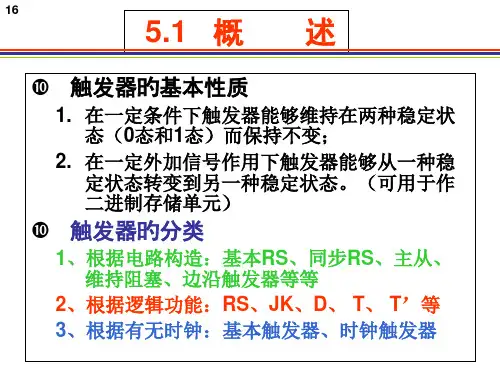

触发器5.1 RS触发器

自测练习

1.或非门构成的基本RS触发器的输入S=1、R=0,当输入S变为0时,触发器的输出将会()。

(a)置位(b)复位(c)不变

2.与非门构成的基本RS触发器的输入S=1,R=1,当输入S变为0时,触发器输出将会()。

(a)保持(b)复位(c)置位

3.或非门构成的基本RS触发器的输入S=1,R=1时,其输出状态为()。

(a)Q=0,Q=1 (b)Q=1,Q=0

(c)Q=1,Q=1 (d)Q=0,Q=0 (e)状态不确定

4.与非门构成的基本RS触发器的输入S=0,R=0时,其输出状态为()。

(a)Q=0,Q=1 (b)Q=1,Q=0

(c)Q=1,Q=1 (d)Q=0,Q=0 (e)状态不确定

5.基本RS触发器74LS279的输入信号是()有效。

(a)低电平(b)高电平

6.触发器引入时钟脉冲的目的是()。

(a)改变输出状态

(b)改变输出状态的时刻受时钟脉冲的控制。

7.与非门构成的基本RS触发器的约束条件是()。

(a)S+R=0 (b)S+R=1

(c)SR=0 (d)SR=1

8.钟控RS触发器的约束条件是()。

(a)S+R=0 (b)S+R=1

(c)SR=0 (d)SR=1

9.RS触发器74LS279中有两个触发器具有两个S输入端,它们的逻辑关系是()。

(a)或(b)与(c)与非(d)异或

10.触发器的输出状态是指()。

(a) Q (b)Q

答案:1.c 2.c 3.e

4.e 5.A 6.b

7.b 8.c 9.b

10.a

5.2 D触发器

自测练习

1.要使电平触发D触发器置1,必须使D=()、CP=()。

2.要使边沿触发D触发器直接置1,只要使S D=()、R D=()即可。

3.对于电平触发的D触发器或D锁存器,()情况下Q输出总是等于D输入。

4.对于边沿触发的D触发器,下面()是正确的。

(a)输出状态的改变发生在时钟脉冲的边沿

(b)要进入的状态取决于D输入

(c)输出跟随每一个时钟脉冲的输入

(d)(a)(b)和(c)

5.“空翻”是指()。

(a)在脉冲信号CP=1时,输出的状态随输入信号的多次翻转

(b)输出的状态取决于输入信号

(c)输出的状态取决于时钟和控制输入信号

(d)总是使输出改变状态

6.对于74LS74,D输入端的数据在时钟脉冲的()(上升,下降)边沿被传输到()(,

Q Q)。

7.要用边沿触发的D触发器构成一个二分频电路,将频率为100Hz的脉冲信号转换为50Hz 的脉冲信号,其电路连接形式为()。

答案:1.1,1 2.0,1 3.CP=1

4.

.a 6.上升,Q

7.

5.3 JK触发器

自测练习

1.主从JK 触发器是在( )采样,在( )输出。

2.JK 触发器在( )时可以直接置1,在( ) 时可以直接清0。

3.JK 触发器处于翻转时输入信号的条件是( ) (a ) J=0,K=0 (b )J=0,K=1 (c ) J=1,K=0 (d )J=1,K=1

4.J=K=1时,边沿JK 触发器的时钟输入频率为120Hz 。

Q 输出为( )。

(a ) 保持为高电平 (b )保持为低电平 (c ) 频率为60Hz 波形 (d )频率为240Hz 波形

5.JK 触发器在CP 作用下,要使Q n+1=Q n

,则输入信号必为( )。

(a ) J=K=0 (b )J= Q n

,K=0

(c ) J= Q n ,K= Q n

(d )J=0,K=1

6.下列触发器中,没有约束条件的是( )。

(a ) 基本RS 触发器 (b )主从JK 触发器 (c ) 钟控RS 触发器 (d )边沿D 触发器 7.JK 触发器的四种同步工作模式分别为( )。

8.某JK 触发器工作时,输出状态始终保持为1,则可能的原因有( )。

(a )无时钟脉冲输入 (b )异步置1端始终有效 (c )J=K=0 (d )J=1,K=0

9.集成JK 触发器74LS76内含( )个触发器,( )(有,没有)异步清0端和异步置1端。

时钟脉冲为( )(上升沿,下降沿)触发。

10.题10图中,已知时钟脉冲CP 和输入信号J 、K 的波形,则边沿JK 触发器的输出波形( )(正确,错误)。

答案:1.上升沿,下降沿 2.S d =0、R d =1,S d =1、R d =0 3.d 4.c 5.a 6.b ,d 7.保持,置1,置0,翻转 8.b,d

9.2,有,下降沿 10.正确

题10图 边沿JK 触发器的波形图 CP J K Q 1 0 0 1

1

1 0

5.4 不同类型触发器的相互转换

自测练习

1.为实现D 触发器转换成T 触发器,题1图所示的虚线框内应是( )。

(a )与非门

(b )异或门 (c )同或门

(d )或非门

2.JK 触发器构成T 触发器的逻辑电路为( )。

3.JK 触发器构成T '触发器的逻辑电路为( )。

答案:1.c

2.

.

习题解答

5-1 由与非门组成的基本RS 触发器和输入端S 、R 信号如习题

5.1图所示,画出输出端Q 、Q 的波形。

5-2 由或非门组成的触发器和输入端信号如习题5.2图所示,请写出触发器输出Q 的

习题 5.1图

R

S Q Q

A Q S

R

Q

Q 习题 5.2图

T

Q Q 题1图

1

解:先将B 、C 进行与运算得到BC 信号,再将BC 作为或非门的一个输入端对应于RS 触发器的功能表,即可得到输出Q 的波形

5-3 钟控的RS 触发器如习题5.3图所示,设触发器的初始状态为0,画出输出端Q 的波形。

解:钟控RS 触发器的输出Q 应该在CP=1时,根据输入端R 、S 的信号改变状态的。

5-4 边沿D 触发器如习题5.4图所示,确定相关于时钟的Q 输出,并分析其特殊功能。

设触发器的初始状态为0。

解:根据习题5.4图可得D 触发器的特征方程 Q D Q 1n ==+,因此在CP 上升沿到来时,Q 输出端的状态随Q 变化,故有如图波形,可见输出端Q 的波形为输入脉冲CP 的二分频信号。

5-5 已知边沿D 触发器输入端的波形如习题5.5图所示,假设为上升沿触发,画出输出端Q 的波形。

若为下降沿触发,输出端Q 的波形如何?设初始状态为0。

Q

1S C1 1R Q S CP R CP

S

R

Q 习题 5.3图

习题 5.4图

Q CP Q CP

D

(a )

(b )

习题 5.5图

解:上升沿触发时,Q 输出波形为(a ),下降沿触发时,Q 输出波形为(b )。

5-6 已知D 触发器各输入端的波形如习题5.6图所示,试画出Q 和Q 端的波形。

解:先将D 1、D 2进行与运算得到D 1D 2信号,再将D 1D 2作为D 触发器的D 输入端,对应于D

触发器的功能表,即可得到输出Q 的波形

5-7 已知逻辑电路和输入信号如习题5.7图所示,画出各触发器输出端Q 1、Q 2的波形。

设触发器的初始状态均为0。

解:习题 5.7图中两个D 均为上升沿触发,输入信号D 始终为1,且两个D 触发器的R d

端为高电平有效。

由于初始状态均为0,故当

CP 1到来时,Q 1首先由0变成1,使得1Q 由1

变成0,当CP 2到来时,Q 2也由0变成1,而此时的Q 2=1又使得Q 1由1变成0并使D2触发器Q 2直接置0,故Q 2的输出始终被钳制为0。

其波形见习题 5.7图中。

5-8 已知JK 信号如习题5.8图中所示,分别画出主从JK 触发器和边沿(下降沿)JK 触发器的输出端Q 的波形。

设触发器的初始状态为0。

习题 5.7图

CP1 CP2 Q 1 Q 2 CP J K

CP

R d D 1 D 2

D 1D 2

Q

D 1D 2 CP

Q R d 1

习题 5.6图

解:主从JK 触发器的波形按只能动作一次的特点画出的。

5-9 边沿JK 触发器电路和输入端信号如习题5.9图所示,画出输出端Q 的波形。

5-10 集成JK 触发器的电路图如习题5.11图所示。

画出输出端Q B 的波形。

设两触发器的初始状态均为0。

S

J 1

J 2 J 3

CP K 1

K 2

K 3

R CP CP

S

R

J 1

J 2

J 3

K 1

K 2

K 3

1J 1K Q 习题 5.9图

习题5.11图

解:根据波形图可知,Q A输出的波形为CP的二分频信号,Q B输出的波形为CP的四分频信号

5.11 试用D触发器和适当的门电路构成JK触发器和T触发器。

解:见正文。

(注:可编辑下载,若有不当之处,请指正,谢谢!)。