数字电子技术基础全套

- 格式:pptx

- 大小:2.04 MB

- 文档页数:68

数字电子技术基础教学教程

数字电子技术是现代电子技术的基础,包含了数字电路、数字

信号处理、计算机原理等重要内容。

本教程旨在帮助读者全面地了

解数字电子技术的基本概念、实际应用和未来发展趋势。

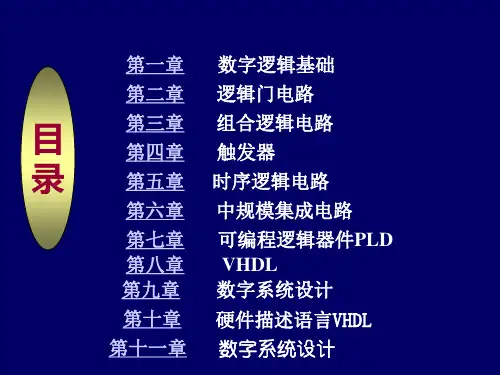

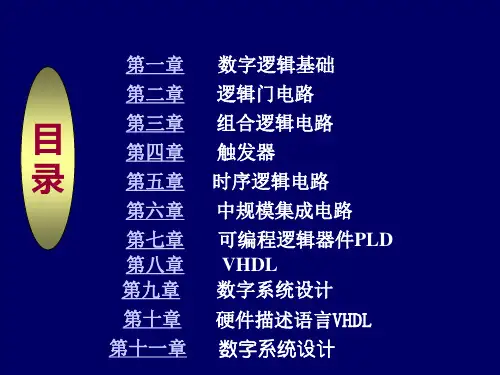

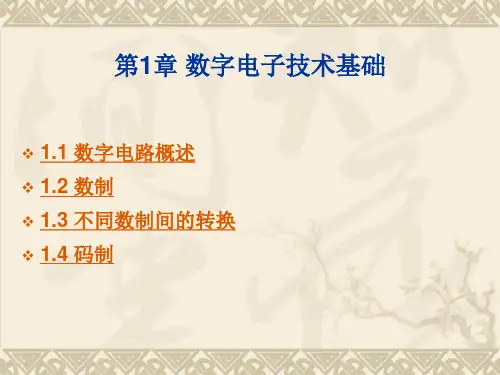

本教程分为以下几个部分:

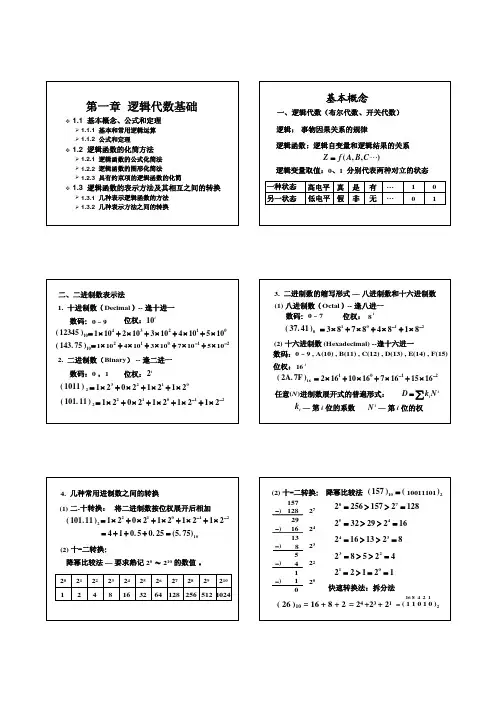

1. 数字电路基础:介绍数字电路的基本原理和组成,包括数字

信号、逻辑门、寄存器、计数器等内容。

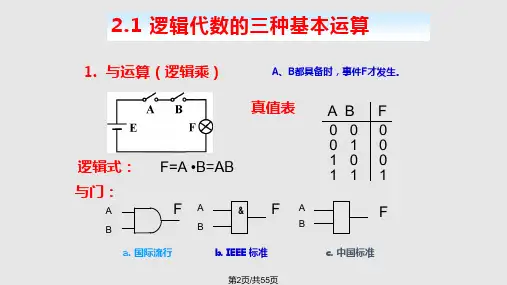

2. 逻辑代数和布尔代数:讲解逻辑代数和布尔代数的基本定义、公式和运算规则,以及应用场景和实例。

3. 组合逻辑电路设计:介绍组合逻辑电路的实现方法和设计流程,以及常用的编码器、解码器、多路选择器和加法器等组合电路。

4. 时序逻辑电路设计:讲解时序逻辑电路的基本概念和特点,

以及时序电路的设计方法和时钟信号的应用。

5. 计算机原理与体系结构:介绍计算机的基本原理和内部结构,包括存储器、CPU、总线和输入输出等部件,以及计算机体系结构

的分类和应用。

希望这份教学教程能够帮助读者加深对数字电子技术的理解和

掌握,也希望读者能够在学习过程中提出宝贵意见和建议,不断完

善和改进本教程的内容。