VLSI系统设计6

- 格式:ppt

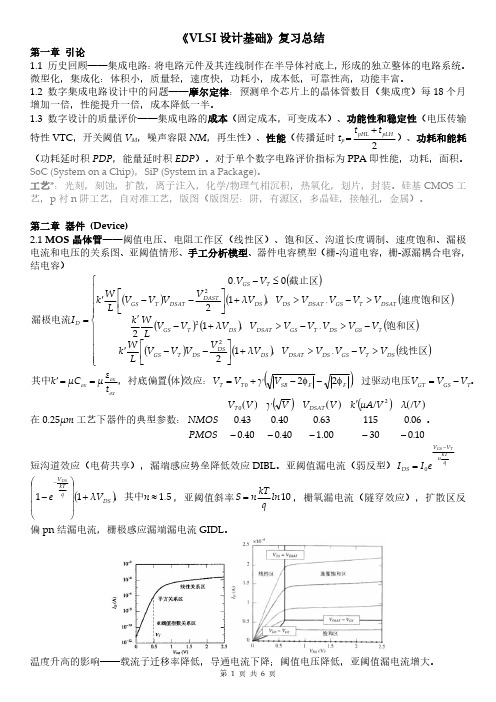

- 大小:1.35 MB

- 文档页数:40

实验一简单组合逻辑电路的设计与仿真一、实验目的(1)初步掌握Verilog/VHDL程序的基本结构(2)学会编写简单的Verilog/VHDL程序(3)掌握用Modelsim软件进行RTL级代码的设计和仿真的基本方法(4)掌握基本组合逻辑电路的实现方法。

二、实验内容这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign 结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

设计模块://--------------- compare.v -----------------------module compare (equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0; // a等于b时,equal输出为1;a不等于b时,equal输出为0。

endmodule测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。

测试模块://--------------- test_compare.v-----------------module test_compare;reg a,b;wire equal;initial // initial常用于仿真时信号的给出。

begin a=0; b=0;#100 a=0; b=1;#100 a=1; b=1;#100 a=1; b=0;#100 $stop; // 系统任务,暂停仿真以便观察仿真波形。

endcompare compare1(.equal(equal),.a(a),.b(b)); // 调用模块。

endmodule仿真波形(部分):三、实验步骤1、产生一个工作库在对设计进行仿真之前,你首先需产生一个库,用于放置编译的源代码。

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

现代VLSI设计-基于IP核的设计第四版课程设计一、背景介绍现代集成电路设计是电子信息工程学科体系中重要的一环,在现代电子信息领域有着广泛的应用。

随着技术的不断进步,集成度的要求越来越高,逐渐从单个器件转向系统级芯片设计,为此,设计人员要对现代VLSI设计有深入的了解和掌握。

本课程设计基于IP核的设计,旨在通过具体的实际案例,提高学生对现代VLSI设计的理解,并学习如何利用常见IP核优化系统性能,达到减少设计成本、提高设计效率、提高设计可维护性的目的。

二、设计目标本次课程设计的主要目标是掌握VLSI设计的基本原理和流程,学习如何使用IP核进行设计,理解如何对电路进行优化。

三、课程内容3.1 VLSI设计基本原理VLSI(Very Large Scale Integration)是指超大规模集成电路。

VLSI设计主要包括从设计到工艺、测试等多个环节,本部分将学习VLSI设计的基本流程、器件结构、工艺和测试方法等基本知识。

3.2 IP核简介IP核(Intellectual Property)是指独立的设计模块,可以被其他不同的电路利用。

IP核的设计和应用可以大大简化电路设计,提高设计效率和可维护性。

本部分将学习IP核的基本原理、分类和应用场景。

3.3 IP核的设计本部分将围绕基于IP核的设计开展实际操作,涉及IP核的设计和应用。

具体包括如何使用Vivado软件进行IP核的设计和如何利用IP核完成特定功能的设计。

3.4 IP核的优化本部分将介绍如何使用IP核进行电路优化,旨在提高系统设计的性能和可靠性。

具体包括如何对IP核进行定制化、如何进行IP核的性能评估以及如何评估系统的功耗等。

四、课程实践本课程设计将通过实践案例学习VLSI设计、IP核的设计与优化。

4.1 实践案例1:基于IP核的数字信号处理系统设计本案例将指导学生利用IP核进行一个简单的数字信号处理系统设计,包括数据输入输出模块、FIR滤波器模块、FFT模块。

VLSI设计基础第三版课程设计一、概述VLSI(Very Large-Scale Integration)是指集成电路技术中的一种技术,这种技术可以使几千个甚至几百万个电子元件集成在一个芯片上。

VLSI的发展使得集成电路的组织、设计、制造变得更加简单和经济。

因此,本课程旨在让学生了解VLSI的基础概念、设计方法和制造流程,同时通过实践,帮助学生掌握VLSI设计的基础知识和技能。

二、教学目标1. 理论目标•掌握VLSI设计的基本概念、原理和方法;•了解VLSI设计流程和制造工艺;•理解芯片设计中的时序、布局和布线等内容;•熟悉ASIC和FPGA的原理和应用。

2. 实践目标•熟悉VLSI设计工具的使用;•学会使用一些流行的VLSI仿真工具;•实现一个小型VLSI设计项目,加深对VLSI设计过程的理解。

第一部分:VLSI设计原理1.VLSI概述2.VLSI设计流程3.VLSI芯片设计的基本概念4.芯片布局设计5.芯片布线设计6.阵列设计基础7.数字信号处理器的设计8.软件定义电台的设计9.ASIC设计基础10.FPGA的基本原理和应用第二部分:VLSI设计实践1.FPGA的简单应用2.Verilog HDL及其模块化设计方法3.VHDL语言及其模块化设计方法4.门级元件的设计和实现5.组合逻辑和时序逻辑的设计6.测试的方法和技巧7.系统级仿真本课程将采用以下教学方法:1.理论授课:讲解VLSI设计的基本概念、原理和方法;2.实验实践:通过一些实践操作,将理论知识具体化;3.设计实践:要求学生进行一些小型VLSI设计项目。

五、教学要求1. 学生要求本课程面向电子信息类等专业的学生,建议先修读模拟电子技术、数字电子技术等课程。

因为本课程需要学生具备一定的电路基础知识和编程能力。

2. 教师要求本课程需要教师具备丰富的VLSI设计经验,熟悉VLSI设计流程和常用工具,能够灵活运用各种学习资源,耐心指导学生进行设计项目。

VLSI系统结构设计典型习题及解答1、填空题1)通用数字系统设计的性能指标是:(1)所需的硬件电路和资源;(2)执行的速度;(3)功耗;(4)有限字长的性能。

2)DSP区别于其它通用计算的两个重要特性是:(1)实时吞吐率的需要;(2)数据驱动的性质。

3)DSP程序的迭代边界是指关键环路的环路边界。

计算迭代边界的算法有最长矩阵路径(LPM)算法和最小环均值(MCM)算法。

4)在DFG中,关键路径是指具有零延时的所有路径中具有最长运算时间的路径。

5)流水线技术就是采用沿着数据通路引入流水锁存器的方法来减小有效关键路径,从而可以提高时钟速度或采样速度,或者可以在同样的速度下降低功耗。

6)并行处理技术就是多个输出在一个时钟周期内并行的计算,从而使有效采样速度提高到与并行级数相当的倍数。

7)重定时在同步电路设计中有很多应用,包括缩短电路的时钟周期,减少电路中寄存器的数目、降低电路的功耗和逻辑综合的规模。

8)展开变换可以揭示隐藏在用DFG描述的数字信号处理系统中的并发性。

因此,展开技术可以用来缩短DSP算法的迭代周期。

展开可以用来生成高速低功耗应用中的字并行架构。

9)折叠变换是一种设计分时复用架构的系统变换技术。

在DSP架构中,折叠技术提供了一种以时间换取面积的方法。

10)重定时在同步电路设计中有很多应用,包括缩短电路的时钟周期,减少电路中寄存器的数目、降低电路的功耗和逻辑综合的规模。

11)脉动阵列是一种有节奏地计算并通过系统传输数据的处理单元网络,这种系统的特征是模块化和规则化。

12)对于3阶FIR滤波器y(n)=b0x(n)+b1x(n-1)+b2x(n-2),请说明下列参数的含义:y(n)表示 n时刻在输出端Y的输出 ; x(n)表示: n时刻在输入端X的输入; x(n-2)表示n-2时刻在输入端X的输入在N时刻在电路中某点的值。

13)利用折叠变换进行VLSI系统的结构设计中,画折叠图的六个步骤分别是:(1)定义折叠集;(2)计算折叠方程;(3)画出折叠运算节点;(4)添加各节点的输入;(5)根据折叠方程添加延时及连线;(6)图形整理。

实验一 15位流水线加法器的设计与实现一、实验类型研究探索性实验。

二、实验目的与任务1.实验目的:熟悉实现流水线的VLSI结构设计思想和所采用的结构设计优化技术,并进一步熟悉有关硬件描述语言的编程和EDA软件的使用。

2.实验任务:完成一个15位流水线加法器的FPGA设计与实现,包括系统结构设计、硬件语言逻辑描述,再进行程序调试、仿真分析等。

三、实验基本原理在系统硬件设计中,采用流水线可提高系统的处理速度,但需增加硬件资源。

而FPGA 中由于每一个逻辑单元都包含一个触发器,这个触发器或者没有用到,或者用于存储布线资源,因此将流水线应用在FPGA的设计中,在提高系统处理速度的同时,只需要极少或根本不需要额外的硬件成本。

图1.1是一个采用流水线的15位加法器的原理图,它采用流水线将一个15位的并行加法器分解成一个7位和一个8位的并行加法运算,在提高系统处理速度的同时,又充分利用了系统的有关触发器资源。

图1.1 15位流水线加法器原理图四、实验仪器设备与工具软件1.PC机(要求内存在256M以上)。

2. Quartus II/ (MAX+plus II+Synplify)、Modelsim软件。

五、实验内容完成一个如图1.1所示的15位流水线加法器的FPGA设计与实现。

具体包括:系统体系结构的设计,主要功能电路的设计,各种VHDL源程序的设计,系统的逻辑综合与适配,系统的调试验证(包括程序调试、有关仿真及分析)。

本设计的参考程序如下:LIBRARY LPM;USE LPM.LPM_COMPONENTS.ALL;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY ADD_1P ISGENERIC (WIDTH : INTEGER := 15; -- TOTAL BIT WIDTHWIDTH1 : INTEGER := 7; -- BIT WIDTH OF LSBSWIDTH2 : INTEGER := 8; -- BIT WIDTH OF MSBSONE : INTEGER := 1); -- 1 BIT FOR CARRY REG.PORT (X,Y : IN STD_LOGIC_VECTOR(WIDTH-1 DOWNTO 0);-- INPUTSSUM : OUT STD_LOGIC_VECTOR(WIDTH-1 DOWNTO 0);-- RESULTCLK : IN STD_LOGIC);END ADD_1P;ARCHITECTURE FLEX OF ADD_1P ISSIGNAL L1, L2, R1, Q1 -- LSBS OF INPUTS: STD_LOGIC_VECTOR(WIDTH1-1 DOWNTO 0);SIGNAL L3, L4, R2, Q2, U2, H2 -- MSBS OF INPUTS: STD_LOGIC_VECTOR(WIDTH2-1 DOWNTO 0);SIGNAL S : STD_LOGIC_VECTOR(WIDTH-1 DOWNTO 0);-- OUTPUT REGISTERSIGNAL CR1, CQ1 : STD_LOGIC_VECTOR(ONE-1 DOWNTO 0);-- LSBS CARRY SIGNAL BEGINPROCESS -- SPLIT IN MSBS AND LSBS AND STORE IN REGISTERSBEGINW AIT UNTIL CLK = '1';-- SPLIT LSBS FROM INPUT X,YFOR K IN WIDTH1-1 DOWNTO 0 LOOPL1(K) <= X(K);L2(K) <= Y(K);END LOOP;-- SPLIT MSBS FROM INPUT X,YFOR K IN WIDTH2-1 DOWNTO 0 LOOPL3(K) <= X(K+WIDTH1);L4(K) <= Y(K+WIDTH1);END LOOP;END PROCESS;-------------- FIRST STAGE OF THE ADDER ------------------ADD_1: LPM_ADD_SUB -- ADD LSBS OF X AND Y GENERIC MAP ( LPM_WIDTH => WIDTH1,LPM_REPRESENTATION => "UNSIGNED",LPM_DIRECTION => "ADD")PORT MAP ( DATAA => L1, DATAB => L2,RESULT => R1, COUT => CR1(0));REG_1: LPM_FF -- SAVE LSBS OF X+Y AND CARRY GENERIC MAP ( LPM_WIDTH => WIDTH1 )PORT MAP ( DATA => R1, Q => Q1,CLOCK => CLK );REG_2: LPM_FFGENERIC MAP ( LPM_WIDTH => ONE )PORT MAP ( DATA => CR1, Q => CQ1, CLOCK => CLK );ADD_2: LPM_ADD_SUB -- ADD MSBS OF X AND Y GENERIC MAP ( LPM_WIDTH => WIDTH2,LPM_REPRESENTATION => "UNSIGNED",LPM_DIRECTION => "ADD")PORT MAP (DATAA => L3, DATAB => L4, RESULT => R2); REG_3: LPM_FF -- SAVE MSBS OF X+YGENERIC MAP ( LPM_WIDTH => WIDTH2 )PORT MAP ( DATA => R2, Q => Q2, CLOCK => CLK );------------ SECOND STAGE OF THE ADDER ---------------------- ONE OPERAND IS ZEROH2 <= (OTHERS => '0');-- ADD RESULT FROM MSBS (X+Y) AND CARRY FROM LSBSADD_3: LPM_ADD_SUBGENERIC MAP ( LPM_WIDTH => WIDTH2,LPM_REPRESENTATION => "UNSIGNED",LPM_DIRECTION => "ADD")PORT MAP ( CIN => CQ1(0), DATAA => Q2,DATAB => H2, RESULT => U2 );PROCESS -- BUILD A SINGLE REGISTERED OUTPUT BEGIN -- WORD OF WIDTH=WIDTH1+WIDTH2W AIT UNTIL CLK = '1';FOR K IN WIDTH1-1 DOWNTO 0 LOOPS(K) <= Q1(K);END LOOP;FOR K IN WIDTH2-1 DOWNTO 0 LOOPS(K+WIDTH1) <= U2(K);END LOOP;END PROCESS;SUM <= S ; -- CONNECT S TO OUTPUT PINSEND FLEX;六、实验步骤1.系统体系结构及主要功能电路的设计。

第一章VLS知识点VLS(Very Large Scale integration)是指非常大规模集成电路技术,是现代集成电路技术的重要分支。

VLS技术的发展使得集成电路的规模大大增加,功能更加强大,性能更加优越。

本章将介绍VLS知识点的基础知识、设计原理、工艺和应用等方面的内容。

一、基础知识1.集成电路:将多个电子元件(如电晶体、电阻、电容等)集成到单个半导体晶片上的电路。

其主要特点是占用空间小、功耗低、可重复使用。

2.VLSI:非常大规模集成电路,是将成百上千个晶体管集成到一个微小的硅晶片上,使电路规模大大增加。

二、设计原理1.逻辑门电路:是通过逻辑门(与门、或门、非门等)来实现不同逻辑功能的电路。

逻辑门的输出结果仅与输入信号的逻辑关系有关。

2. 布尔代数:在逻辑门电路中,常用布尔代数来描述逻辑关系。

布尔代数是由数学家乔治·布尔(George Boole)创立的一种数学运算方法,用于描述逻辑关系和逻辑运算。

3.时序逻辑:逻辑电路的输出是由输入信号和时钟信号共同决定的。

时钟信号用于控制逻辑电路的工作时序。

三、工艺1.MOSFET:金属-氧化物-半导体场效应晶体管,是VLSI集成电路中常用的基本元件。

其主要特点是体积小、功耗低、噪声低、可靠性高。

2.CMOS:互补金属-氧化物-半导体技术,是一种集成电路制造工艺。

CMOS技术结合了NMOS(n型金属-氧化物-半导体场效应晶体管)和PMOS (p型金属-氧化物-半导体场效应晶体管)技术,具有功耗低、可靠性高的特点。

3.焊接技术:用于将船到的芯片和印刷电路板进行连接的一种技术。

常用的焊接技术有手工焊接、自动焊接、贴片焊接等。

4.接触孔技术:用于在不同层次的芯片之间进行电连接的一种技术。

接触孔技术将不同层次的芯片通过金属导线进行连接,实现不同层次之间的信号传输。

四、应用1.通信领域:VLSI技术的快速发展使得通信设备的功能大大增强。

在通信领域中,VLSI技术被广泛应用于芯片设计、信号处理、调制解调器等方面。

第一章1.一个完整的电子信息系统能够及时的捕捉信息,处理信息,传递信息。

2.信息和信息处理可以是链式的,也可以是并发的。

目前大多数是链式的。

3.信息链处理模块关联图:(画图连到一起,带箭头)外部信息,能域变换,信号预处理,信号变换,数字信号处理,信号变换,驱动伺服能域变换4.感知信息模块(1)传感器(基本功能是完成不同领域的信号转换)主要有:半导体传感器,微机电传感器半导体传感器有:压敏传感器,气敏传感器,温度传感器MEMS传感器有:汽车安全气囊加速传感器,MEMS风速计(2)电信号处理与变换模块:完成模拟信号的放大或者是调制信号的检出,模拟信号到数字信号的转换(ADC),数字信号到模拟转换(DAC),信号的调制等(3)目前的算法模块以数字方式工作(4)输出处理模块:其任务是根据信息输出的需要,将信息转成一定的输出形式或直接完成某些动作5.VLSI系统设计的主要层次:层次:(1)硬件系统的设计,即从系统行为到具体的逻辑和电路(2)版图设计,目的是将具体的逻辑或电路变为二维平面上的图形(3)工艺设计,是对为电子制造技术的选择与控制,再贵材料或者其他半导体材料上,将二维的平面版图转变为三维的立体器件结构6.VLSI系统的设计通常采用:(1)自顶向下和(2)由底向上的设计方法7.复杂性管理:(1)抽象提取:将涉及层次抽象或硬件设计层次,工艺设计层次,版图设计层次。

硬件设计层次包括了两个方面的设计问题:硬件系统设计和可测试性设计(2)分级管理(3)设计规则化、模块化(4)全局优化和局部优化:局部优化以基本模块为对象开展优化(5)设计工具8.版图设计三个主要层次:基本单元版图设计;版图生成单元基本结构版图设计;系统版图布局布线设计。

9.如何充分发挥各层次的优点,实现系统设计的?这就是当今集成电路或系统的设计理念:将集成电路或系统的分析计算部分和信息接口分开进行设计。

分析计算及部分即所谓的内部电路,采用高度规则的结构以降低版图实现的难度,提高设计仙侣;与外界进行信息交换的接口部分即I∕O单元,采用高度优化的单元形式,为VLSI系统内部提供稳定可靠的信号,屏蔽外部无关信号干扰,提高电路或系统可靠性能,10.规则结构分为:门阵列,晶体管规则阵列,非规则结构:宏单元,积木块晶体管规则阵列以晶体管作为基本单元构成阵列,常见形式:各种ROM结构和其他的可编程晶体管结构,如与ROM,或ROM,PLA等11.VLSI产品的设计开发通常包括几个主要的设计与研制过程,系统,逻辑,电路设计,版图设计,工艺试验和测试实验。