lattice FPGA简介

- 格式:docx

- 大小:29.83 KB

- 文档页数:6

LatticeECP4系列重新定义了低成本、低功耗FPGA《电子与电脑》编辑部【期刊名称】《电子与电脑》【年(卷),期】2011(000)012【摘要】莱迪思半导体公司日前宣布推出下一代LatticeECP4FPGA系列,由其重新定义了低成本,低功耗的中档FPGA市场,具有6 Gbps的SERDES采用低成本wire-bond封装,功能强大的DSP块和具有基于硬IP的通信引擎,适用于成本和功耗敏感的无线、有线、视频,和计算市场.LatticeECP4FPGA系列以LatticeECP3系列为基础,为主流客户提供高级功能,同时保持业界领先的低功耗和低成本.对于为各种应用开发主流平台,LatticeECP4器件是非常理想的,如远程无线射频头、分布式天线系统、蜂窝基站、以太网汇聚、交换、路由、工业网络、视频信号处理、视频传输和数据中心的计算.高品质的SERDES和固化的通信引擎LatticeECP4 FPGA 包含多达1 6个符合CEI标准的6 Gbps SERDES通道,具有嵌入式物理编码子层(PCS)模块,采用低成本wire-bonded封装和高性能flip chip封装,使客户能够选择以芯片到芯片以及远距离背板应用的方式部署LatticeECP4 FPGA.多功能和可配置的SERDES/PCS可以无缝地与固化的通信引擎相集成,经济地构建完整的高带宽子系统.通信引擎比用类似的FPGA实现减少10倍以上的功耗和成本.LatticeECP4通信引擎组合包括针对PCI Express2.1、多个10千兆以太网MAC和三速以太网MAC,以及串行快速I/O (SRIO) 2.1的解决方案.SERDES/PCS和通信引擎的结合是完成基于复杂串行协议的设计的理想选择,具有较低的成本,功耗和小尺寸的特点,同时加快了产品的上市时间.【总页数】2页(P30-31)【作者】《电子与电脑》编辑部【作者单位】【正文语种】中文【相关文献】1.Nano系列-超低成本、超低功耗的FPGA [J],2.Altera发售低功耗低成本的CycloneV系列28nmFPGA [J],3.重新定义低功耗通用FPGA,莱迪思Certus-NX"新"在何处? [J], 单祥茹tticeECP4^(TM)系列重新定义了低成本、低功耗FPGA [J],ttice低成本低功耗ECP4FPGA系列 [J],因版权原因,仅展示原文概要,查看原文内容请购买。

FPGA 简介2008/06/15 11:48FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB (Input Output Block)和内部连线(Interconnect)三个部分。

FPGA的基本特点主要有:1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

——2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5)FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

目前FPGA的品种很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA 公司的FIEX系列等。

FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。

用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。

掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA功能时,只需换一片EPROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

FPGA及其设计原理简介搜集&制作者:myxxyyFPGA(Field Programmable Gate Array)全称现场可编程门阵列,是1984年由美国Xilinx公司发明的基于SRAM工艺以查找表(LUT)为基本单元的新型可编程逻辑器件(PLD)。

所谓PLD,是指运行功能是在器件生产出来以后由使用者设定的,以此区别于传统的固定功能型器件。

FPGA可由用户自定义其内部的逻辑和功能,同时又能够进行无限次的重新配置,加上PC机上CAD辅助设计软件和强大的仿真工具,使得电子设计工程师在办公室或实验室中就可以设计自己的ASIC器件,实现用户规定的各种专门用途,极大的增加了电子系统设计的灵活性。

目前,FPGA广泛应用于通信、移动设备、航空航天、自动控制等领域,并有向计算密集型应用发展的趋势。

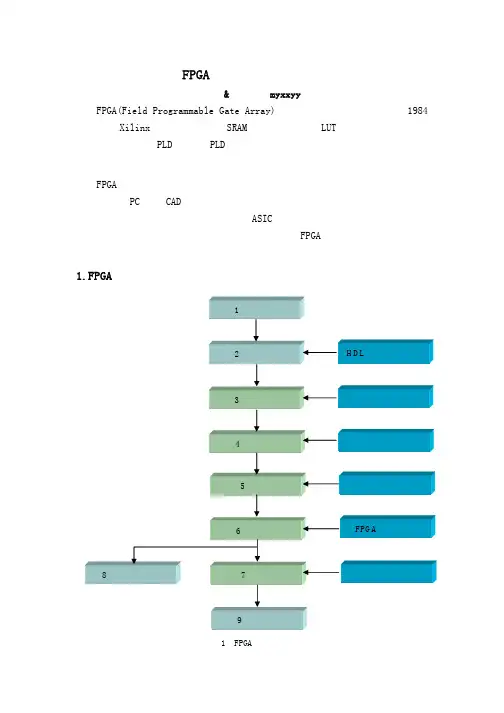

1.FPGA设计流程及步骤图1:FPGA的设计流程图说明:z HDL语言指VHDL和Verilog HDL等。

z逻辑仿真器主要指ModelSim,Verilog-XL等。

z逻辑综合器主要指LeonardoSpectrum、Synplify、FPGA Express/FPGA Compiler等。

z FPGA厂家工具指的是如Altera的Max PlusII、Quartus II,Xilinx的Foundation、Alliance、ISE等下面分别介绍各个设计步骤:1.1设计定义这是由系统概要设计指导和详细设计具体规定下的本FPGA模块必须完成的功能以及与外围器件的接口,包括接口信号规格、处理时钟频率、时序要求、管脚分配锁定等,是对FPGA进行编程设定的依据。

对设计定义的要求是合理、清晰、准确。

1.2设计输入设计输入主要包括使用硬件描述语言HDL与原理图输入两种方式。

HDL设计方式是现今设计大规模数字集成电路的良好形式,除IEEE标准中VHDL与Verilog HDL两种形式外,尚有各自FPGA厂家推出的专用语言,如Quartus 下的AHDL。

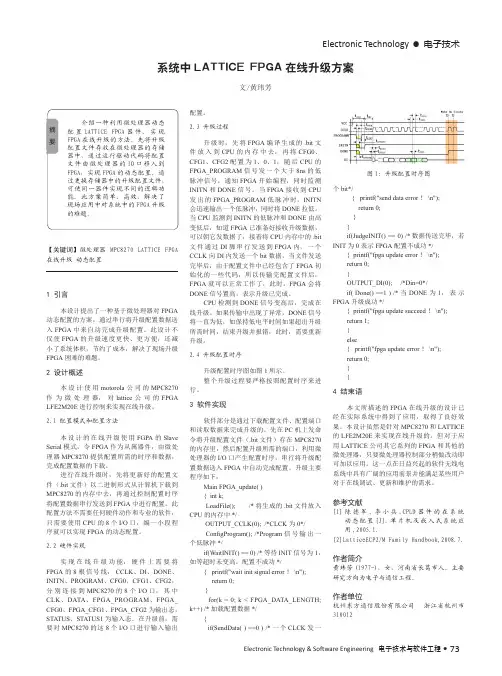

Electronic Technology •电子技术Electronic Technology & Software Engineering 电子技术与软件工程• 73【关键词】微处理器 MPC8270 LATTICE FPGA在线升级 动态配置1 引言本设计提出了一种基于微处理器对FPGA动态配置的方案,通过串行将升级配置数据送入FPGA 中来自动完成升级配置。

此设计不仅使FPGA 的升级速度更快、更方便,还减小了系统体积,节约了成本,解决了现场升级FPGA 困难的难题。

2 设计概述本设计使用motorola 公司的MPC8270作为微处理器,对lattice 公司的FPGALFE2M20E 进行控制来实现在线升级。

2.1 配置模式和配置方法本设计的在线升级使用FGPA 的SlaveSerial 模式,令FPGA 作为从属器件,由微处理器MPC8270提供配置所需的时序和数据,完成配置数据的下载。

进行在线升级时,先将更新好的配置文件(.bit 文件)以二进制形式从计算机下载到MPC8270的内存中去,再通过控制配置时序将配置数据串行发送到FPGA 中进行配置。

此配置方法不需要任何硬件动作和专业的软件,只需要使用CPU 的8个I/O 口,编一小段程序就可以实现FPGA 的动态配置。

2.2 硬件实现实现在线升级功能,硬件上需要将FPGA 的8根信号线: CCLK 、DI 、DONE 、INITN 、PROGRAM 、CFG0、CFG1、CFG2,分别连接到MPC8270的8个I/O 口,其中CLK 、DATA 、FPGA_PROGRAM 、FPGA_CFG0、FPGA_CFG1、FPGA_CFG2为输出态,STATUS 、STATUS1为输入态。

在升级前,需要对MPC8270的这8个I/O 口进行输入输出系统中LATTICE FPGA 在线升级方案文/黄玮芳配置。

2.3 升级过程升级时,先将FPGA 编译生成的.bit 文件放入到CPU 的内存中去,再将CFG0、CFG1、CFG2配置为1、0、1,随后CPU 的FPGA_PROGRAM 信号发一个大于8ns 的低脉冲信号,通知FPGA 开始编程,同时监测INITN 和DONE 信号。

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。

FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。

FPGA的加载模式主要有以下几种:1).PS模式(Passive Serial Configuration Mode),即被动串行加载模式。

PS模式适合于逻辑规模小,对加载速度要求不高的FPGA加载场合。

在此模式下,加载所需的配置时钟信号CCLK由FPGA外部时钟源或外部控制信号提供。

另外,PS加载模式需要外部微控制器的支持。

2).AS模式(Active Serial Configuration Mode),即主动串行加载模式。

在AS 模式下,FPGA主动从外部存储设备中读取逻辑信息来为自己进行配置,此模式的配置时钟信号CCLK由FPGA内部提供。

3).PP模式(Passive Parallel Configuration Mode),即被动并行加载模式。

此模式适合于逻辑规模较大,对加载速度要求较高的FPGA加载场合。

PP模式下,外部设备通过8bit并行数据线对FPGA进行逻辑加载,CCLK信号由外部提供。

4).BS模式(Boundary Scan Configuration Mode),即边界扫描加载模式。

也就是我们通常所说的JTAG加载模式。

所有的FPGA芯片都有三个或四个加载模式配置管脚,通过配置来选取不同的加载模式。

首先来介绍下PS加载模式,各个厂商FPGA产品的PS加载端口定义存在一些差异,下面就对目前主流的三个FPGA厂商Altera, Xilinx,Lattice的PS加载方式进行一一介绍。

Altera公司的FPGA产品PS加载接口如下图所示。

1).CONFIG_DONE:加载完成指示输出信号,I/O接口,高有效,实际使用中通过4.7K电阻上拉到VCC,使其默认状态为高电平,表示芯片已加载完毕,当FPGA正在加载时,会将其驱动为低电平。

网络边缘智能化?这家FPGA 都准备好了!

FPGA 向来是高大上的形象,即便在人工智能火热的今天,围绕FPGA 讨论的焦点也集中在云端的加速,与之相提并论的,更多是以高性能计算见长

的GPU、CPU、DSP。

但是,有家公司,却专注在“网络边缘端”,将产品布局在适于低功耗运行的

低密度FPGA 上,其全新的毫瓦级功耗FPGA 解决方案—— Lattice senAI , 为机器学习推理在大众市场物联网应用中实现快速部署创造机遇,且听莱迪思半导体亚太区资深事业发展经理陈英仁娓娓道来。

莱迪思半导体亚太区资深事业发展经理陈英仁

快速兴起的网络边缘计算

提及AI 或智能计算,我们更多会想到“云端的加速”。

但并非所有应用都将

在云端运行。

莱迪思《加速实现网络边缘低功耗人工智能应用》白皮书中表明,另一轮从集中式到分布式的系统架构转变的征兆已经显而易见了,无论到来与否,有一点确信无疑,那就是低延迟要求、不断加剧的隐私问题和通信带宽限制,将驱动网络边缘对智能化的需求。

陈英仁以智能音响为例,集合了语音控制、摄像头检测功能的智能音响,可以为生活带来更多的便利性,但也正由于

存在摄像头、麦克风,隐私暴露就成为大家担心的问题。

如果这时在终端加入

数据处理和分析功能,就可以很好地对隐私进行保护。

此外,终端的很多应用

是需要低延迟的,甚至有时在没有网络的情况下,也需要保证在线下进行及时

的反馈,这时也需要终端数据处理的加入。

这样的需求有多大?Gartner 分析表示:“目前企业产品的数据约有10% 都在传统的集中式数据中心或云端以外的地方处理,到2022 年,这一数据将会。

ispLEVER使用指南 (Lattice FPGA部分)1.介绍1.1 简介该使用指南适用于初次使用ispLEVER软件或者不常使用该软件的工程设计人员,它可以帮助你去了解不同的处理过程,使用各种工具,以及熟悉ispLEVER产生的各种报告。

在进行下一步时,可以准备一个设计,以此去了解设计的仿真,功耗的计算,静态时序分析,以及以时序驱动的布局和布线,检查由软件输出的报告等。

以此设计为例,你可以练习约束设计的输入,输出信号以及这些信号管脚的分配去满足系统要求。

也可以修改约束条件,达到最佳地利用LatticeEC的结构和资源,同时实现高性能。

该使用指南覆盖了绝大部分通常的流程和软件选项,那些更大的,时序要求更严的设计则需要更精细的控制才能满足你对性能和资源利用率要求的目标,在此之前,你必须对这些基本的有所了解和掌握。

1.2 目标当你读完该使用指南时,你有能力完成以下的任务:1.使用ispLEVER软件创建一个新的Verilog语言的工程目录,选定你的目标器件,并利用Project Navigator在该工程目录中添加Verilog HDL源代码。

2.生成一个sysCLOCK 锁相环(PLL)模块,并把它添加到该工程路径中,利用Module/IP Manager和文本编译器(Text Editor)将该PLL模块添加到源代码中。

3.在器件的管脚上锁定相应的信号,利用参数编译器(Preference Editor)定义信号的频率周期和时钟到输出(Clock-to-out)的时间。

4.利用映射(Mapping),布局(Placing),布线(Routing)等工具来完成设计。

同时,利用Project Navigator检查结果报告。

5.了解静态时序分析报告,调整设计去满足设计的时序要求。

6.修改和重新设置约束条件去满足设计的性能要求。

7.使用Floorplanner来检查器件的实现情况,以及相应的布线阻塞情况,可编程单元(PFU)的利用率。

FPGA硬件电路设计及FPGA平台介绍FPGA(Field Programmable Gate Array)是一种可现场编程的可编程逻辑器件。

与传统的ASIC(Application-Specific Integrated Circuit)硬件设计相比,FPGA具有更高的灵活性和可重构性。

在FPGA上进行硬件电路设计,可以在设计阶段进行修改和优化,避免了传统ASIC设计中勘误的成本和延迟。

本文将介绍FPGA硬件电路设计的基本原理和方法,并介绍常用的FPGA开发平台。

一、FPGA硬件电路设计原理FPGA是由可编程逻辑单元(PLU)和可编程互连资源(IOB)组成的。

PLU通常由可编程查找表(LUT)和触发器(Flip-flop)构成,用于实现组合逻辑和时序逻辑。

IOB用于将FPGA与外部设备连接起来,包括输入输出引脚和时钟管理单元。

二、FPGA硬件电路设计方法FPGA硬件电路设计可以采用自顶向下和自底向上两种方法。

自顶向下方法是从整体到部分,先设计电路的顶层结构,然后逐步设计下层模块,最后实现具体的逻辑。

自底向上方法是从部分到整体,先设计底层模块,然后逐步组合成高层模块和最终的电路。

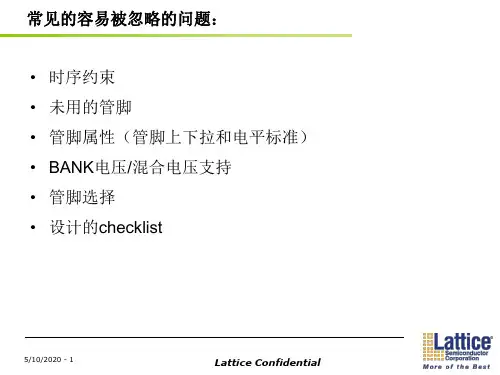

在设计FPGA硬件电路时,还需要考虑如下几个关键问题:1.时序约束:为了确保电路在FPGA上能够正常运行,需要对电路的时序行为进行约束。

时序约束包括输入输出时钟频率、最小间隔时间等。

通过约束工具将时序约束应用到设计中,可以帮助自动布线工具生成符合时序要求的布局。

2.优化策略:FPGA硬件电路设计中常见的优化策略包括逻辑优化和布局优化。

逻辑优化可以通过改进硬件描述代码、优化逻辑等方法来减少逻辑资源和提高性能。

布局优化可以通过调整电路的物理布局来减少时序延迟和功耗。

3.仿真测试:在将FPGA硬件电路部署到实际芯片之前,可以使用仿真工具对设计进行功能验证和时序验证。

仿真测试可以帮助发现和解决设计中的问题,确保设计的正确性和可靠性。

Lattice低成本低功耗ECP4FPGA系列

佚名

【期刊名称】《电子产品世界》

【年(卷),期】2011(18)12

【摘要】Lattice ECP4 FPGA系列,具有6Gbps的SERDES采用低成本wire—bond封装,功能强大的DSP块和具有基于硬IP的通信引擎,适用于成本和功耗敏感的无线、有线、视频和计算市场。

【总页数】1页(P70-70)

【关键词】Lattice;低成本;低功耗;SERDES;FPGA;通信引擎;封装;无线

【正文语种】中文

【中图分类】TN6

【相关文献】

1.一种基于Lattice ispMACH4000Z系列CPLD的低功耗时间测量方法 [J], 果红军;刘秀红

tticeECP4系列重新定义低成本、低功耗FPGA [J], 丛秋波

ttice推出LatticeECP2低成本FPGA系列产品 [J], 无

ttice ECP5-5G系列低功耗无缝连接解决方案 [J],

ttice CrossLink-NX系列低功耗FPGA开发方案 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

为什么Lattice在进入FPGA市场的第一年就能取得这么好的成绩?我想这里面可能有三个层次的深层原因:第一,针对Altera和Xilinx在高端有Stratix和Virtex、在低端有Cyclone和Spartan产品的情况下,我们选择了从中端切入的策略,从而在刚进入FPGA应用市场时能够有效地避免与已在高端和低端市场确立了自己领导地位的Altera和Xilinx发生正面冲撞,二年多来的实践证明这一策略是非常正确的;第二,我们在满足市场要求的严格质量前提下做出了自己的产品特色,例如,我们的低端LatticeECP2/M FPGA产品在保持对Cyclone和Spartan价格竞争力的前提下,再增加了一些切合用户实际应用需要而主要竞争对手还没有的功能,如更多的高速串行接口、更多的I/O口、128位AES加密和更大的内部存储空间等;第三,系统制造商心里也期望市场能涌现出较强的第3个FPGA供应商,因为这样才能形成稳定的三足鼎立之势,促进市场的有序竞争,并帮助它们稳定供应链和进一步降低运营成本。

目前FPGA和CPLD在哪些主要应用空间具有不可替代的关键地位?目前FPGA和CPLD的目标应用主要可分为以下三大类:低成本应用、对价格敏感的高性能应用、以及需要极高性能的应用。

第一类应用包括等离子或LCD TV、VoIP、机顶盒、图像渲染、音频处理和控制逻辑,第二类应用包括企业联网、GPON、企业存储、无线基站、协议转换、网络交换、图像滤波和存储器桥接,第三类应用包括光纤联网、SDH线路卡、下一代40G光通道卡、局域网交换机、DDR3存储器测试仪、高端服务器、背板高速接口、数据包成帧和分拆、高速存储器控制和高速信号处理。

Lattice目前主要有哪几条产品线?它们各针对什么目标应用?Lattice目前主要有4条产品线:针对低端市场的低成本FPGA LatticeECP2/M、针对高端市场的系统级高性能FPGA LatticeSC/M、带嵌入式闪存的非易失性FPGA LatticeXP和MachXO、以及混合信号PLD ispClock和Power Manager II,LatticeECP2和LatticeECP2M的主要区别是后者还带有SRAM存储器,LatticeSC和LatticeSCM的主要区别也一样。

LatticeECP2的目标市场是第一类低成本应用,它主要与Cyclone和Spartan进行竞争。

LatticeECP2M的目标市场是第二类应用,它主要与Stratix和Virtex进行竞争。

LatticeSC/M的目标市场是第三类应用,它主要与Stratix-GX和Virtex-FXT进行竞争。

LatticeXP带有闪存,因此它特别适用于对瞬时上电、安全性和现场逻辑升级能力有特殊要求的应用。

MachXO系列产品将CPLD和FPGA的特性组合在一起,特别适用于诸如总线桥接、总线接口和控制等应用(传统上,这些应用大都采用CPLD或者低容量的FPGA来实现)。

Lattice的可编程混合信号器件Power Manager II 和ispClock分别将电源管理和时钟管理器件与CPLD集成在一起,它们的设计应用目标是尽可能地消除PCB板上的分立器件和降低系统设计风险。

Lattice目前4条主要产品线的性能特点和应用特点分别是什么?这4条主要产品线都根据它们的目标应用进行了特别的性能优化。

具体来说,LatticeECP2/M 低成本FPGA系列重新定义了低成本FPGA,集成了以前只有高成本、高性能FPGA才有的特点和性能,使其在更低的成本下拥有更多最佳的FPGA特性,例如,LatticeECP2具有高达1.1M 位的RAM块、533Mbps DDR/DDR2控制接口、128位AES加密,支持双重引导、高达36×36宽度的sysDSP块、750Mbps速率的SPI4.2以及840Mbps的普通接口;LatticeECP2M具有高达5.3M位的RAM块、16个3.125Gbps的高速SERDES、每个信道的功耗低至100mW,支持PCIe、CPRI、SRIO、SATA、1GbE和FC等多个其它标准。

LatticeSC/M根据当今基于连结的高速系统的要求而设计,是针对当今高性能通信应用的系统级解决方案,它具有15K至115K四输入查找表、139至942 I/O、700MHz全局时钟、1GHz 边沿时钟、4至32个600Mbps至3.8Gbps SERDES、SPI 5、SONET、XAUI、1~7.8Mb嵌入式RAM块(500MHz)、额外的240K至1.8Mb分布式RAM,每个LatticeSC/M器件具有8个PLL,工作频率高达1GHz。

针对低成本、系统级的集成,LatticeSCM系列还提供了低功耗、低成本的结构化ASIC块(即工程预制的IP块MACO),目前可提供的工程预制IP块包括PCIe、SPI4.2、GbE和DDR。

LatticeXP FPGA和MachXO跨越式PLD最大的性能特点是可满足许多重要应用的无缝在系统更新要求。

我们知道,一个应用要提供无缝在系统更新能力必须满足四个要求。

首先,它必须能够通过一个嵌入式的微处理器来在系统更新逻辑。

其次,总体配置时间必须相对较短。

再次,在更新过程中,必须能够控制器件的I/O。

最后,在配置完成之后、I/O控制交还用户之前,必须对器件状态进行初始化。

LatticeXP和MachXO具有目前业内唯一能够满足无缝现场逻辑升级要求的双重SRAM和Flash配置空间结构。

这种双重的配置空间可以将FPGA 无法处理输入的时间降低到小于2ms,比其它解决方案小了一个数量级。

此外,边界扫描及编程电路的独特性能使得器件能够在FPGA或PLD恢复正常工作之前,被初始化到一个恰当的状态。

现场逻辑升级可以让设计者修复缺陷、对标准的改变做出反应、升级设备以及增加额外的服务,它使得系统开发人员拥有空前的灵活性,也因此越来越多地成为众多应用的必备性能。

与此同时,对系统可靠运行时间的要求提高到“5个九”(99.999%)的应用也在不断增加,LatticeXP和MachXO的TransFR是目前业界唯一的一种能在不中断系统运行的情况下更新逻辑的解决方案。

Power Manager II集成了智能电源定序和精密故障监控技术,具有采用数字闭环技术实现的电源电压裕量控制及调整功能,而且所有这些都实现在一个单片低成本芯片中!ispPAC电源管理器件Power Manager II综合了Lattice创新的ispPAC和CPLD工艺,其可编程的模拟输入能为多个供电节点(最多达12个)提供精确的同步监控,与此同时耐用的片内CPLD又能最有效地产生控制信号,用于电源定序和监控信号的产生。

IspClock系列器件提供了一个创新的复杂时钟网络解决方案,它的主要设计目标就是尽可能地简化当前的多时钟树网络设计,以尽可能地不使用各种零延时缓冲器、扇出缓冲器、终端电阻器、延时线以及弯曲的时钟走线布局!ispClock器件能够被编程而产生多个时钟频率,对每个输出进行时钟走线长度差异的补偿,精确地匹配走线阻抗并且用不同的信号要求来驱动时钟网络,而且所有这些都是在满足严格的相偏和抖动标准的情况下!Lattice计划什么时候推出65nm FPGA?与我们的主要竞争对手不同,Lattice在公开新产品的开发信息方面是比较保守的,虽然我们一直在进行65nm FPGA的研发,但在没有正式量产前,我们一般不会向外公开发布这方面的信息。

你认为导致Lattice当年在PLD市场急剧下滑的主要原因是什么?要说清楚这个问题,首先我们应了解PLD市场的结构。

在上世纪八十年代到九十年代初期,整个PLD市场的分布结构为:CPLD占70%,FPGA仅占30%,可是到了今天,这一市场分布结构已彻底颠倒过来,变成CPLD仅占10-15%,而FPGA则占到85-90%。

在上世纪八十年代,Lattice一直在CPLD供应市场上保持着技术领先者的角色,也许是这一领先角色带来的优越感让当时Lattice的管理层产生了一个战略幻觉,即CPLD在未来仍将主导PLD市场的发展,并由此做出了一个现时看来战略性的错误决策,即花5亿现金在1999年收购了AMD旗下专攻可编程逻辑器件的全资子公司Vantis,以全力保持和增强在CPLD产品市场的技术领先地位。

收购完这家公司以后不久,PLD市场开始急剧地一面倒向FPGA。

但此时的Lattice已再无余力投资FPGA产品的开发,只能心不甘情不愿地眼睁睁看着Altera和Xilinx一天天坐大。

非易失 FPGA∙LatticeXP2 FPGA 器件将LatticeECP2的基本结构与一种低成本的90纳米的闪存FPGA 工艺组合在一个被称为flexiFLASH的结构中。

flexiFLASH方式提供了许多便利,诸如:瞬时上电、小的芯片面积、采用FlashBAK™嵌入式存储器块的片上存储器、串行TAG存储器、设计安全性等。

LatticeXP2器件还支持采用TransFR的现场升级(Live Updates)、128位的AES加密以及双引导技术。

∙Lattice's MachXO 系列为传统上使用CPLD的应用提供了一种非易失、低成本、低密度、瞬时上电的高性能的逻辑解决方案。

该系列具有高引脚/逻辑比,非常适用于粘合逻辑、总线桥接、总线接口、上电控制和控制逻辑。

∙LatticeXP (eXpanded Programmability) FPGA 器件将LatticeEC FPGA结构和低成本的130纳米Flash FPGA技术合成在单个芯片上:瞬时上电(配置时间< 1毫秒),非易失存储器(片上的Flash,无外部引导PROM),高安全性(无外部配置位流),并且可无限重复配置(SRAM FPGA结构)。

∙Lattice的ispXPGA FPGA 器件将E2非易失单元和基于4输入查找表的FPGA结构以及800Mbps的SERDES功能结合在一起,用于高速串行IO FPGA设计。

LatticeECP3 FPGA产品系列选择指南器件SERDES 信道数(最大值)18 x 18 乘法器LUT数(k)分布式RAM (K)EBR SRAM块(K)EBR SRAM(Mbits)最大用户I/OPLL/DLL数ECP3-174 24 17 36 552 30 222 4/2 ECP3-354 68 33 68 1327 72 310 4/2 ECP3-7012 128 67 145 4420 240 490 10/2 ECP3-9512 128 92 188 4420 240 490 10/2 ECP3-15016 320 149 303 6850 372 586 10/2LatticeSC FPGA 产品系列选择指南器件SERDES 信道数(最大值)结构化的ASIC块(最大值)LUT数(k)Dist. RAM(Mbits)EBR SRAM(Mbits)EBRSRAM块最大用户 I/OPLL/DLL数LFSC158 4 15.2 0.24 1.03 56 300 8/12 LFSC2516 6 25.4 0.41 1.92 104 484 8/12 LFSC4016 10 40.4 0.65 3.98 216 562 8/12 LFSC8032 10 80.1 1.28 5.68 308 904 8/12 LFSC11532 12 115.2 1.84 7.80 424 942 8/12 LatticeECP2(包含S-系列)FPGA 产品系列选择指南器件sysDSP块18 x 18 乘法器LUT数(K)Dist. RAM(KBits)EBR SRAM(KBits)EBR SRAM块最大用户I/OPLL/DLL数LFECP2-63 12 6 12 55 3 190 2/2 LFECP2-12624 12 24 221 12 297 2/2 LFECP2-20728 21 42 277 15 402 2/2 LFECP2-35832 32 65 332 18 450 2/2 LFECP2-5018 72 48 96 387 21 500 4/2 LFECP2-7022 88 68 136 1032 56 583 6/2 LatticeECP2M (包含S-系列)FPGA 产品系列选择指南器件SERDES信道数(最大值)18 x 18 乘法器LUT(K)分布式 RAM(K)EBR 块 SRAM(K)EBR SRAM块最大用户I/OPLL/DLLECP2M-204 24 19 41 1217 66 304 8/2 ECP2M-354 32 34 71 2101 114 410 8/2 ECP2M-508 88 48 101 4147 225 410 8/2 ECP2M-7016 96 67 145 4534 246 436 8/2 ECP2M-10016 168 85 202 5308 288 616 8/2 LatticeECP 和 EC(包含S-系列)FPGA 产品系列选择指南器件sysDSP块*18 x 18 嵌入式乘法器*LUT(K)分布式 RAM(K)EBR 块 SRAM(K)EBR SRAM块最大用户I/OPLLEC1- - 1.5 6 18 2 112 2 EC3- - 3.1 12 55 6 160 2 ECP6/EC6 4 16 6.1 25 92 10 224 2 ECP10/EC105 20 10.2 41 277 30 288 4 ECP15/EC156 24 15.4 61 350 38 352 4 ECP20/EC207 28 19.7 79 424 46 400 4 ECP33/EC338 32 32.8 131 535 58 496 4* 仅对ECP 器件LatticeXP2 FPGA产品系列选择指南器件sysDSP块18 x 18 乘法器LUT(K)分布式RAM(K)EBR块SRAM(K)EBR SRAM块数最大用户I/OPLLXP2-53 12 5 10 166 9 172 2 XP2-84 16 8 18 221 12 201 2 XP2-175 20 17 35 276 15 358 4 XP2-307 28 29 56 387 21 472 4 XP2-408 32 40 83 885 48 540 4MachXO 产品系列选择指南器件PLL LUT EBR SRAM 块EBR 块 SRAM (K) 分布式 RAM (K) 最大用户 I/OLCMXO2560 256 0 0 2.0 78LCMXO6400 640 0 0 6.1 159LCMXO12001 1200 1 9 6.4 211LCMXO22802 2280 3 27 7.7 271LatticeXP FPGA 产品系列选择指南器件LUT (K) 分布式 RAM (K) EBR 块 SRAM (K) EBR SRAM 块数目最大用户I/O PLL LFXP33.1 12 54 6 136 2 LFXP65.8 23 90 10 188 2 LFXP109.7 39 216 24 244 4 LFXP1515.4 61 288 32 300 4 LFXP2019.7 79 414 46 340 4。