FPGA全面介绍PPT

- 格式:ppt

- 大小:6.72 MB

- 文档页数:35

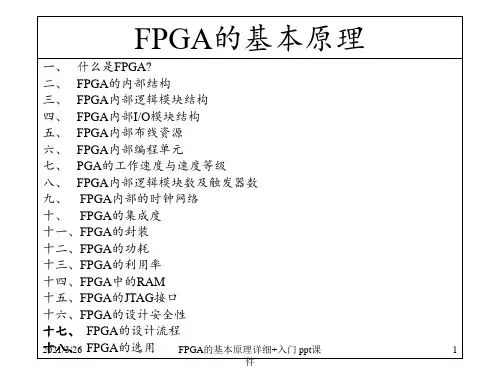

数字电路与系统东南大学信息科学与工程学院第九章可编程逻辑器件可编程逻辑器件的基本结构和电路表示方法 可编程逻辑阵列PLA可编程阵列逻辑PAL通用阵列逻辑GAL复杂可编程逻辑器件CPLD现场可编程门阵列FPGA9.6.1 FPGA的基本结构◆结构组成:由三个可编程基本模块阵列组成,输入/输出块IOB(Input / Output Block)阵列、可配置逻辑块CLB(Configurable Logic Block)阵列及可编程互连网络PI(Programmable Interconnection)结构特点:FPGA的可配置逻辑块不像CPLD的LAB那么复杂,但是其数量很多,一些大型的FPGA含有数万个可配置逻辑模块。

输入/输出块围绕着CLB分布,其可以配置为输入、输出或者双向传输,用来与外部器件进行数据传输。

分布式的可编程互连网络提供了CLB与输入/输出的连接。

FPGA的基本结构9.6.2 可编程逻辑块(CLB)结构◆FPGA的CLB一般由数个小型的逻辑单元构成,类似于CPLD中的宏单元。

如图所示为CLB的基本结构图,每个CLB均被可编程互连网络围绕,用于跟其他的CLB相连接。

CLB的基本结构CLB中的逻辑单元可配置为组合逻辑电路、时序逻辑电路或者这二者的混合。

一个典型的基于查找表(LUT,look-up table)的逻辑单元的结构图如图所示。

◆LUT是一种可编程存储器,可以用来产生与或形式的组合逻辑函数,其功能与PAL或PLA类似。

◆LUT通常由2n个内存单元构成,n为输入变量的个数。

◆例如,3个输入变量可以寻址8个内存单元,所以一个有3个输入的变量的LUT可以生成8个与项的与或形式的逻辑函数。

根据输入变量的取值,可以向对应的内存单元内写入0或1,以实现对LUT的编程,如图所示。

◆每一个“1”表示在与或函数式中含有该与项,“0”表示在与或函数式中不包含该与项,因此该图中所示的LUT 对应的逻辑函数式为:在此处键入公式。