Altera FPGA介绍

- 格式:pdf

- 大小:5.22 MB

- 文档页数:72

FPGA配置模式时间:2011-09-12 23:15:16 来源:作者:FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

如何实现快速的时序收敛、降低功耗和成本、优化时钟管理并降低FPGA与PCB并行设计的复杂性等问题,一直是采用FPGA的系统设计工程师需要考虑的关键问题。

如今,随着FPGA向更高密度、更大容量、更低功耗和集成更多IP的方向发展,系统设计工程师在从这些优异性能获益的同时,不得不面对由于FPGA前所未有的性能和能力水平而带来的新的设计挑战。

在很多项目设计中采用Altera 公司基于SRAM架构Cyclone系列器件。

Cyclone器件与其他FPGA器件一样是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。

这些配置数据可通过多种模式加载到FPGA内部的SRAM中,由于SRAM的易失性,每次上电时,都必须对FPGA进行重新配置。

1 Cyclone FPGA 配置模式Cyclone系列FPGA器件配置方案主要有三种,包括使用低成本配置芯片的主动串行(AS)配置、被动串行(PS)配置以及基于JTAG配置,实际应用时可以使用其中的一种方案配置Cyclone系列FPGA器件,来实现用户编程所要实现的功能。

Cyclone系列FPGA器件是用SRAM单元配置数据的。

由于SRAM掉电后容易丢失数据,配置数据必须即时地下载到上电的Cyclone器件中。

不同的配置模式可采用不同的专用配置芯片或数据源这三种配置模式是由Cyclone器件的模式选择引脚MSEL1和MSEL0的高低电平来决定的,如果你的实际应用只要求单一的配置模式,可以把模式选择引脚连接到VCC端或接地端在切换引脚的过程中,器件的运行状态不会被影响。

FPGA开发板FPGA开发板ALTERA FPGA是世界上十几家生产CPLD/FPGA的公司中最大的可编程逻辑器件供应商之一,生产的FPGA产品有:FLEX6000/8000/10K、APEX20K、ACEX1K、APEXⅡ、Mercury、Excalibur、Cyclone、Stratix、CycloneⅡ和StratixⅡ等系列。

Altera的FPGA器件采用钢铝布线的先进CMOS技术,具有非常低的功耗和相当高的速度,而且采用连续式互连结构,提供快速的、连续的信号延时。

Altera器件密度从300门到400万门,能很容易地集成现有的各种逻辑器件,高集成度的FPGA提供更高的系统性能,更高的可靠性,更高的性能价格比。

Altera Cyclone系列FPGA是Altera公司2003年9月份推出的,基于1.5V,0.13μm 工艺,Cyclone 是一个性价比很高的FPGA系列。

其中EP1C3T144是Cyclone系列中的一员,共有2910逻辑单元,59904RAM bits,1个PLLs,最多有104个用户I/O,可以说这款FPGA的资源非常丰富,足够满足大型设计的需要。

本公司因此特推出Cyclone EP1C3T144C8 FPGA开发板,该开发板功能强大,接口丰富,可做大型综合实验。

FPGA开发板硬件资源主要有:1、Altera EP1C3T144C8 FPGA芯片2、Altera 串行配置芯片EPCS13、DAC0832芯片4、ADC0809芯片5、液晶接口6、TP3057PCM编解码芯片7、八位高亮数码管8、八位拨码开关9、4×4阵列键盘10、4个复位轻触按键11、9个高亮发光二极管(红、绿、黄色各三灯)12、双刀双掷继电器13、异步通信串口(UART)14、双有源晶振(24MHz和32.768MHz)15、5V,3.3V,1.5V电源管理系统FPGA开发板带以下DEMO程序:1、FPGA实现流水灯实验2、FPGA实现电子钟实验3、FPGA实现串口发送实验4、FPGA实现串口接收、点阵显示实验5、FPGA实现矩阵键盘和点阵显示(实时扫描方式)6、FPGA实现矩阵键盘和数码管显示(延时扫描方式)7、FPGA实现AD转换、数码显示和拨码选择通道实验8、FPGA实现DA转换,产生锯齿、三角、正弦波;拨码开关选择波形9、FPGA实现液晶显示(并行控制)10、FPGA实现液晶显示(串行控制)11、FPGA实现TP3057音频编解码12、简单密码锁实验(按键+继电器实验)FPGA开发板上的所有模块单元都已连线,省去了连线的烦恼,同时FPGA芯片所有可用I/O都通过自锁紧插座引出,方便做扩展实验,而且FPGA芯片由于管脚密集,在引脚插座旁都标有对应的管脚号,使您对所用的管脚一目了然。

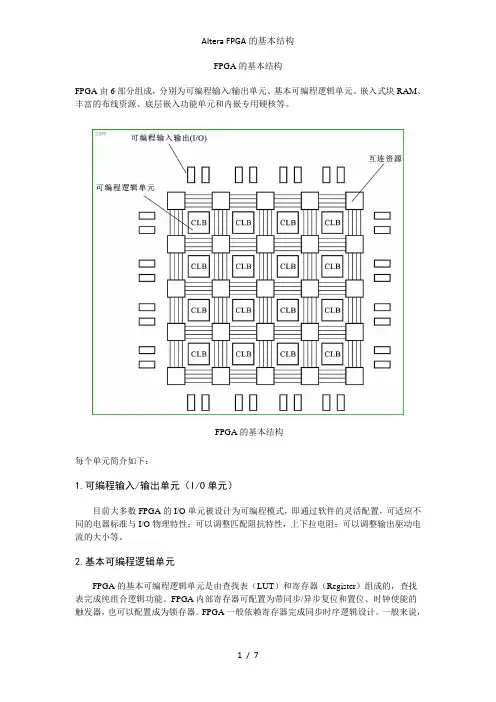

FPGA的基本结构FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

FPGA的基本结构每个单元简介如下:1.可编程输入/输出单元(I/O单元)目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可适应不同的电器标准与I/O物理特性;可以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。

2.基本可编程逻辑单元FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。

FPGA内部寄存器可配置为带同步/异步复位和置位、时钟使能的触发器,也可以配置成为锁存器。

FPGA一般依赖寄存器完成同步时序逻辑设计。

一般来说,比较经典的基本可编程单元的配置是一个寄存器加一个查找表,但不同厂商的寄存器和查找表的内部结构有一定的差异,而且寄存器和查找表的组合模式也不同。

学习底层配置单元的LUT和Register比率的一个重要意义在于器件选型和规模估算。

由于FPGA内部除了基本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL,专用的Hard IP Core等,这些模块也能等效出一定规模的系统门,所以简单科学的方法是用器件的Register或LUT的数量衡量。

3.嵌入式块RAM目前大多数FPGA都有内嵌的块RAM。

嵌入式块RAM可以配置为单端口RAM、双端口RAM、伪双端口RAM、CAM、FIFO等存储结构。

CAM,即为内容地址存储器。

写入CAM的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所有内部数据的地址。

简单的说,RAM是一种写地址,读数据的存储单元;CAM与RAM恰恰相反。

除了块RAM,Xilinx和Lattice的FPGA还可以灵活地将LUT配置成RAM、ROM、FI FO等存储结构。

4.丰富的布线资源布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。

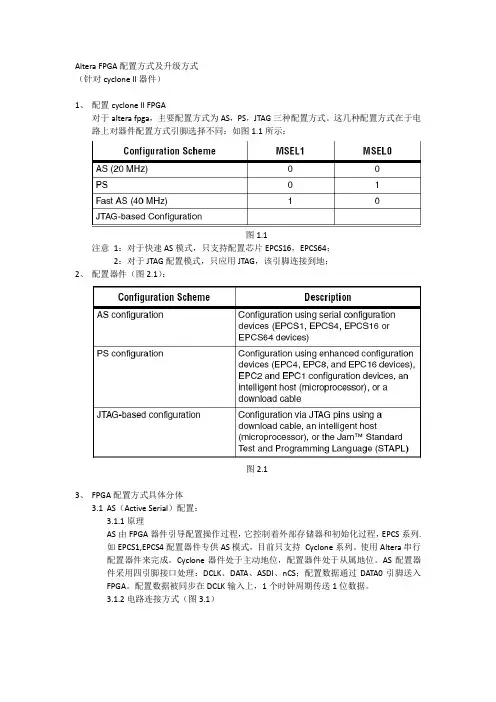

Altera FPGA配置方式及升级方式(针对cyclone II器件)1、配置cyclone II FPGA对于altera fpga,主要配置方式为AS,PS,JTAG三种配置方式。

这几种配置方式在于电路上对器件配置方式引脚选择不同:如图1.1所示:图1.1注意1:对于快速AS模式,只支持配置芯片EPCS16,EPCS64;2:对于JTAG配置模式,只应用JTAG,该引脚连接到地;2、配置器件(图2.1):图2.13、FPGA配置方式具体分体3.1AS(Active Serial)配置:3.1.1原理AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

AS配置器件采用四引脚接口处理:DCLK、DATA、ASDI、nCS;配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

3.1.2电路连接方式(图3.1)图3.13.1.3配置时序(图3.2)图3.2在配置完成后到初始化完成所需要299个时钟周期(100M)3.1.4配置文件.pof .jic .rbf3.2PS(Passive Serial)配置方式3.2.1配置原理主动串行配置方式可以通过altera配置器件,一个下载电缆,或者通过一个主控制器,诸如MAX II器件、MCU等来配置FPGA。

配置数据通过DATA0在每个DCLK的上升沿送入器件。

FPGA配置方式选择引脚配置如图3.3所示图3.33.2.2电路连接:配置器件配置(图3.4)图3.4MAX II配置,图3.5图3.5MCU配置,图3.6图图3.63.2.3配置时序图3.73.2.4配置文件格式.rbf .hex .ttf3.3JTAG配置方式3.3.1原理对于cyclone II器件来说,JTAG配置方式优先于其他器件配置方式。

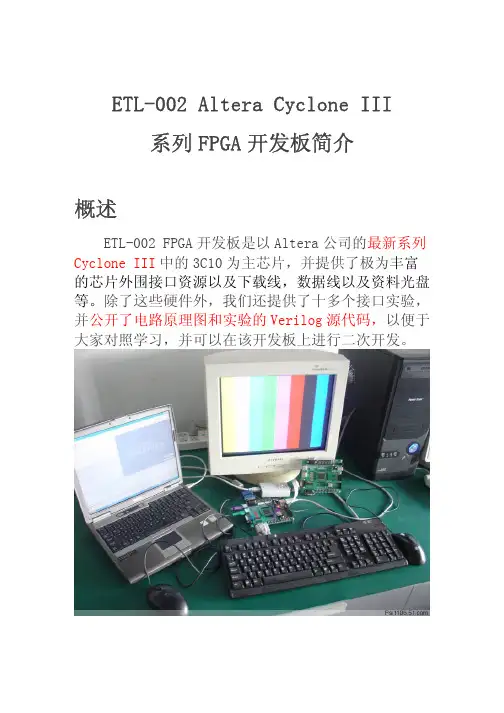

ETL-002 Altera Cyclone III系列FPGA开发板简介概述ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。

除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。

开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。

开发板同时支持AS模式下载和JTAG模式下载。

程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。

丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。

这些接口主要包括:PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。

开发板自带了动态彩条显示的功能双串口接口:可以与任何的串口设备相接。

开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。

开发板自带的演示程序实时地显示分钟和秒钟的信息。

4位LED灯:用于指示状态。

开发板自带了跑马灯实验。

4位按键开关:可用于复位等作用。

4位拨码开关:可用于电路的选择作用教学实验除了开发板的丰富的硬件资源外,我们还提供了数十个学习实验。

通过这些实验,您可以学习FPGA芯片,Quartus II软件和设计仿真和下载等FPGA的设计流程,然后将试验中程序执行的信息通过数码管,LED 灯,串口等板上的硬件直观的显示出来。

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Altera公司是一家知名的半导体公司,致力于生产和销售可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)等产品。

下面将列举Altera公司旗下的CPLD和FPGA产品,帮助大家更好地了解这家公司的产品线。

一、CPLD产品线1. MAX 7000系列MAX 7000系列是Altera公司推出的一款CPLD产品,具有低功耗、高性能和可编程性强的特点。

该系列产品广泛应用于通信、工业控制、汽车电子等领域,为客户提供了稳定可靠的解决方案。

2. MAX 9000系列MAX 9000系列是Altera公司的另一款CPLD产品,采用了先进的CMOS工艺和可编程逻辑单元,具有高密度、可靠性高的特点。

该系列产品在航空航天、国防安全、医疗设备等领域有着广泛的应用。

二、FPGA产品线1. Stratix系列Stratix系列是Altera公司旗下最为知名的FPGA产品之一,拥有高速、高密度、低功耗等特点,适用于需要大规模数据处理和高性能计算的应用场景。

该系列产品常用于人工智能、云计算、数据中心等领域。

2. Cyclone系列Cyclone系列是Altera公司针对中小规模应用市场推出的FPGA产品,具有低成本、低功耗、高性能等特点。

该系列产品在嵌入式系统、工业自动化、网络通信等领域有着广泛的应用。

3. Arria系列Arria系列是Altera公司旗下的高性能FPGA产品,具有高速、低功耗、灵活性强等特点,适用于需要高性能和灵活性的应用场景。

该系列产品在无线通信、高性能计算、高清视频等领域有着广泛的应用。

通过以上列举,我们可以看到Altera公司在CPLD和FPGA领域拥有丰富的产品线,为不同领域的客户提供了多样化的解决方案。

期待Altera在未来能够持续推出更多高性能、低功耗的PLD和FPGA产品,满足客户不断增长的需求。

Altera公司作为半导体行业的领军企业,一直以来致力于为全球各行业提供高性能、低功耗的可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)产品。

ALTERA的FPGA命名规则DIP中⽂解释:双列直插式封装。

插装型封装之⼀,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP是最普及的插装型封装,应⽤范围包括标准逻辑IC,存贮器LSI,微机电路等。

PLCC中⽂解释:外形呈正⽅形,32脚封装,四周都有管脚,外形尺⼨⽐DIP封装⼩得多。

PLCC封装适合⽤SMT表⾯安装技术在PCB上安装布线,具有外形尺⼨⼩、可靠性⾼的优点。

PQFP中⽂解释:芯⽚引脚之间距离很⼩,管脚很细,⼀般⼤规模或超⼤规模集成电路采⽤这种封装形式,其引脚数⼀般都在100以上。

SOP中⽂解释:⼩外形封装(SOP)。

以后逐渐派⽣出SOJ(J型引脚⼩外形封装)、TSOP(薄⼩外形封装)、VSOP(甚⼩外形封装)、SSOP(缩⼩型SOP)、TSSOP(薄的缩⼩型SOP)及SOT(⼩外形晶体管)、SOIC(⼩外形集成电路)等。

ALTERA器件命名规则XXX XXX X X XX X1 2 3 4 5 61.前缀: EP典型器件EPC 组成的EPROM器件EPF FLEX 10K或FLFX 6000系列、FLFX 8000系列EPM MAX5000系列、MAX7000系列、MAX9000系列EPX 快闪逻辑器件2.器件型号3.封装形式:D 陶瓷双列直插 Q 塑料四⾯引线扁平封装P 塑料双列直插 R 功率四⾯引线扁平封装S 塑料微型封装 T 薄型J形引线芯⽚载体J 陶瓷J形引线芯⽚载体 W 陶瓷四⾯引线扁平封装L 塑料J形引线芯⽚载体 B 球阵列4.温度范围: C ℃⾄70℃,I -40℃⾄85℃,M -55℃⾄125℃ 5.腿数6.速度以EP2C35F672C6N为例做⼀个说明:EP2C:器件系列ALTERA35:逻辑单元数,35表⽰约有35k的逻辑单元;F:表⽰PCB封装类型,F是FBGA封装,E(EQFP)、Q(PQFP)、U(UBGA)、M(MBGA);Package Type:E: Plastic Enhanced Quad Flat Pack (EQFP)Q: Plastic Quad Flat Pack (PQFP)F: FineLine Ball-Grid Array (FBGA)U: Ultra FineLine Ball-Grid Array (UBGA)M: Micro FineLine Ball-Grid Array (MBGA)672:表⽰引脚数量,C:⼯作温度,C表⽰可以⼯作在0°C到85°C,I表⽰可以⼯作在-40°到100°C,A表⽰可以⼯作在-40°C到125°C;Operating Temperature:C: Commercial temperature (TJ = 0°C to 85°C)I: Industrial temperature (TJ = -40°C to 100°C)A: Automotive temperature (TJ = -40°C to 125°C)6:速度等级,6约最⼤是500Mhz,7约最⼤是43Mhz,8约最⼤是400Mhz;N:后缀,N表⽰⽆铅,ES⼯程样⽚。

FPGA中时钟约束由于是第一次使用FPGA做东西,而且是在完全没有基础的情况下接手了这个项目,所以很多地方设计的并不是很周到,而且遇到了各种各样的问题,最终要以实现项目功能为目的,并把每一个问题解决掉。

在程序一点点的累加上去之后发现警告一直很多,并且有很大一部分是集中在Time这一栏,在分析这一块之前,先介绍一下我那充满了漏洞的系统设计。

FPGA在我的系统中是一个中间环节,主要功能是数据的处理和缓存。

从前端传感器出来的数据经过量化变成数字信号之后就送到了FPGA中,所以FPGA是被动接收前端的数据,FPGA完成了处理之后给后面的CPU发送一个信号,CPU就从FPGA中取出数据。

所以这样FPGA对于前端的传感器和后端的CPU都是被动的,在理论上是可以完成的,但是这样做下来,FPGA没有自己的时钟,无论是前端数据的存入还是后端的数据输出,都是被动的,根据外来的输入时钟完成数据流的传输。

关于时钟的约束部分,我是下载了一份文档,学习的,但是个人感觉文档上面说的很官方化,不是很好理解,而且又是中文的,所以只是挑出其中一些有用的部分在此展现一下。

希望对看官有所帮助。

先看一下有哪一些时钟吧。

时钟(Clocks)使用create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。

生成时钟(Generated Clocks)Quartus II TimeQuest Timing Analyzer可以把修改或改变主时钟(或者引入时钟)特性的分频时钟、波纹时钟和电路作为生成时钟。

可以定义这些电路的输出作为生成时钟。

虚拟时钟(Virtual Clocks)虚拟时钟是一个在设计中没有真正源或者说与设计没有直接关系的一个时钟。

例如,如果一个时钟不是设计中的时钟,而仅仅作为一个外部器件的时钟源,并且外部器件和该设计有输入或者输出的管脚,那么就认为这个时钟是虚拟时钟。

多频时钟(Multi-Frequency Clocks)某些情况下在设计中会有很多个时钟源提供时钟信号。