数字系统设计与VerilogHDL (12)[15页]

- 格式:ppt

- 大小:8.06 MB

- 文档页数:15

数字设计中的Verilog HDL语言基础Verilog HDL语言是数字设计中非常重要的一门编程语言,它被广泛应用于集成电路设计和硬件描述语言。

在数字设计中,Verilog HDL语言被用来描述硬件的行为和结构,使得工程师能够通过编写代码来设计和实现各种数字电路。

Verilog HDL语言具有如下几个基础要素:1. 模块(Module):Verilog HDL语言中的最基本构建单元就是模块,一个模块可以包含端口、输入、输出、内部信号和行为描述等部分。

模块用来描述数字电路中的一个功能模块或组件,它是实现数字电路的基础。

2. 信号(Signal):信号是Verilog HDL语言中用来传递信息的基本元素,它可以是输入信号、输出信号或者中间信号。

信号可以是数字类型、整数类型、浮点数类型等,通过信号的传输和逻辑操作来描述整个数字电路的行为。

3. 端口(Port):端口是模块与外部环境进行通信的接口,它可以是输入端口、输出端口或者双向端口。

端口定义了模块和其他模块或顶层模块之间的信号传输规则,是数字电路的输入输出通道。

4. 运算符(Operator):Verilog HDL语言中包含了各种运算符,用来对信号进行逻辑运算、算术运算和比较运算等操作。

常见的运算符包括与(&)、或(|)、非(!)、加(+)、减(-)、乘(*)、除(/)、取余(%)等,通过运算符的使用能够实现数字电路中的各种功能。

5. 时钟(Clock):时钟信号在数字设计中起到非常重要的作用,它用来同步数字电路中的各个组件,确保它们按照时序进行正确的操作。

时钟信号通常是周期性的信号,在数字电路中广泛用于触发、同步和控制各个模块的工作。

通过学习Verilog HDL语言的基础知识,可以帮助我们更好地理解数字设计中的原理和技术,进而能够设计和实现各种复杂的数字电路。

掌握Verilog HDL语言的基础概念和语法规则,是每一位数字设计工程师必备的技能之一。

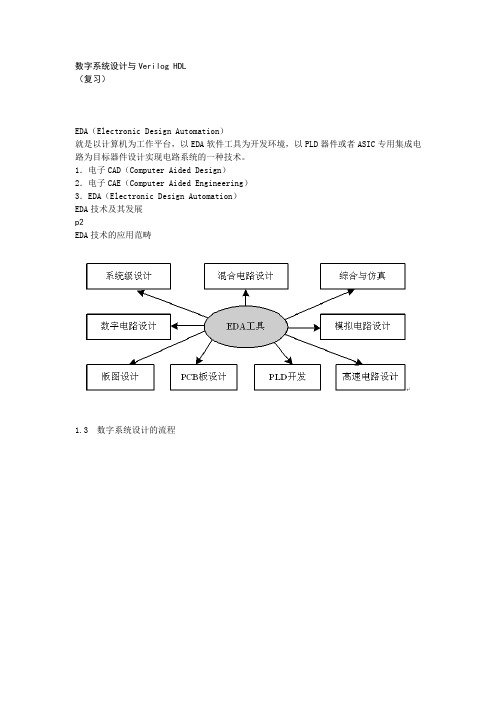

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

数字系统设计与VerilogHDL课程设计一、课程设计背景数字系统设计和VerilogHDL是计算机科学与技术专业中比较重要的课程之一。

在该课程中,学生将学习到数字系统的设计和实现过程,以及VerilogHDL语言的应用和编写。

本课程设计旨在让学生通过实践,巩固并深化所学知识,提高其实际运用能力,并帮助学生更好地理解数字系统设计和VerilogHDL的重要性。

二、课程设计目标与要求1. 课程设计目标本课程设计主要目标是让学生了解数字系统设计和VerilogHDL的工作原理和实现方法,并通过实践进行巩固,提高学生的动手能力,为日后从事该领域的工作做好充分的准备。

2. 课程设计要求本课程设计要求学生能够在充分理解了数字系统设计和VerilogHDL的基本原理和方法后,进行硬件电路图、程序代码的设计和仿真。

同时,学生需要自主完成以下任务:1.学习数字系统设计和VerilogHDL的基本知识。

2.设计并仿真一个简单的多功能数字系统,包括至少一个输入和一个输出设备,以及多个存储器(SRAM、DRAM、ROM等都可以)。

3.使用VerilogHDL语言设计实现一个几位数的计算器。

4.完成个人或小组课程设计报告,包括设计过程中的心得、体会等内容。

三、课程设计流程1. 学习数字系统设计和VerilogHDL的基本知识数字系统设计和VerilogHDL的基本知识包括数字系统的基本概念、数字信号处理、电路设计和VerilogHDL的基本语法和程序设计方法等。

学生可以通过阅读相关教材和参考资料来学习这些知识。

2. 设计多功能数字系统在完成学习后,学生可以开始设计自己的多功能数字系统。

该系统应该包括输入、输出、存储器等组件,并应该考虑到系统的稳定性、处理速度、数据存储和传输等方面的问题。

设计的过程中还需注意电路连接、时序控制、设计优化等方面,确保数字系统的高效功能和性能。

3. 设计计算器在完成多功能数字系统的设计后,学生可以进一步使用VerilogHDL语言,编写程序设计一个几位数的计算器。

数字系统设计与veriloghdl课后答案【篇一:数字逻辑与数字系统设计习题参考答案】>第1章习题解答1.3 (1)86(2)219(3)106.25(4)0.6875 (4)0.1011.4 (1)101111(2)1001000(3)100001l.111.5 (1)(117)10=(165)8=(1110101)2=(75)16(2)(3452)10=(6574)8=(110101111100)2=(d7c)16(3)(23768.6875)10=(56330.54)8=(101110011011000.1011)2=(5cd 8.b)16 (4)(0.625)10=(0.5)8=(0.101)2=(0.a)16 1.6(1)(117)8=(1001111)2=(79)10(2)(7456)8=(111100101110)2=(3886)10(3)(23765.64)8=(10 0111 1111 0101.1101)2=(10229.8125)10(4)(0.746)8=(0.11111)2=(0.96875)10 1.7 (1)(9a)16=(10011010)2=(154)10(2) (3cf6)16=(11110011110110)2=(15606)10(3) (7ffe.6)16=(111111*********.011)2=(32766.375)10 (4)(0.c4)16=(0.110001)2=(0.765625)10 1-8(1)(125)10=(000100100101)8421bcd(2)(7342)10=(0111001101000010)8421bcd(3)(2018.49)10=(0010000000011000.01001001)8421bcd(4)(0.785)10=(0.011110000101)8421bcd1.9(1)(106)10=(1101010)2 原码=反码=补码=01101010 (2)(-98)10=(-1100010)2原码=11100010反码=10011101 补码=11100011(3)(-123)10=(-1111011)2 原码=11111011反码=10000101 补码=11111011(4)(-0.8125)10=(-0.1101)2 原码=1.1101000反码=1.0010111 补码=1.00110001.10(1)(104)10=(1101000)2 [1101000]补=01101000(-97)10=(-1100001)2 [-1100001]补=1001111101101000 + 10011111 0000011110000011 + 01001111 11010010[104-97]补=01101000+10011111=00000111, 104-97=(00000111)2=7 (2) (-125)10=(-1111101)2(79)10=(01001111)2[-1111101]补=10000011 [01001111]补=0100111101111000 [-125+79]补=10000011+01001111=11010010,-125+79=(-0101110)2=-46 (3) (120)10=(1111000)2[01111000]补=01111000(-67)10=(-1000011)2[-1000011]补=10111101[120-67]补=10000011+01001111=00110101,-125+79=(00110101)2=53 (4) (-87)10=(-1010111)2[-1010111]补=10101001(12)10=(1100)2[1100]补=00001100[-87+12]补=10101001+00001100=10110101,-125+79=(-1001011)2=-75+ 10111101 0011010110101001+ 00001100 10110101第2章习题解答2.3 解:根据逻辑图可直接写出逻辑表达式:(a) f=ab?bc;(b)f=abbcac解:设3个输入变量分别为a、b、c,输出为f,按题意,其中有奇数个为1,则输出f=1,因此可写出其逻辑表达式为f=abc?abc?abc?abc。

数字系统设计与verilog_HDL_王金明_第四版__EDA期末知识点复习(宁波工程学院电科版)1、采用硬件描述语言(HDL)进行电路设计的优势。

1)更适合用于描述规模大、功能复杂的数字系统2)语言标准化、便于设计的复用、交流、保存和修改3)设计与工艺的无关性,宽范围的描述能力,便于组织大规模、模块化的设计2、Verilog模块的结构模块声明:包括模块名字、模块输入、输出端口列表,结束关键字为endmodule端口定义:格式为:input: 端口名1,端口名2…端口名n;output: 端口名1,端口名2…端口名n;inout: 端口名1,端口名2…端口名n;3、标识符是用户在编程时给verilog对象起的名字,模块、端口和实例的名字都是标识符。

标识符可以是任意一组字母、数字以及符号“$”和“_”的组合,但标识符的第一个字符必须是字母(a-z,A-Z)或者是下划线“_”,标识符最长可包含1023个字符,此外,标识符区分大小写。

4、整数写法:+/-’1、在较长的数之间可用下划线分开2、当数字不说明位宽时,默认值为32位3、 X或(z)在二进制中代表1位x(或z),在八进制中代表3位,在16进制中代表4位4、如果没有定义一个整数的位宽,其宽度为相应值中定义的位数。

5、如果定义的位宽比实际的位数长,通常在左边填0补位,但如果最左边一位为x或z,就相应的用x或z左边补位。

6、“?”是高阻态z的另一种表示符号,在数字的表示中,字符“?”和z 是完全等价的,可相互代替。

7、整数可以带符号,并且正负号应写在最左边,负数通常表示为二进制补码的形式。

8、当位宽与进制缺省时表示的是10进制数9、在位宽和‘之间,以及进制和数值之间允许出现空格,但’和进制之间以及数值之间是不能出现空格的。

要求掌握整数正确的书写方式。

5、向量:宽度大于1位的变量;标量:宽度为1位的变量。

定义2个8位reg型矢量:reg [7:0] ra, rb;6、运算符(1)注意:逻辑运算符,例如逻辑与&&、逻辑或||、逻辑非!,运算结果是1位的。

《数字系统设计与Verilog HDL》教学大纲课程中文名称: 数字系统设计与Verilog HDL 课程英文名称: Digital system design with Verilog HDL课程代码: 学时/实践或实验/学分:40/8/2.5课程类别: 课程性质: 选修课适用专业:执笔人: 审定人:审批人:一、教学目标教学目标是使学生了解掌握EDA技术的基础知识、可编程逻辑器件的基本结构、硬件描述语言的语法、编程方法以及相关开发软件的使用方法。

重点掌握:PLD器件的结构和开发流程、开发软件的使用方法、Verilog HDL语言的基本语法和利用Verilog HDL语言建模、仿真和综合的设计复杂数字逻辑电路与系统设计的方法和技术。

目标1:了解EDA技术的发展概况,掌握EDA技术的基本概念及相关的基础知识,掌握数字系统设计的设计方法和流程。

了解可编程逻辑器件的分类,掌握可编程逻辑器件的基本结构掌握,掌握CPLD及FPGA器件的基本结构掌握。

目标2:掌握Verilog HDL的语言要素、各种语句以及设计方法等基础知识;掌握Verilog HDL 模块和测试模块的基本结构,能够利用Verilog HDL语言对数字电路进行建模。

目标3:掌握Verilog HDL的三种描述方式;掌握层次设计的方法以及一些设计技巧;并掌握利用有限状态机对数字电路进行建模的方式。

目标4:掌握开发软件及仿真软件的使用流程及方法,能够对设计文件进行仿真验证。

二、课程教学目标与毕业要求关系矩阵注:用☆☆☆、☆☆、☆分别表示教学目标对毕业要求的贡献度为强、中、弱。

三、教学内容和学时分配(32学时)《数字系统设计与Verilog HDL》在理论教学方面侧重于PLD基本原理、Verilog HDL语法要素和行为语句、Verilog HDL阻塞与非阻塞赋值、Verilog HDL有限状态机设计和数字电路设计。

实验教学方面侧重于利用现代 EDA设计流程、软件仿真应用、仿真测试程序设计、层次设计。

数字系统设计与VerilogHDL课后习题习题11.1现代EDA技术的特点有哪些?1.2什么是T op-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。

习题11.1现代EDA技术的特点有哪些?1.2什么是Top-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。

6.5 initial语句与always语句的关键区别是什么?6.6分别用任务和函数描述一个4选1多路选择器。