MEMORY存储芯片ADM232AARWZ-REEL中文规格书

- 格式:pdf

- 大小:300.36 KB

- 文档页数:5

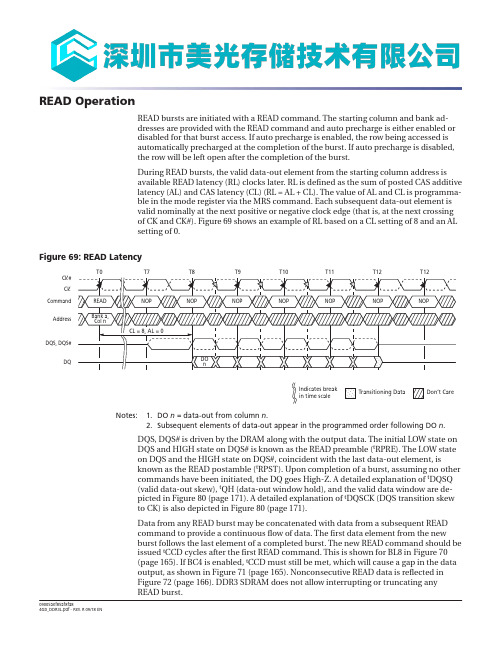

READ OperationREAD bursts are initiated with a READ command. The starting column and bank ad-dresses are provided with the READ command and auto precharge is either enabled or disabled for that burst access. If auto precharge is enabled, the row being accessed is automatically precharged at the completion of the burst. If auto precharge is disabled,the row will be left open after the completion of the burst.During READ bursts, the valid data-out element from the starting column address is available READ latency (RL) clocks later. RL is defined as the sum of posted CAS additive latency (AL) and CAS latency (CL) (RL = AL + CL). The value of AL and CL is programma-ble in the mode register via the MRS command. Each subsequent data-out element is valid nominally at the next positive or negative clock edge (that is, at the next crossing of CK and CK#). Figure 69 shows an example of RL based on a CL setting of 8 and an AL setting of 0.Figure 69: READ LatencyCKCK#CommandAddressDQDQS, DQS#Don’t CareTransitioning Data Indicates break in time scaleNotes:1.DO n = data-out from column n .2.Subsequent elements of data-out appear in the programmed order following DO n .DQS, DQS# is driven by the DRAM along with the output data. The initial LOW state on DQS and HIGH state on DQS# is known as the READ preamble (t RPRE). The LOW state on DQS and the HIGH state on DQS#, coincident with the last data-out element, isknown as the READ postamble (t RPST). Upon completion of a burst, assuming no other commands have been initiated, the DQ goes High-Z. A detailed explanation of t DQSQ (valid data-out skew), t QH (data-out window hold), and the valid data window are de-picted in Figure 80 (page 171). A detailed explanation of t DQSCK (DQS transition skew to CK) is also depicted in Figure 80 (page 171).Data from any READ burst may be concatenated with data from a subsequent READ command to provide a continuous flow of data. The first data element from the new burst follows the last element of a completed burst. The new READ command should be issued t CCD cycles after the first READ command. This is shown for BL8 in Figure 70(page 165). If BC4 is enabled, t CCD must still be met, which will cause a gap in the data output, as shown in Figure 71 (page 165). Nonconsecutive READ data is reflected in Figure 72 (page 166). DDR3 SDRAM does not allow interrupting or truncating any READ burst.Figure 100: Precharge Power-Down (Slow-Exit Mode) Entry and ExitCKCK#CommandCKEEnter power-downmode Exit power-downmodeDon’t CareIndicates break in time scaleNotes:1.Any valid command not requiring a locked DLL.2.Any valid command requiring a locked DLL.Figure 101: Power-Down Entry After READ or READ with Auto Precharge (RDAP)Don’t CareTransitioning Data CKCK#Command DQ BL8DQ BC4DQS, DQS#Address CKEPower-down or self refresh entryIndicates break in time scaleFigure 102: Power-Down Entry After WRITECKCK#Command DQ BL8DQ BC4DQS, DQS#AddressCKEself refresh entry1Don’t CareTransitioning Data Indicates break in time scaleNote:1.CKE can go LOW 2t CK earlier if BC4MRS.Figure 103: Power-Down Entry After WRITE with Auto Precharge (WRAP)Don’t CareTransitioning Data CKCK#CommandDQ BL8DQ BC4DQS, DQS#Address A10CKEPower-down or self refresh entry 2Start internal precharge Indicates break in time scaleNotes:1.t WR is programmed through MR0[11:9] and represents t WRmin (ns)/t CK rounded up tothe next integer t CK.2.CKE can go LOW 2t CK earlier if BC4MRS.Figure 104: REFRESH to Power-Down EntryCKCK#CommandCKET0T1T2T3Ta0Ta1Ta2Tb0Don’t CareIndicates break in time scaleNote:1.After CKE goes HIGH during t RFC, CKE must remain HIGH until t RFC is satisfied.Figure 105: ACTIVATE to Power-Down EntryCKCK#Command Address CKET0T1T2T3T4T5T6T7Figure 108: Power-Down Exit to Refresh to Power-Down EntryCKCK#CKET0T1T2T3T4Ta0Ta1Tb0Command。

Data SheetADuM1410/ADuM1411/ADuM1412FEATURESLow power operation 5 V operation1.3 mA per channel maximum at 0 Mbps to 2 Mbps 4.0 mA per channel maximum at 10 Mbps 3 V operation0.8 mA per channel maximum at 0 Mbps to 2 Mbps 1.8 mA per channel maximum at 10 Mbps Bidirectional communication 3 V/5 V level translationHigh temperature operation: 105°C Up to 10 Mbps data rate (NRZ)Programmable default output stateHigh common-mode transient immunity: >25 kV/µs 16-lead, RoHS compliant, SOIC wide body package Safety and regulatory approvalsUL recognition: 3750 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A VDE certificate of conformityDIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 V IORM = 560 V peakTÜV approval: IEC/EN 60950-1V GND V V V V GND DD22OA OB OC OD2206580-001Figure 1. ADuM1410V GND V V V V CTRL GND DD22OA OB OC ID2206580-002Figure 2. ADuM1411V GND V V V V CTRL GNDDD22OA OB IC ID 2206580-003APPLICATIONSGeneral-purpose multichannel isolation SPI interface/data converter isolation RS-232/RS-422/RS-485 transceivers Industrial field bus isolationGENERAL DESCRIPTIONThe ADuM1410/ADuM1411/ADuM14121 are four-channel digital isolators based on Analog Devices, Inc., i Coupler® technology. Combining high speed CMOS and monolithic air core transformer technologies, these isolation components provide outstanding performance characteristics superior to alternatives such as optocoupler devices.By avoiding the use of LEDs and photodiodes, i Coupler devices remove the design difficulties commonly associated with opto-couplers. The usual concerns that arise with optocouplers, such as uncertain current transfer ratios, nonlinear transfer functions, and temperature and lifetime effects, are eliminated with the simple i Coupler digital interfaces and stable performance characteristics. The need for external drivers and other discrete components is eliminated with these i Coupler products. Furthermore, i Coupler1Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329.Figure 3. ADuM1412devices consume one-tenth to one-sixth the power of optocou-plers at comparable signal data rates.The ADuM1410/ADuM1411/ADuM1412 isolators provide four independent isolation channels in a variety of channel configu-rations and data rates (see the Ordering Guide) up to 10 Mbps. All models operate with the supply voltage on either side ranging from 2.7 V to 5.5 V , providing compatibility with lower voltage systems as well as enabling voltage translation functionality across the isolation barrier. All products also have a default output control pin. This allows the user to define the logic state the outputs are to adopt in the absence of the input power. Unlike other optocoupler alternatives, the ADuM1410/ADuM1411/ ADuM1412 isolators have a patented refresh feature that ensures dc correctness in the absence of input logic transitions and during power-up/power-down conditions.Data Sheet ADuM1410/ADuM1411/ADuM1412 SPECIFICATIONSELECTRICAL CHARACTERISTICS—5 V OPERATION4.5 V ≤ V DD1 ≤5.5 V, 4.5 V ≤ V DD2 ≤ 5.5 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 5 V. All voltages are relative to their respective ground. Table 1.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.50 0.73 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.38 0.53 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.4 3.2 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.2 1.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10)8.8 12 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.8 4.0 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.2 2.8 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.8 2.4 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 5.4 7.6 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 3.8 5.3 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2(Q)2.0 2.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 4.6 6.5 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC,I ID, I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 2.0 V Logic Low Input Threshold V IL 0.8 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 5.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 4.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet Parameter Symbol Min Typ Max Unit Test Conditions/Comments SWITCHING SPECIFICATIONSADuM1410ARWZ/ADuM1411ARWZ/ADuM1412ARWZMinimum Pulse Width2PW 1000 ns C L = 15 pF, CMOS signal levels Maximum Data Rate3 1 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 65 100 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 40 ns C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK50 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching6t PSKCD/OD50 ns C L = 15 pF, CMOS signal levels ADuM1410BRWZ/ADuM1411BRWZ/ADuM1412BRWZMinimum Pulse Width2PW 100 ns C L = 15 pF, CMOS signal levels Maximum Data Rate310 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 30 50 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 5 ns C L = 15 pF, CMOS signal levels Change vs. Temperature 5 ps/°C C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK30 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching,Codirectional Channels6t PSKCD 5 ns C L = 15 pF, CMOS signal levelsChannel-to-Channel Matching,Opposing-Directional Channels6t PSKOD 6 ns C L = 15 pF, CMOS signal levelsAll ModelsOutput Rise/Fall Time (10% to 90%) t R/t F 2.5 ns C L = 15 pF, CMOS signal levelsCommon-Mode Transient Immunity at Logic High Output7|CM H| 25 35 kV/µs V Ix = V DD1 or V DD2, V CM = 1000 V,transient magnitude = 800 VCommon-Mode Transient Immunity at Logic Low Output7 |CM L| 25 35 kV/µs V Ix = 0 V, V CM = 1000 V,transient magnitude = 800 VRefresh Rate f r 1.2 MbpsInput Enable Time8t ENABLE 2.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1 Input Disable Time8t DISABLE 5.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1Input Dynamic Supply Current per Channel9I DDI (D)0.12 mA/MbpsOutput Dynamic Supply Current per Channel9I DDO (D)0.04 mA/Mbps1 The supply current values for all four channels are combined when running at identical data rates. Output supply current values are specified with no output load present. The supply current associated with an individual channel operating at a given data rate can be calculated as described in the Power Consumption section. See Figure 8 through Figure 10 for information on per-channel supply current as a function of data rate for unloaded and loaded conditions. See Figure 11 through Figure 15 for total V DD1 and V DD2 supply currents as a function of data rate for ADuM1410/ADuM1411/ADuM1412 channel configurations.2 The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.3 The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.4 t PHL propagation delay is measured from the 50% level of the falling edge of the V Ix signal to the 50% level of the falling edge of the V Ox signal. t PLH propagation delay is measured from the 50% level of the rising edge of the V Ix signal to the 50% level of the rising edge of the V Ox signal.5 t PSK is the magnitude of the worst-case difference in t PHL or t PLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.6 Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing-directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.7 |CM H| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O > 0.8 V DD2. |CM L| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O < 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.8 Input enable time is the duration from when V DISABLE is set low until the output states are guaranteed to match the input states in the absence of any input data logic transitions. If an input data logic transition within a given channel does occur within this time interval, the output of that channel reaches the correct state within the much shorter duration as determined by the propagation delay specifications within this data sheet. Input disable time is the duration from when V DISABLE is set high until the output states are guaranteed to reach their programmed output levels, as determined by the CTRL2 logic state (see Table 14).9 Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in signal data rate. See Figure 8 through Figure 10 for information on per-channel supply current for unloaded and loaded conditions. See the Power Consumption section for guidance on calculating the per-channel supply current for a given data rate.Rev. M | Page of 22Data Sheet ADuM1410/ADuM1411/ADuM1412ELECTRICAL CHARACTERISTICS—3 V OPERATION2.7 V ≤ V DD1 ≤3.6 V, 2.7 V ≤ V DD2 ≤ 3.6 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 3.0 V. All voltages are relative to their respective ground. Table 2.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.25 0.38 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.19 0.33 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.2 1.6 mA DC to 1 MHz logic signalfrequency V DD2 Supply Current I DD2 (Q)0.8 1.0 mA DC to 1 MHz logic signalfrequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 4.5 6.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 1.4 1.8 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.0 1.9 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q)0.9 1.7 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 3.1 4.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.1 3.0 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2 (Q) 1.0 1.8 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 2.6 3.8 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC, I ID,I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 1.6 V Logic Low Input Threshold V IL 0.4 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 3.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 2.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet。

6.5Write ProtectionApplications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern, the W25Q32JV provides several means to protect the data from inadvertent writes.Write Protect Features∙Device resets when VCC is below threshold∙Time delay write disable after Power-up∙Write enable/disable instructions and automatic write disable after erase or program∙Software and Hardware (/WP pin) write protection using Status Registers∙Additional Individual Block/Sector Locks for array protection∙Write Protection using Power-down instruction∙Lock Down write protection for Status Register until the next power-up∙One Time Program (OTP) write protection for array and Security Registers using Status Register* *Note:This feature is available upon special order. Please contact Winbond for details.Upon power-up or at power-down, the W25Q32JV will maintain a reset condition while VCC is below the threshold value of V WI, (See Power-up Timing and Voltage Levels and Figure 43). While reset, all operations are disabled and no instructions are recognized. During power-up and after the VCC voltage exceeds V WI, all program and erase related instructions are further disabled for a time delay of t PUW. This includes the Write Enable, Page Program, Sector Erase, Block Erase, Chip Erase and the Write Status Register instructions. Note that the chip select pin (/CS) must track the VCC supply level at power-up until the VCC-min level and t VSL time delay is reached, and it must also track the VCC supply level at power-down to prevent adverse command sequence. If needed a pull-up resister on /CS can be used to accomplish this.After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Page Program, Sector Erase, Block Erase, Chip Erase or Write Status Register instruction will be accepted. After completing a program, erase or write instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (SRP, SRL) and Block Protect (CMP, TB, BP[2:0]) bits. These settings allow a portion or the entire memory array to be configured as read only. Used in conjunction with the Write Protect (/WP) pin, changes to the Status Register can be enabled or disabled under hardware control. See Status Register section for further information. Additionally, the Power-down instruction offers an extra level of write protection as all instructions are ignored except for the Release Power-down instruction.The W25Q32JV also provides another Write Protect method using the Individual Block Locks. Each 64KB block (except the top and bottom blocks, total of 62 blocks) and each 4KB sector within the top/bottom blocks (total of 32 sectors) are equipped with an Individual Block Lock bit. When the lock bit is 0, the corresponding sector or block can be erased or programmed; when the lock bit is set to 1, Erase or Program commands issued to the corresponding sector or block will be ignored. When the device is powered on, all Individual Block Lock bits will be 1, so the entire memory array is protected from Erase/Program. An “Individual Block Unlock (39h)” instruction must be issued to unlock any specific sector or block.The WPS bit in Status Register-3 is used to decide which Write Protect scheme should be used. When WPS=0 (factory default), the device will only utilize CMP, SEC, TB, BP[2:0] bits to protect specific areas of the array; when WPS=1, the device will utilize the Individual Block Locks for write protection.Figure 4c. Status Register-3Write Protect Selection (WPS) –Volatile/Non-Volatile WritableThe WPS bit is used to select which Write Protect scheme should be used. When WPS=0, the device will use the combination of CMP, SEC, TB, BP[2:0] bits to protect a specific area of the memory array. When WPS=1, the device will utilize the Individual Block Locks to protect any individual sector or blocks. Thedefault value for all Individual Block Lock bits is 1 upon device power on or after reset.Output Driver Strength (DRV1, DRV0) –Volatile/Non-Volatile WritableThe DRV1 & DRV0 bits are used to determine the output driver strength for the Read operations.Reserved Bits –Non FunctionalThere are a few reserved Status Register bits that may be read out as a “0” or “1”. It is recommended to ignore the values of those bits. During a “Write Status Register” instruction, the Reserved Bits can be written as “0”, but there will not be any effects.Status Register Memory Protection (WPS = 0, CMP = 0)Notes:1.X = don’t care2.L = Lower; U = Upper3.If any Erase or Program command specifies a memory region that contains protected data portion, this commandwill be ignored.Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h)The Write Status Register instruction allows the Status Registers to be written. The writable Status Register bits include: SEC, TB, BP[2:0] in Status Register-1; CMP, LB[3:1], QE, SRL in Status Register-2; DRV1, DRV0, WPS in Status Register-3. All other Status Register bit locations are read-only and will not be affected by the Write Status Register instruction. LB[3:1] are non-volatile OTP bits, once it is set to 1, it cannot be cleared to 0.To write non-volatile Status Register bits, a standard Write Enable (06h) instruction must previously have been executed for the device to accept the Write Status Register instruction (Status Register bit WEL must equal 1). Once write enabled, the instruction is entered by driving /CS low, sending the instruction code “01h/31h/11h”, and then writing the status register data byte as illustrated in Figure 9a.To write volatile Status Register bits, a Write Enable for Volatile Status Register (50h) instruction must have been executed prior to the Write Status Register instruction (Status Register bit WEL remains 0). However, SRL and LB[3:1] cannot be changed from “1” to “0” because of the OTP protection for these bits. Upon power off or the execution of a Software/Hardware Reset, the volatile Status Register bit values will be lost, and the non-volatile Status Register bit values will be restored.During non-volatile Status Register write operation (06h combined with 01h/31h/11h), after /CS is driven high, the self-timed Write Status Register cycle will commence for a time duration of t W(See AC Characteristics). While the Write Status Register cycle is in progress, the Read Status Register instruction may still be accessed to check the status of the BUSY bit. The BUSY bit is a 1 during the Write Status Register cycle and a 0 when the cycle is finished and ready to accept other instructions again. After the Write Status Register cycle has finished, the Write Enable Latch (WEL) bit in the Status Register will be cleared to 0.During volatile Status Register write operation (50h combined with 01h/31h/11h), after /CS is driven high, the Status Register bits will be refreshed to the new values within the time period of t SHSL2(See AC Characteristics). BUSY bit will remain 0 during the Status Register bit refresh period.Refer to section 7.1 for Status Register descriptions.Figure 9a. Write Status Register-1/2/3 Instruction。

ADM485FUNCTIONAL BLOCK DIAGRAMCC 00078-001FEATURESMeets EIA RS-485 standard 5 Mbps data rateSingle 5 V supply–7 V to +12 V bus common-mode range High speed, low power BiCMOS Thermal shutdown protection Short-circuit protectionDriver propagation delay: 10 ns typical Receiver propagation delay: 15 ns typical High-Z outputs with power off Superior upgrade for LTC485APPLICATIONSLow power RS-485 systems DTE/DCE interface Packet switchingLocal area networks (LNAs) Data concentration Data multiplexersIntegrated services digital network (ISDN)GENERAL DESCRIPTIONThe ADM485 is a differential line transceiver suitable for high speed bidirectional data communication on multipoint bus transmission lines. It is designed for balanced data transmission and complies with EIA standards RS-485 and RS-422. The part contains a differential line driver and a differential line receiver. Both the driver and the receiver can be enabled independently. When disabled, the outputs are three-stated.The ADM485 operates from a single 5 V power supply. Excessive power dissipation caused by bus contention or by output shorting is prevented by a thermal shutdown circuit. If during fault conditions, a significant temperature increase is detected in the internal driver circuitry, this feature forces the driver output into a high impedance state.Up to 32 transceivers can be connected simultaneously on a bus, but only one driver should be enabled at any time. It is important, therefore, that the remaining disabled drivers do not load the bus. To ensure this, the ADM485 driver features high output impedance when disabled and when powered down, which minimizes the loading effect when the transceiver is not being used. The high impedance driver output is maintained over the common-mode voltage range of −7 V to +12 V .Figure 1.The receiver contains a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating). The ADM485 is fabricated on BiCMOS, an advanced mixed technology process combining low power CMOS with fast switching bipolar technology. All inputs and outputs contain protection against ESD; all driver outputs feature high source and sink current capability. An epitaxial layer is used to guard against latch-up.The ADM485 features extremely fast switching speeds. Minimal driver propagation delays permit transmission at data rates up to 5 Mbps while low skew minimizes EMI interference. The part is fully specified over the commercial and industrial temperature range and is available in 8-lead PDIP , 8-lead SOIC, and small footprint, 8-lead MSOP packages.ADM485Rev. F | Page 2 of 16ADM485SPECIFICATIONSV CC = 5 V ± 5%, all specifications T MIN to T MAX, unless otherwise noted.Rev. F | Page 3 of 16ADM485TIMING SPECIFICATIONSV CC = 5 V ± 5%, all specifications T MIN to T MAX, unless otherwise noted.1 Guaranteed by characterization.Rev. F | Page 4 of 16ADM485Rev. F | Page 5 of 16ABSOLUTE MAXIMUM RATINGST A = 25°C, unless otherwise noted.Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Table 4. TransmittingInputsOutputsDE DIB A 1 1 0 1 1 0 1 0 0X 1Z 2Z 21 X = don’t care.2Z = high impedance.1 X = don’t care.2Z = high impedance.ESD CAUTION。

__________________________________________Typical Operating Characteristics(V CC = +3.3V, 235kbps data rate, 0.1µF capacitors, all transmitters loaded with 3k Ω, T A = +25°C, unless otherwise noted.)TIMING CHARACTERISTICS—MAX3237(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Note 2:MAX3222/MAX3232/MAX3241: C1–C4 = 0.1µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.MAX3237: C1–C4 = 0.1µF tested at 3.3V ±5%; C1–C4 = 0.22µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.Note 3:Transmitter input hysteresis is typically 250mV.-6-5-4-3-2-101234560MAX3222/MAX3232TRANSMITTER OUTPUT VOLTAGEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )20003000100040005000246810121416182022150MAX3222/MAX3232SLEW RATEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E (V /μs )20003000100040005000510152025303540MAX3222/MAX3232SUPPLY CURRENT vs. LOAD CAPACITANCEWHEN TRANSMITTING DATALOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )20003000100040005000MAX3222/MAX3232/MAX3237/MAX32413.0V to 5.5V, Low-Power, up to 1Mbps, True RS-232 Transceivers Using Four 0.1µF External CapacitorsFigure 4a. MAX3241 Transmitter Output Voltage vs. Load Current per Transmitter3.0V to 5.5V , Low-Power, up to 1Mbps, True RS-232Transceivers Using Four 0.1µF External CapacitorsMAX3222/MAX3232/MAX3237/MAX3241CC = 3.3V5μs/divFigure 5. Loopback Test CircuitHigh Data RatesThe MAX3222/MAX3232/MAX3241 maintain the RS-232±5.0V minimum transmitter output voltage even at high data rates. Figure 5 shows a transmitter loopb ack test circuit. Figure 6 shows a loopb ack test result at 120kbps, and Figure 7 shows the same test at 235kbps. For Figure 6, all transmitters were driven simultaneously at 120kb ps into RS-232 loads in parallel with 1000pF. For Figure 7, a single transmitter was driven at 235kbps, and all transmitters were loaded with an RS-232 receiver in parallel with 1000pF.The MAX3237 maintains the RS-232 ±5.0V minimum transmitter output voltage at data rates up to 1Mb ps. Figure 8 shows a loopb ack test result at 1Mb ps with MBAUD = V CC . For Figure 8, all transmitters were loaded with an RS-232 receiver in parallel with 250pF.fdzfdfbbFigure 6. MAX3241 Loopback Test Result at 120kbpsCC = 3.3V2μs/divFigure 7. MAX3241 Loopback Test Result at 235kbps0V +5V 0V -5V +5V 0VT_INT_OUT = R_IN 5k R_OUT 150pF200ns/divCC = 3.3VFigure 8. MAX3237 Loopback Test Result at 1000kbps (MBAUD = V CC )___________________Chip Topography___________________Chip InformationT1INT2IN 0.087"(2.209mm)R2OUTR2IN T2OUT R1OUTR1INT1OUTV CCV+C1+ENC1-C2+C2-V-GNDTRANSISTOR COUNT: 339SUBSTRATE CONNECTED TO GNDMAX3222/MAX3232/MAX3237/MAX3241 3.0V to 5.5V, Low-Power, up to 1Mbps, True RS-232Transceivers Using Four 0.1µF External Capacitors。

ADG3304Data Sheet Rev. E | Page 16 of 21TERMINOLOGYV IHALogic input high voltage at Pin A1 to Pin A4. V ILALogic input low voltage at Pin A1 to Pin A4. V OHA Logic output high voltage at Pin A1 to Pin A4. V OLA Logic output low voltage at Pin A1 to Pin A4. C A Capacitance measured at Pin A1 to Pin A4 (EN = 0). I LA, Hi-ZLeakage current at Pin A1 to Pin A4 when EN = 0 (high impedance state at Pin A1 to Pin A4).V IHYLogic input high voltage at Pin Y1 to Pin Y4. V ILYLogic input low voltage at Pin Y1 to Pin Y4. V OHY Logic output high voltage at Pin Y1 to Pin Y4. V OLY Logic output low voltage at Pin Y1 to Pin Y4. C Y Capacitance measured at Pin Y1 to Pin Y4 (EN = 0). I LY , Hi-ZLeakage current at Pin Y1 to Pin Y4 when EN = 0 (high impedance state at Pin Y1 to Pin Y4).V IHENLogic input high voltage at the EN pin.V ILENLogic input low voltage at the EN pin.C ENCapacitance measured at EN pin.I LENEnable (EN) pin leakage current.t ENThree-state enable time for Pin A1 to Pin A4 and Pin Y1 to Pin Y4.t P , A→YPropagation delay when translating logic levels in the A→Y direction.t R, A→YRise time when translating logic levels in the A→Y direction. T F, A→Y Fall time when translating logic levels in the A→Y direction. D MAX, A→Y Guaranteed data rate when translating logic levels in the A→Y direction under the driving and loading conditions specified in Table 1. T S KEW , A→Y Difference between propagation delays on any two channels when translating logic levels in the A→Y direction. t PPSKEW , A→Y Difference in propagation delay between any one channel and the same channel on a different part (under same driving/ loading conditions) when translating in the A→Y direction. t P , Y→A Propagation delay when translating logic levels in the Y→A direction. t R, Y→A Rise time when translating logic levels in the Y→A direction. t F, Y→A Fall time when translating logic levels in the Y→A direction. D MAX, Y→A Guaranteed data rate when translating logic levels in the Y→A direction under the driving and loading conditions specified in Table 1. t S KEW , Y→A Difference between propagation delays on any two channels when translating logic levels in the Y→A direction. t PPSKEW , Y→A Difference in propagation delay between any one channel and the same channel on a different part (under the same driving/ loading conditions) when translating in the Y→A direction. V CCA V CCA supply voltage. V CCY V CCY supply voltage. I CCA V CCA supply current. I CCY V CCY supply current. I Hi-Z, A V CCA supply current during three-state mode (EN = 0). I Hi-Z, Y V CCY supply current during three-state mode (EN = 0).Data SheetADG3304 Rev. E | Page 17 of 21THEORY OF OPERATIONThe ADG3304 level translator allows the level shifting necessary for data transfer in a system where multiple supply voltages are used. The device requires two supplies, V CCA and V CCY (V CCA ≤ V CCY ). These supplies set the logic levels on each side of the device. When driving the A pins, the device translates the V CCA -compatible logic levels to V CCY -compatible logic levels available at the Y pins. Similarly, because the device is capable of bidirectional translation, when driving the Y pins, the V CCY -compatible logic levels are translated to V CCA -compatible logic levels available at the A pins. When EN = 0, Pin A1 to Pin A4 and Pin Y1 to Pin Y4 are three-stated. When EN is driven high, the ADG3304 goes into normal operation mode and performs level translation. LEVEL TRANSLATOR ARCHITECTURE The ADG3304 consists of four bidirectional channels. Each channel can translate logic levels in either the A→Y or the Y→A direction. It uses a one-shot accelerator architecture, which ensures excellent switching characteristics. Figure 39 shows a simplified block diagram of a bidirectional channel.Y 04860-053Figure 39. Simplified Block Diagram of an ADG3304 Channel The logic level translation in the A→Y direction is performed using a level translator (U1) and an inverter (U2), while the translation in the Y→A direction is performed using Inverter U3 and Inverter U4. The one-shot generator detects a rising or falling edge present on either the A side or the Y side of the channel. It sends a short pulse that turns on the PMOS transistors (T1 to T2) for a rising edge, or the NMOS transistors (T3 to T4) for a falling edge. This charges/discharges the capacitive load faster, which results in faster rise and fall times.The inputs of the unused channels (A or Y) should be tied to their corresponding V CC rail (V CCA or V CCY ) or to GND. INPUT DRIVING REQUIREMENTS To ensure correct operation of the ADG3304, the circuit that drives the input of the ADG3304 channels should have an output impedance of less than or equal to 150 Ω and a minimum peak current driving capability of 36 mA. OUTPUT LOAD REQUIREMENTS The ADG3304 level translator is designed to drive CMOS-compatible loads. If current-driving capability is required, it is recommended to use buffers between the ADG3304 outputs and the load. ENABLE OPERATIONThe ADG3304 provides three-state operation at the A and Y I/O pins by using the enable pin (EN), as shown in Table 5. Table 5. Truth TableENY I/O Pins A I/O Pins 0Hi-Z 1 Hi-Z 1 1Normal operation 2Normal operation 21High impedance state.2 In normal operation, the ADG3304 performs level translation.While EN = 0, the ADG3304 enters into three-state mode. In this mode, the current consumption from both the V CCA and V CCY supplies is reduced, allowing the user to save power, which is critical, especially on battery-operated systems. The EN input pin can be driven with either V CCA -compatible or V CCY -compatible logic levels.POWER SUPPLIESFor proper operation of the ADG3304, the voltage applied to the V CCA must be less than or equal to the voltage applied to V CCY . To meet this condition, the recommended power-up sequence is V CCY first and then V CCA . The ADG3304 operates properly only after both supply voltages reach their nominal values. It is not recommended to use the part in a system where, during power-up, V CCA can be greater than V CCY due to a significant increase in the current taken from the V CCA supply. For optimum performance, the V CCA pin and V CCY pin should be decoupled to GND as close as possible to the device.。

Integrated | 10Shutdown and Enable Control (MAX205E/MAX206E/MAX211E/MAX213E/MAX241E)In shutdown mode, the charge pumps are turned off,V+ is pulled down to V CC , V- is pulled to ground, and the transmitter outputs are disabled. This reduces sup-ply current typically to 1µA (15µA for the MAX213E).The time required to exit shutdown is under 1ms, asshown in Figure 5.Receivers All MAX213E receivers, except R4 and R5, are put into a high-impedance state in shutdown mode (see Tables 1a and 1b). The MAX213E’s R4 and R5 receivers still function in shutdown mode. These two awake-in-shut-down receivers can monitor external activity while main-taining minimal power consumption.The enable control is used to put the receiver outputs into a high-impedance state, to allow wire-OR connection of two EIA/TIA-232E ports (or ports of different types) at the UART. It has no effect on the RS-232 drivers or the charge pumps.Note: The enable c ontrol pin is ac tive low for the MAX211E/MAX241E (EN ), but is ac tive high for theMAX213E (EN). The shutdown control pin is active highFigure 4. Charge-Pump DiagramWhen in low-power shutdown mode, the MAX205E/MAX206E/MAX211E/MAX213E/MAX241E driver outputsare turned off and draw only leakage currents—even ifthey are back-driven with voltages between 0V and12V. Below -0.5V in shutdown, the transmitter output isdiode-clamped to ground with a 1k Ω series imped-ance.RS-232 ReceiversThe receivers convert the RS-232 signals to CMOS-logicoutput levels. The guaranteed 0.8V and 2.4V receiverinput thresholds are significantly tighter than the ±3Vthresholds required by the EIA/TIA-232E specification.This allows the receiver inputs to respond to TTL/CMOS-logic levels, as well as RS-232 levels.The guaranteed 0.8V input low threshold ensures thatreceivers shorted to ground have a logic 1 output. The5k Ω input resistance to ground ensures that a receiverwith its input left open will also have a logic 1 output.Receiver inputs have approximately 0.5V hysteresis.This provides clean output transitions, even with slowrise/fall-time signals with moderate amounts of noiseand ringing.In shutdown, the MAX213E’s R4 and R5 receivers haveno hysteresis.找MEMORY 、二三极管上美光存储Integrated | 13MAX202E–MAX213E,MAX232E/MAX241E ±15kV ESD-Protected, 5V RS-232 Transceivers outputs. Therefore,after PC board assembly,theMachine Model is less relevant to I/O ports.Applications InformationCapacitor SelectionThe capacitor type used for C1–C4 is not critical forproper operation. The MAX202E, MAX206–MAX208E,MAX211E, and MAX213E require 0.1µF capacitors,and the MAX232E and MAX241E require 1µF capaci-tors, although in all cases capacitors up to 10µF canbe used without harm. Ceramic, aluminum-electrolytic,or tantalum capacitors are suggested for the 1µFcapacitors, and ceramic dielectrics are suggested forthe 0.1µF capacitors. When using the minimum recom-mended capacitor values, make sure the capacitancevalue does not degrade excessively as the operatingtemperature varies. If in doubt, use capacitors with alarger (e.g., 2x) nominal value. The capacitors’ effec-tive series resistance (ESR), which usually rises at lowtemperatures, influences the amount of ripple on V+and V-.Use larger capacitors (up to 10µF) to reduce the outputimpedance at V+ and V-. This can be useful when“stealing” power from V+ or from V-. The MAX203E andMAX205E have internal charge-pump capacitors.Bypass V CC to ground with at least 0.1µF. In applica-tions sensitive to power-supply noise generated by the charge pumps, decouple V CC to ground with a capaci-tor the same size as (or larger than) the charge-pump capacitors (C1–C4).V+ and V- as Power Supplies A small amount of power can be drawn from V+ and V-,although this will reduce both driver output swing and noise margins. Increasing the value of the charge-pump capacitors (up to 10µF ) helps maintain performance when power is drawn from V+ or V-.Driving Multiple Receivers Each transmitter is designed to drive a single receiver.Transmitters can be paralleled to drive multiple receivers.Driver Outputs when Exiting Shutdown The driver outputs display no ringing or undesirable transients as they come out of shutdown.High Data Rates These transceivers maintain the RS-232 ±5.0V mini-mum driver output voltages at data rates of over 120kbps. F or data rates above 120kbps, refer to the Transmitter Output Voltage vs. Load Capacitance graphs in the Typical Operating Characteristics .Communication at these high rates is easier if the capacitive loads on the transmitters are small; i.e.,short cables are best.Table 2. Summary of EIA/TIA-232E, V.28 Specifications PARAMETERCONDITIONS EIA/TIA-232E, V.28 SPECIFICA-TIONS 0 Level3k Ωto 7k Ωload +5V to +15V Data Rate 3k Ω≤R L ≤7k Ω, C L ≤2500pFUp to 20kbps +3V to +15V Instantaneous Slew Rate, Max 3k Ω≤R L ≤7k Ω, C L ≤2500pF 30V/µsDriver Output Short-Circuit Current, Max 100mATransition Rate on Driver Output V.281ms or 3% of the period Driver Output Resistance-2V < V OUT < +2V 300ΩEIA/TIA-232E4% of the period Driver Output Level, Max No load±25V Driver Output Voltage 3k Ωto 7k Ωload-5V to -15V 0 Level1 Level 1 Level Receiver Input Level ±25VReceiver Input Voltage -3V to -15V。

Table 54: Electrical Characteristics and AC Operating Conditions (Continued)Notes: 1.AC timing parameters are valid from specified T C MIN to T C MAX values.2.All voltages are referenced to V SS.3.Output timings are only valid for R ON34 output buffer selection.4.The unit t CK (AVG) represents the actual t CK (AVG) of the input clock under operation.The unit CK represents one clock cycle of the input clock, counting the actual clockedges.5.AC timing and I DD tests may use a V IL-to-V IH swing of up to 900mV in the test environ-ment, but input timing is still referenced to V REF (except t IS, t IH, t DS, and t DH use theAC/DC trip points and CK, CK# and DQS, DQS# use their crossing points). The minimumslew rate for the input signals used to test the device is 1 V/ns for single-ended inputsand 2 V/ns for differential inputs in the range between V IL(AC) and V IH(AC).6.All timings that use time-based values (ns, μs, ms) should use t CK (AVG) to determine thecorrect number of clocks (Table 54 (page 72) uses CK or t CK [AVG] interchangeably). Inthe case of noninteger results, all minimum limits are to be rounded up to the nearestwhole integer, and all maximum limits are to be rounded down to the nearest wholeinteger.7.Strobe or DQS diff refers to the DQS and DQS# differential crossing point when DQS isthe rising edge. Clock or CK refers to the CK and CK# differential crossing point whenCK is the rising edge.8.This output load is used for all AC timing (except ODT reference timing) and slew rates.The actual test load may be different. The output signal voltage reference point isV DDQ/2 for single-ended signals and the crossing point for differential signals (see Fig-ure 26 (page 64)).9.When operating in DLL disable mode, Micron does not warrant compliance with normalmode timings or functionality.Table 55: Electrical Characteristics and AC Operating Conditions for Speed ExtensionsTable 55: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)Table 55: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)Table 55: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)。

203TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.29Programmable Real-Time Unit Subsystem (PRUSS)The Programmable Real-Time Unit Subsystem (PRUSS)consists of•Two Programmable Real-Time Units (PRU0and PRU1)and their associated memories•An Interrupt Controller (INTC)for handling system interrupt events.The INTC also supports posting events back to the device level host CPU.•A Switched Central Resource (SCR)for connecting the various internal and external masters to the resources inside the PRUSS.The two PRUs can operate completely independently or in coordination with each other.The PRUs can also work in coordination with the device level host CPU.This is determined by the nature of the program which is loaded into the PRUs instruction memory.Several different signaling mechanisms are available between the two PRUs and the device level host CPU.The PRUs are optimized for performing embedded tasks that require manipulation of packed memory mapped data structures,handling of system events that have tight realtime constraints and interfacing with systems external to the device.The PRUSS comprises various distinct addressable regions.Externally the subsystem presents a single 64Kbyte range of addresses.The internal interconnect bus (also called switched central resource,or SCR)of the PRUSS decodes accesses for each of the individual regions.The PRUSS memory map is documented in Table 6-105and in Table 6-106.Note that these two memory maps are implemented inside the PRUSS and are local to the components of the PRUSS.Table 6-105.Programmable Real-Time Unit Subsystem (PRUSS)Local Instruction Space Memory MapBYTE ADDRESSPRU0PRU10x00000000-0x00000FFF PRU0Instruction RAM PRU1Instruction RAM(1)Note that PRU0accesses Data RAM 0at address 0x00000000,also PRU1accesses Data RAM 1at address 0x00000000.Data RAM0is intended to be the primary data memory for PRU0and Data RAM1is intended to be the primary data memory for PRU1.However for passing information between PRUs,each PRU can access the data ram of the ‘other’PRU through address 0x00002000.Table 6-106.Programmable Real-Time Unit Subsystem (PRUSS)Local Data Space Memory MapBYTE ADDRESSPRU0PRU10x00000000-0x000001FFData RAM 0(1)Data RAM 1(1)0x00000200-0x00001FFFReserved Reserved 0x00002000-0x000021FFData RAM 1(1)Data RAM 0(1)0x00002200-0x00003FFFReserved Reserved 0x00004000-0x00006FFFINTC Registers INTC Registers 0x00007000-0x000073FFPRU0Control Registers PRU0Control Registers 0x00007400-0x000077FFReserved Reserved 0x00007800-0x00007BFFPRU1Control Registers PRU1Control Registers 0x00007C00-0xFFFF FFFFReserved Reserved The global view of the PRUSS internal memories and control ports is documented in Table 6-107.The offset addresses of each region are implemented inside the PRUSS but the global device memory mapping places the PRUSS slave port in the address range 0x01C30000-0x01C3FFFF.The PRU0and PRU1can use either the local or global addresses to access their internal memories,but using the local addresses will provide access time several cycles faster than using the global addresses.This is because when accessing via the global address the access needs to be routed through the switch fabric outside PRUSS and back in through the PRUSS slave port.AlarmInterruptsPeriodicInterrupts XTAL 211TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.32Real Time Clock (RTC)The RTC provides a time reference to an application running on the device.The current date and time is tracked in a set of counter registers that update once per second.The time can be represented in 12-hour or 24-hour mode.The calendar and time registers are buffered during reads and writes so that updates do not interfere with the accuracy of the time and date.Alarms are available to interrupt the CPU at a particular time,or at periodic time intervals,such as once per minute or once per day.In addition,the RTC can interrupt the CPU every time the calendar and time registers are updated,or at programmable periodic intervals.The real-time clock (RTC)provides the following features:•100-year calendar (xx00to xx99)•Counts seconds,minutes,hours,day of the week,date,month,and year with leap year compensation •Binary-coded-decimal (BCD)representation of time,calendar,and alarm•12-hour clock mode (with AM and PM)or 24-hour clock mode•Alarm interrupt•Periodic interrupt•Single interrupt to the CPU•Supports external 32.768-kHz crystal or external clock source of the same frequency•Separate isolated power supplyFigure 6-73shows a block diagram of the RTC.Figure 6-73.Real-Time Clock Block Diagram。

DOUTRIN250 kb/s IEC61000-4-2An IMPORTANT NOTICE at the end of this data sheet addresses availability,warranty,changes,use in safety-critical applications, intellectual property matters and other important disclaimers.PRODUCTION DATA.1Features•Meets or Exceeds TIA/RS-232-F and ITURecommendation V.28•ESD Protection for RS-232Bus Pins–±15-kV Human-Body Model(HBM)–±8-kV IEC61000-4-2,Contact Discharge–±15-kV IEC61000-4-2,Air-Gap Discharge•Operates From a Single5-V Power Supply With1-µF Charge-Pump Capacitors•Operates up to250kbit/s•Two Drivers and Two Receivers•Low Supply Current:8mA Typical2Applications•TIA/RS-232-F•Battery-Powered Systems•Terminals•Modems•Computers3DescriptionThe MAX232E is a dual driver and receiver thatincludes a capacitive voltage generator to supply RS-232-F compliant voltage levels from a single5-Vsupply.Each receiver converts RS-232inputs to5-VTTL/CMOS levels.This receiver has a typicalthreshold of1.3V,a typical hysteresis of0.5V,andcan accept±30-V inputs.Each driver convertsTTL/CMOS input levels into TIA/RS-232-F levels.Device Information(1)PART NUMBER PACKAGE(PINS)BODY SIZE(NOM)MAX232ECDMAX232EIDSOIC(16)9.90mm×3.91mmMAX232ECDWMAX232EIDWSOIC WIDE(16)10.30mm×7.50mmMAX232ECNMAX232EINPDIP(16)19.30mm×6.35mmMAX232ECPWMAX232EIPWTSSOP(16) 5.00mm×4.40mm(1)For all available packages,see the orderable addendum atthe end of the data sheet.Logic Diagram(Positive Logic)14MAX232ESLLS723C –APRIL 2006–REVISED AUGUST 2016Product Folder Links:MAX232E Submit Documentation FeedbackCopyright ©2006–2016,Texas Instruments Incorporated12Device and Documentation Support12.1Receiving Notification of Documentation UpdatesTo receive notification of documentation updates,navigate to the device product folder on .In the upper right corner,click on Alert me to register and receive a weekly digest of any product information that has changed.For change details,review the revision history included in any revised document.12.2Community ResourcesThe following links connect to TI community resources.Linked contents are provided "AS IS"by the respective contributors.They do not constitute TI specifications and do not necessarily reflect TI's views;see TI's Terms of Use .TI E2E™Online Community TI's Engineer-to-Engineer (E2E)Community.Created to foster collaborationamong engineers.At ,you can ask questions,share knowledge,explore ideas and helpsolve problems with fellow engineers.Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools andcontact information for technical support.12.3TrademarksE2E is a trademark of Texas Instruments.All other trademarks are the property of their respective owners.12.4Electrostatic Discharge CautionThis integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.12.5GlossarySLYZ022—TI Glossary .This glossary lists and explains terms,acronyms,and definitions.13Mechanical,Packaging,and Orderable InformationThe following pages include mechanical,packaging,and orderable information.This information is the most current data available for the designated devices.This data is subject to change without notice and revision of this document.For browser-based versions of this data sheet,refer to the left-hand navigation.。

6.5Write ProtectionApplications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern, the W25Q32JV provides several means to protect the data from inadvertent writes.Write Protect Features∙Device resets when VCC is below threshold∙Time delay write disable after Power-up∙Write enable/disable instructions and automatic write disable after erase or program∙Software and Hardware (/WP pin) write protection using Status Registers∙Additional Individual Block/Sector Locks for array protection∙Write Protection using Power-down instruction∙Lock Down write protection for Status Register until the next power-up∙One Time Program (OTP) write protection for array and Security Registers using Status Register* *Note:This feature is available upon special order. Please contact Winbond for details.Upon power-up or at power-down, the W25Q32JV will maintain a reset condition while VCC is below the threshold value of V WI, (See Power-up Timing and Voltage Levels and Figure 43). While reset, all operations are disabled and no instructions are recognized. During power-up and after the VCC voltage exceeds V WI, all program and erase related instructions are further disabled for a time delay of t PUW. This includes the Write Enable, Page Program, Sector Erase, Block Erase, Chip Erase and the Write Status Register instructions. Note that the chip select pin (/CS) must track the VCC supply level at power-up until the VCC-min level and t VSL time delay is reached, and it must also track the VCC supply level at power-down to prevent adverse command sequence. If needed a pull-up resister on /CS can be used to accomplish this.After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Page Program, Sector Erase, Block Erase, Chip Erase or Write Status Register instruction will be accepted. After completing a program, erase or write instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (SRP, SRL) and Block Protect (CMP, TB, BP[2:0]) bits. These settings allow a portion or the entire memory array to be configured as read only. Used in conjunction with the Write Protect (/WP) pin, changes to the Status Register can be enabled or disabled under hardware control. See Status Register section for further information. Additionally, the Power-down instruction offers an extra level of write protection as all instructions are ignored except for the Release Power-down instruction.The W25Q32JV also provides another Write Protect method using the Individual Block Locks. Each 64KB block (except the top and bottom blocks, total of 62 blocks) and each 4KB sector within the top/bottom blocks (total of 32 sectors) are equipped with an Individual Block Lock bit. When the lock bit is 0, the corresponding sector or block can be erased or programmed; when the lock bit is set to 1, Erase or Program commands issued to the corresponding sector or block will be ignored. When the device is powered on, all Individual Block Lock bits will be 1, so the entire memory array is protected from Erase/Program. An “Individual Block Unlock (39h)” instruction must be issued to unlock any specific sector or block.The WPS bit in Status Register-3 is used to decide which Write Protect scheme should be used. When WPS=0 (factory default), the device will only utilize CMP, SEC, TB, BP[2:0] bits to protect specific areas of the array; when WPS=1, the device will utilize the Individual Block Locks for write protection.Figure 4c. Status Register-3Write Protect Selection (WPS) –Volatile/Non-Volatile WritableThe WPS bit is used to select which Write Protect scheme should be used. When WPS=0, the device will use the combination of CMP, SEC, TB, BP[2:0] bits to protect a specific area of the memory array. When WPS=1, the device will utilize the Individual Block Locks to protect any individual sector or blocks. Thedefault value for all Individual Block Lock bits is 1 upon device power on or after reset.Output Driver Strength (DRV1, DRV0) –Volatile/Non-Volatile WritableThe DRV1 & DRV0 bits are used to determine the output driver strength for the Read operations.Reserved Bits –Non FunctionalThere are a few reserved Status Register bits that may be read out as a “0” or “1”. It is recommended to ignore the values of those bits. During a “Write Status Register” instruction, the Reserved Bits can be written as “0”, but there will not be any effects.Status Register Memory Protection (WPS = 0, CMP = 0)Notes:1.X = don’t care2.L = Lower; U = Upper3.If any Erase or Program command specifies a memory region that contains protected data portion, this commandwill be ignored.Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h)The Write Status Register instruction allows the Status Registers to be written. The writable Status Register bits include: SEC, TB, BP[2:0] in Status Register-1; CMP, LB[3:1], QE, SRL in Status Register-2; DRV1, DRV0, WPS in Status Register-3. All other Status Register bit locations are read-only and will not be affected by the Write Status Register instruction. LB[3:1] are non-volatile OTP bits, once it is set to 1, it cannot be cleared to 0.To write non-volatile Status Register bits, a standard Write Enable (06h) instruction must previously have been executed for the device to accept the Write Status Register instruction (Status Register bit WEL must equal 1). Once write enabled, the instruction is entered by driving /CS low, sending the instruction code “01h/31h/11h”, and then writing the status register data byte as illustrated in Figure 9a.To write volatile Status Register bits, a Write Enable for Volatile Status Register (50h) instruction must have been executed prior to the Write Status Register instruction (Status Register bit WEL remains 0). However, SRL and LB[3:1] cannot be changed from “1” to “0” because of the OTP protection for these bits. Upon power off or the execution of a Software/Hardware Reset, the volatile Status Register bit values will be lost, and the non-volatile Status Register bit values will be restored.During non-volatile Status Register write operation (06h combined with 01h/31h/11h), after /CS is driven high, the self-timed Write Status Register cycle will commence for a time duration of t W(See AC Characteristics). While the Write Status Register cycle is in progress, the Read Status Register instruction may still be accessed to check the status of the BUSY bit. The BUSY bit is a 1 during the Write Status Register cycle and a 0 when the cycle is finished and ready to accept other instructions again. After the Write Status Register cycle has finished, the Write Enable Latch (WEL) bit in the Status Register will be cleared to 0.During volatile Status Register write operation (50h combined with 01h/31h/11h), after /CS is driven high, the Status Register bits will be refreshed to the new values within the time period of t SHSL2(See AC Characteristics). BUSY bit will remain 0 during the Status Register bit refresh period.Refer to section 7.1 for Status Register descriptions.Figure 9a. Write Status Register-1/2/3 Instruction。

ADM483E GENERAL INFORMATIONThe ADM483E is a robust RS-485 transceiver that operates from a single 5 V supply.It is ideally suited for operation in electrically harsh environ-ments or where cables may be plugged and unplugged. It is also immune to high RF field strengths without special shielding precautions. The ADM483E is intended for balanced data transmission and complies with both EIA Standards RS-485 and RS-422. It contains a differential line driver and a differential line receiver; it is suitable for half-duplex data transmission because the driver and receiver share the same differential pins. The input impedance on the ADM483E is 12 kΩ, allowing up to 32 transceivers on the differential bus.The ADM483E operates from a single 5 V ± 10% power supply. Excessive power dissipation caused by bus contention or by output shorting is prevented by a thermal shutdown circuit. This feature forces the driver output into a high impedance state if, during fault conditions, a significant temperature increase is detected in the internal driver circuitry.The receiver has a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating).A high level of robustness is achieved using internal protection circuitry, eliminating the need for external protection components such as transorbs or surge suppressors.Low electromagnetic emissions are achieved using slew limited drivers, minimizing interference both conducted and radiated. The ADM483E can transmit at data rates up to 250 kbps.A typical application for the ADM483E is illustrated in Figure 23. This figure shows a half-duplex link where data may be transferred at rates up to 250 kbps. A terminating resistor is shown at both ends of the link. This termination is not critical because the slew rate is controlled by the ADM483E and reflections are minimized.The communications network can be extended to include multipoint connections as shown in Figure 26. Up to 32 transceivers can be connected to the bus.612-23 Figure 23. Typical Half-Duplex Link ApplicationTable 6 and Table 7 show the truth tables for transmitting and receiving.1 X = don’t care.1 X = don’t care.ESD TRANSIENT PROTECTION SCHEMEThe ADM483E uses protective clamping structures on its inputs and outputs that clamp the voltage to a safe level and dissipate the energy present in ESD (electrostatic discharge).The protection structure achieves ESD protection up to ±15 kV according to the Human Body Model.ADM483ETYPICAL PERFORMANCE CHARACTERISTICS510152025303540455000.5 1.0 1.5 2.0 2.5OUTPUT LOW VOLTAGE (V)O U T P U T C U R R E N T (m A)06012-003Figure 3. Output Current vs. Receiver Output Low Voltage–30–25–20–15–10–501.52.0 2.53.0 3.54.0 4.55.0OUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A)06012-004Figure 4. Output Current vs. Receiver Output High Voltage3.94.04.14.24.34.44.5–40–20020406080TEMPERATURE (°C)O U T P U T H I G H V O L T A G E (V)06012-005Figure 5. Receiver Output High Voltage vs. Temperature 00.10.20.30.40.50.60.70.80.9–40–20020406080TEMPERATURE (°C)O U T P U T L O W V O L T A G E (V)06012-006Figure 6. Receiver Output Low Voltage vs. Temperature5101520253035404500.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5DIFFERENTIAL OUTPUT VOLTAGE (V)O U T P U T C U R R E N T (m A)06012-007Figure 7. Driver Output Current vs. Differential Output Voltage1.51.61.71.81.92.02.12.22.3–40–20020406080TEMPERATURE (°C)D I F FE R E N T I A L O U T P U T V O L T A G E (V)06012-008Figure 8. Driver Differential Output Voltage vs. TemperatureADM483E20406080100120140024681012OUTPUT LOW VOLTAGE (V)O U T P U T C U R R E N T (m A )06012-009Figure 9. Output Current vs. Driver Output Low Voltage–140–120–100–80–60–40–200–8–6–4–20246OUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A )06012-010Figure 10. Output Current vs. Driver Output High Voltage0100200300400500600TEMPERATURE (°C)S U P P L Y C U R R E N T (µA )06012-011Figure 11. ADM483E Supply Current vs. Temperature012345678910–60–40–20020406080100TEMPERATURE (°C)S H U T DO W N C U R R E N T (µA )06012-012Figure 12. Shutdown Current vs. TemperatureCH1 5.00V CH3 500mV CH2 500mV A CH1 2.80V06012-013Figure 13. ADM483E Receiver t PHLCH3 500mV A CH1 2.80V06012-014Figure 14. ADM483E Receiver t PLH Driven by External RS-485 DeviceADM483ETEST CIRCUITS AND SWITCHING CHARACTERISTICS06012-015Figure 15. Driver DC Test Load06012-016Figure 16. Driver Timing Test Circuit5VDI 0V0V +V O –V OV DIFF06012-017Figure 17. Driver Propagation DelaysΩOH06012-018Figure 18. Driver Enable and Disable Times (t DHZ , t DZH , t DZH(SHDN))VOUTV CC DE06012-019Figure 19. Driver Enable and Disable Times (t DZL , t DLZ , t DZL(SHDN))06012-020Figure 20. Receiver Propagation Delay Test CircuitTHE RISE TIME AND FALL TIME OF INPUT A AND INPUT B < 4ns+1V –1VBROV OHV OLA06012-021Figure 21. Receiver Propagation DelaysADM483EOH S1 OPEN S2 CLOSED S3 = +1.5VOHS1 CLOSED S2 OPEN S3 = –1.5V+5V0VV CCV OL06012-022Figure 22. Receiver Enable and Disable Times。

Device Command CodesThe system CPU provides control of all in-system READ, WRITE, and ERASE operationsof the device via the system bus. The device manages all block-erase and word-programalgorithms.Device commands are written to the CUI to control all device operations. The CUI doesnot occupy an addressable memory location; it is the mechanism through which thedevice is controlled.Note: For a dual device, all setup commands should be re-issued to the device when adifferent die is selected.Table 10: Command Codes and DefinitionsErase OperationsBLOCK ERASE CommandERASE operations are performed on a block basis. An entire block is erased each time aBLOCK ERASE command sequence is issued, and only one block is erased at a time.When a block is erased, each bit within that block reads as a logical 1.A BLOCK ERASE operation is initiated by writing the BLOCK ERASE SETUP commandto the address of the block to be erased, followed by the BLOCK ERASE CONFIRM com-mand. If the device is placed in standby (CE# de-asserted) during a BLOCK ERASE oper-ation, the device completes the operation before entering standby. The V PP value mustbe above V PPLK and the block must be unlocked.During a BLOCK ERASE operation, the device executes a sequence of internally-timedevents that conditions, erases, and verifies all bits within the block. Erasing the arraychanges the value in each cell from a 1 to a 0. Memory block array cells that with a valueof 1 can be changed to 0 only by programming the block.The status register can be examined for block erase progress and errors by reading anyaddress. The device remains in the read status register state until another command iswritten. SR0 indicates whether the addressed block is erasing. SR7 is set upon erasecompletion.SR7 indicates block erase status while the sequence executes. When the BLOCK ERASEoperation has completed, SR5 = 1 (set) indicates an erase failure. SR3 = 1 indicates thatthe device could not perform the BLOCK ERASE operation because V PP was outside ofits acceptable limits. SR1 = 1 indicates that the BLOCK ERASE operation attempted toerase a locked block, causing the operation to abort.Before issuing a new command, the status register contents should be examined andthen cleared using the CLEAR STATUS REGISTER command. Any valid command canfollow after the BLOCK ERASE operation has completed.The BLOCK ERASE operation is aborted by performing a reset or powering down thedevice. In either case, data integrity cannot be ensured, and it is recommended to eraseagain the blocks aborted.BLANK CHECK CommandThe BLANK CHECK operation determines whether a specified main block is blank; thatis, completely erased. Other than a BLANK CHECK operation, only a BLOCK ERASE op-eration can ensure a block is completely erased. BLANK CHECK is especially usefulwhen a BLOCK ERASE operation is interrupted by a power loss event.A BLANK CHECK operation can apply to only one block at a time. The only operationallowed simultaneously is a READ STATUS REGISTER operation. SUSPEND and RE-SUME operations and a BLANK CHECK operation are mutually exclusive.A BLANK CHECK operation is initiated by writing the BLANK CHECK SETUP commandto the block address, followed by the CHECK CONFIRM command. When a successfulcommand sequence is entered, the device automatically enters the read status state.The device then reads the entire specified block and determines whether any bit in theblock is programmed or over-erased.BLANK CHECK operation progress and errors are determined by reading the status reg-ister at any address within the block being accessed. SR7 = 0 is a BLANK CHECK busystatus. SR7 = 1 is a BLANK CHECK operation complete status. The status register shouldbe checked for any errors and then cleared. If the BLANK CHECK operation fails, mean-ing the block is not completely erased, SR5 = 1. CE# or OE# toggle (during polling) up-dates the status register.The READ STATUS REGISTER command must always be followed by a CLEAR STATUSREGISTER command. The device remains in status register mode until another com-mand is written to the device. Any command can follow once the BLANK CHECK com-mand is complete.ERASE SUSPEND CommandThe ERASE SUSPEND command suspends a BLOCK ERASE operation that is in pro-gress, enabling access to data in memory locations other than the one being erased. TheERASE SUSPEND command can be issued to any device address. A BLOCK ERASE oper-ation can be suspended to perform a WORD or BUFFER PROGRAM operation, or aREAD operation within any block except the block that is erase suspended.When a BLOCK ERASE operation is executing, issuing the ERASE SUSPEND commandrequests the device to suspend the erase algorithm at predetermined points. The devicecontinues to output status register data after the ERASE SUSPEND command is issued.Block erase is suspended when SR[7,6] are set.To read data from the device (other than an erase-suspended block), the READ ARRAYcommand must be issued. During erase suspend, a PROGRAM command can be issuedto any block other than the erase-suspended block. Block erase cannot resume untilprogram operations initiated during erase suspend complete. READ ARRAY, READ STA-TUS REGISTER, READ DEVICE IDENTIFIER, READ CFI, and ERASE RESUME are validcommands during erase suspend. Additionally, CLEAR STATUS REGISTER, PROGRAM,PROGRAM SUSPEND, BLOCK LOCK, BLOCK UNLOCK, and BLOCK LOCK DOWN arevalid commands during an ERASE SUSPEND operation.During an erase suspend, de-asserting CE# places the device in standby, reducing activecurrent. V PP must remain at a valid level, and WP# must remain unchanged while inerase suspend. If RST# is asserted, the device is reset.ERASE RESUME CommandThe ERASE RESUME command instructs the device to continue erasing, and automati-cally clears SR[7,6]. This command can be written to any address. If status register errorbits are set, the status register should be cleared before issuing the next instruction.RST# must remain de-asserted.Erase ProtectionWhen V PP = V IL, absolute hardware erase protection is provided for all device blocks. IfV PP is at or below V PPLK, ERASE operations halt and SR3 is set indicating a V PP-level er-ror.Figure 12: Block Locking State DiagramProgram/Erase Allowed WP# = V IL = 0WP# = V IL = 0Program/Erase PreventedProgram/Erase Prevented WP# = V IH = 1Program/Erase AllowedWP# = V IH = 1Note: 1.D0h = UNLOCK command; 01h = LOCK command; 60h (not shown) LOCK SETUP com-mand; 2Fh = LOCK DOWN command.Block Locking During SuspendBlock lock and unlock changes can be performed during an erase suspend. To change block locking during an ERASE operation, first issue the ERASE SUSPEND command.Monitor the status register until SR7 and SR6 are set, indicating the device is suspended and ready to accept another command.Next, write the desired lock command sequence to a block, which changes the lock state of that block. After completing BLOCK LOCK or BLOCK UNLOCK operations, re-sume the ERASE operation using the ERASE RESUME command.Note:A BLOCK LOCK SETUP command followed by any command other than BLOCK LOCK,BLOCK UNLOCK, or BLOCK LOCK DOWN produces a command sequence error and set SR4 and SR5. If a command sequence error occurs during an erase suspend, SR4 and SR5 remains set, even after the erase operation is resumed. Unless the Status Register is cleared using the CLEAR STATUS REGISTER command before resuming the ERASE op-eration, possible erase errors may be masked by the command sequence error.If a block is locked or locked-down during an erase suspend of the same block, the lock status bits change immediately. However, the ERASE operation completes when it is re-sumed. BLOCK LOCK operations cannot occur during a program suspend.Selectable OTP BlocksThe OTP security feature on the device is backward-compatible to the earlier genera-tion devices. Contact your local Micron representative for details about its implementa-tion.Password AccessThe password access is a security enhancement offered on the device. This feature pro-tects information stored in array blocks by preventing content alteration or reads until avalid 64-bit password is received. The password access may be combined with nonvola-tile protection and/or volatile protection to create a multi-tiered solution.Contact your Micron sales office for further details concerning password access.。