数字电路卡诺图化简

- 格式:ppt

- 大小:2.59 MB

- 文档页数:30

The way to grow is to know how to shut up and work hard, to be low-key and humble, to learn to be strong, and to be the person you want to be in every cherished day.(WORD文档/A4打印/可编辑/页眉可删)数字电路面试题及答案同步电路和异步电路的区别是什么?(仕兰微电子)异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,但它同时也用在时序电路中,此时它没有统一的时钟,状态变化的时刻是不稳定的,通常输入信号只在电路处于稳定状态时才发生变化。

也就是说一个时刻允许一个输入发生变化,以避免输入信号之间造成的竞争冒险。

电路的稳定需要有可靠的建立时间和持时间,待下面介绍。

同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。

这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。

比如D触发器,当上升延到来时,寄存器把D端的电平传到Q输出端。

下面介绍一下建立保持时间的问题。

建立时间(tsu)是指在触发器的时钟上升沿到来以前,数据稳定不变的时间。

如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(th)是指在触发器的时钟上升沿到来以后,数据稳定不变的时间。

如果保持时间不够,数据同样不能被打入触发器。

数据稳定传输必须满足建立时间和保持时间的要求,否则电路就会出现逻辑错误。

在同步电路设计中一般采用D触发器,异步电路设计中一般采用Latch2、什么是同步逻辑和异步逻辑?(汉王笔试)同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系组合电路与时序电路区别组合逻辑电路是具有一组输出和一组输入的非记忆性逻辑电路,它的基本特点是任何时刻的输出信号状态仅取决于该时刻各个输入信号状态的组合,而与电路在输入信号作用前的状态无关。

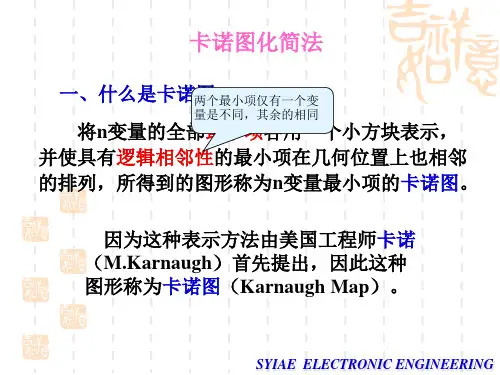

卡诺图化简逻辑函数的方法和理论依据摘要:从最小项的定义和性质入手,简述卡诺图化简逻辑函数的理论依据以及化简是否达到最简形式的判定标准。

通过举例来解释利用卡诺图化简少变量逻辑函数的一般方法,以及卡诺图在数字电子技术中其他应用。

另外介绍一种多变量逻辑函数的卡诺图解法。

关键词:卡诺图;最小项;逻辑函数化简;多变量0 引言在逻辑电路的分析和设计中,经常会遇到逻辑函数的化简问题。

如果利用常规的公式法化简,除需要掌握大量的基本公式外,还需要能够灵活、交替地运用各种方法,方可求得最简结果,而且有时不易判断是否已简化到最简形式,技巧性较强,对使用者的要求较高。

当所需化简的逻辑函数输入变量较少时(一般不大于4个),利用科诺图化简法可以更简单、直接的得到逻辑函数的最简表达式。

因此逻辑函数的卡诺图化简法在实际分析、设计电路时有很广泛的应用。

1 最小项定义及其性质1.1最小项的定义设有n个逻辑变量,由它们组成具有n个变量的“与”项中,每个变量以原变量或者反变量的形式出现一次且仅出现一次,则称这个与项为最小项。

对于n个变量来说,可有2n个最小项。

任何一个逻辑函数均可表示成惟一的一组最小项之和,称它为标准的与或表达式,也称为最小项表达式。

对于任意一个最小项,只有一组变量取值使它的值为1,而变量的其他取值都使该最小项为0。

事实上,真值表的每一行对应着一个最小项。

表(1)中列出了最小项取值为1时,各输入变量的取值。

我们约定:将最小项为l时各输入变量的取值视为二进制,其对应的十进制i作为最小项的编号,并把该最小项记作m i。

如A、B、C三个变量有2n =8个最小项,如表(1)所示。

图(1)1.2最小项的性质最小项具有以下三个性质:(1)全体最小项之和为1;(2)任意两个最小项之积为0;(3)若两个最小项之间只有一个变量不同,即在一个最小项中是原变量,在另一个最小项中是反变量,其余各变量均相同,则称这两个最小项是相邻项。

两个相邻的最小项之和可以合并成一个与项,并消去一个因子。

数字逻辑中逻辑化简方法

数字逻辑中常用的逻辑化简方法主要有两种,分别是布尔代数化简和卡诺图化简。

1. 布尔代数化简:

布尔代数是一种以布尔运算为基础的代数系统,用于描述和操作逻辑语句。

布尔代数化简的基本方法包括逻辑公式的代数化简与逻辑电路的代数化简。

逻辑公式的代数化简是通过应用布尔运算的性质和规则,将复杂的逻辑表达式化简为较简单的形式。

逻辑电路的代数化简是通过对逻辑电路的输入和输出进行布尔代数运算,来简化逻辑电路的实现。

2. 卡诺图化简:

卡诺图是一种图形化的逻辑化简方法,通过将逻辑表达式的真值表绘制成图形化的方式来进行逻辑化简。

卡诺图化简的基本步骤包括:

- 绘制逻辑表达式的真值表,将结果填入卡诺图中。

- 查找能够覆盖到1的最大方块(称为主体)。

- 根据主体中1的位置和数量,确定化简后的逻辑表达式。

卡诺图化简方法适用于逻辑表达式的较简单的情况,能够快速有效地进行逻辑化简。

数字电路中的卡诺图――――――――――朱必成 F卡诺图是一幅或多幅方格子图形。

二至四变量卡诺图各占一幅图,五变量两幅,六变量四幅构成。

它贯穿了数字电路的各个层面,是十分重要且有用的基础知识。

经过课上学习与课外资料的查询,对其有了一定了解与认识。

1 化简的依据卡诺图具有循环邻接的特性,若图中两个相邻的方格均为1,则用两个相邻最小项的和表示可以消去一个变量,如4变量卡诺图中的方格5和方格7,它们的逻辑加是消取了变量C,即消去了相邻方格中不相同的那个因子。

若卡诺图中4个相邻的方格为1,则这4个相邻的最小项的和将消去两个变量,如4变量卡诺图中方格2、3、7、6,它们的逻辑加是消去了变量B和D,即消去相邻4个方格中不相同的那两个因子,这样反复应用A+=1的关系,就可使逻辑表达式得到简化。

这就是利用卡诺图法化简逻辑函数的基本原理。

2 用卡诺图化简逻辑函数的步骤1.将逻辑函数写成最小项表达式。

2.按最小项表达式填卡诺图,凡式中包含了的最小项,其对应方格填1,其余方格填0。

3.合并最小项,即将相邻的1方格圈成一组(包围圈,每一组含2n个方格),对应每个包围圈写成一个乘积项。

4.将所有包围圈所对应的乘积项相加。

有时也可以由真值表直接填卡诺图,1、2两步可以合成一步。

3画包围圈时应遵循的原则1.包围圈内的方格数必定是2n 个,n 等于0、1、2、3、…2.相邻方格包括上下底相邻,左右边相邻和四角相邻。

3.同一方格可以被不同的包围圈重复包围,但新增包围圈中一定要有新的1方格,否则该包围圈为多余。

4.包围圈内的1方格数要尽可能多,即包围圈应尽可能大。

4举例:5.卡诺图的应用技巧: (1)。

卡诺图中圈零:如 BD BC AD AC F +++=))((B A D C B A D C F F BA D C F ++=+==+= (2) 任意项的处理:实际中经常会遇到这样的问题,在真值表内对于变量的某些取值组合,函数的值可以是任意的,或者这些变量的取值根本不会出现,这些变量取值所对应的最小项称为无关项或任意项。