数字集成电路(中文)第六章

- 格式:doc

- 大小:55.00 KB

- 文档页数:3

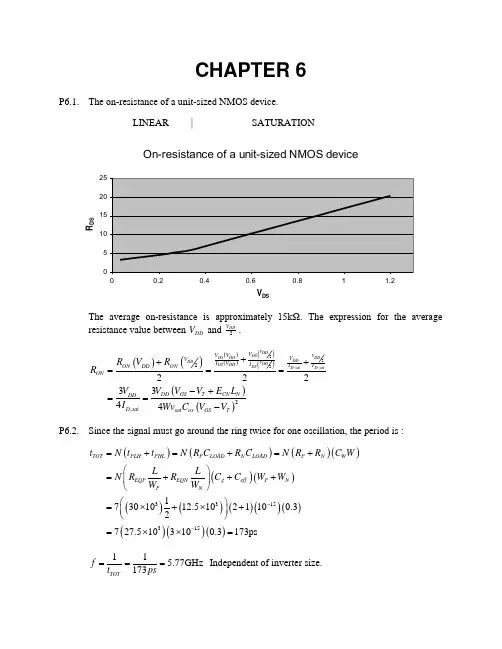

CHAPTER 6P6.1. The on-resistance of a unit-sized NMOS device.LINEAR | SATURATIONOn-resistance of a unit-sized NMOS device051015202500.20.40.60.811.2V DSR D SThe average on-resistance is approximately 15kΩ. The expression for the average resistance value between DD V and 2DDV .()()()()()()()()222,,22,2223344V DD DSV DS DD DDDD DDV DDDS DD DS D satD satV V V V V I V I I ON DD ON ON DD GS T CN N DDD sat sat ox GS T R V R R V V VE L V I Wv C V V +++===-+==-P6.2. Since the signal must go around the ring twice for one oscillation, the period is :()()()()()()()()()()()()()()331531517301012.51021100.32727.5103100.3173ps TOT PLH PHL P LOAD N LOAD P N W EQP EQN g eff P N P N t N t t N R C R C N R R C W L L N R R C C W W W W --=+=+=+⎛⎫=+++ ⎪⎝⎭⎛⎫=⨯+⨯+ ⎪⎝⎭=⨯⨯=115.77GHz 173TOTf t ps=== Independent of inverter size.P6.3. SPICE.P6.4. The self-capacitance in these cases are the capacitances that will make the transition from0 to DD V or vice versa.a. In this case, all the internal nodes will be charged so the self-capacitance is :()2233313SELF eff eff C C W W W W W C W =++++=b. In this case, all the internal nodes but the one above the bottom NMOS transistor will be charged:()223310SELF eff eff C C W W W W C W =+++=c. If we assume a worst-case scenario, this node will be charged up to DD V from 0.()2233313SELF eff eff C C W W W W W C W =++++=d. The node above the bottom-most NMOS transistor has already been discharged.()223310SELF eff eff C C W W W W C W =+++=P6.5. SPICEP6.6. For optimum sizing given four inverters.()()()()()()()()()()()()44332214111111120012005.8911200203.895.891203.8934.645.89134.64 5.895.8915.8915.8945.890.525.5OUT NPE LE FO SE LE C C SE LE C C SE LE C C SE LE C C SE D LE FO P SE P =⨯=====⨯===⨯===⨯===⨯====⨯+=+=+=∏∑∑For the number of devices for optimum delay:log log log log log log12005.11log log 4N N SE SE PE SE PE N SE PEPE N SE =======Setting 5N =gives:()()()()()()()()5544332215114.1211200290.634.121290.6370.394.12170.3917.054.12117.05 4.124.1214.1214.1244.120.518.5OUT N SE LE C C SE LE C C SE LE C C SE LE C C SE LE C C SE D LE FO P SE P ===⨯===⨯===⨯===⨯===⨯====⨯+=+=+=∑∑P6.7. Solution for NAND3For the first NAND3, LE=5W/3W=5/3. For the second NAND3, the delay is not the same asthe basic inverter. So use the more general formula:310/25/33nand W R LE WR⨯== Same as the first case.a.For equal rise and fall time, we double the sizes of the transistors which leads to:313LE==b.For the pseudo-NMOS, we must first calculate the currents, which are different forpull-up and pull-down in the case of a pseudo-NMOS.For the case of the pull-up, only the PMOS is charging the output, for equal delays,we double the size of the PMOS and NMOS to obtain:23LE=P6.9.a.53 LE=b.53 LE=c.82,33 R FLE LE==d.4,23R FLE LE==P6.10.a.813RLE st gate =b.523FLE nd gate =()()()()()()()()()()()()()()45343433221411451110002222336.8711000145.656.87145.6535.366.8735.36 6.876.871 6.8716.8746.870.51 1.50.5OUT NN N PE LE FO SE LE C C SE LE C C SE LE C C SE LE C C SE D SE P SE P ⎛⎫⎛⎫=⨯== ⎪⎪⎝⎭⎝⎭===⨯===⨯===⨯===⨯====+=+=++++∏∑∑31=P6.12.()()()()()()()()()()()()()()()6345434332211546410001777833311.5510001173.2111.55173.2112511.5525411.5511.55111.551111.55OUT N N PE LE FO BE SE LE C BE C SE LE C BE C SE LE C BE C SE LE C BE C SE D SE P ⎛⎫⎛⎫⎛⎫=⨯⨯== ⎪⎪⎪⎝⎭⎝⎭⎝⎭===⨯⨯===⨯⨯===⨯⨯===⨯⨯====+∏()()41411.550.51 1.5251.2N SE P =+=++++=∑∑()()()()()()()()()()()635735445712(2)(4)800066730333314.6800011095.814.610951175.114.64512(4175.1500)533533OUT PE LE FO BE SE LE C BE C SE LE C BE C SE PE LE FO BE SE ⎛⎫⎛⎫⎛⎫=⨯⨯== ⎪⎪⎪⎝⎭⎝⎭⎝⎭===⨯⨯===⨯⨯===⎛⎫⎛⎫=⨯⨯=⨯+= ⎪⎪⎝⎭⎝⎭==∏∏()()()()()()()()()()()5343322151117.4712001114.317.54114.32317.517.5117.51117.53(17.5)214.60.51 1.5 2.25288.9NN N LE C BE C SE LE C BE C SE LE C BE C SE D SE P SE P =⨯⨯===⎛⎫⎪⨯⨯⎝⎭===⨯⨯====+=+=++++++=∑∑To minimize the delay, a estimate of the number of needed stages can be performed :log log 6637049.610log log 4SE PE N SE =∴===≈ The additional stages can be implemented as inverters attached at the input.P6.14. Consider the following situations :C LV inC LV outOutput high-to-low Output low-to-highIn the first case, the output is making a transition from high to low. The next inverter (not shown) has the PMOS in the cutoff region and the NMOS in the linear region. In these regions, the input capacitance of the next gate can be computed as follows:PMOS: C GP =C g x 2W x (1/2) NMOS: C GN =C g x WFor the output low-to-high transition, we have the PMOS linear and the NMOS cutoff: PMOS: C GP =C g x 2W NMOS: C GN =C g x W (1/2)Clearly, the second case has a larger total capacitance and hence a larger effective C g .P6.15. For this problem we examine ramp inputs as compared to step inputs. In both cases below,the transistors being driven enter the linear region and experience larger gate capacitances than the step input case. Therefore, C g is always larger for ramp inputs.C LC LV outpositive-going input ramp negative-going input rampV V DDP6.16. The FO4 delay for 0.18um is approximately 75ps. For 0.13um it is 55ps. Therefore, theconstant for the equation is roughly 420ps/um.。

第六章Verilog的数据类型及逻辑系统学习内容:•学习Verilog逻辑值系统•学习Verilog中不同类的数据类型•理解每种数据类型的用途及用法•数据类型说明的语法Verilog采用的四值逻辑系统’0’, Low, False, Logic Low, Ground,VSS,Negative Assertion‘1’, High, True, Logic High, Power,VDD, VCC, Positive Assertion’X’ Unknown: Occurs at Logical Which Cannotbe Resolved ConflictHiZ, High Impedance, Tri-Stated,Disabled Driver (Unknown)主要数据类型Verilog主要有三类(class)数据类型:•net (线网): 表示器件之间的物理连接•register (寄存器):表示抽象存储元件•parameters(参数) : 运行时的常数(run-time constants)net(线网)net需要被持续的驱动,驱动它的可以是门和模块。

当net驱动器的值发生变化时,Verilog自动的将新值传送到net上。

在例子中,线网out由or门驱动。

当or门的输入信号置位时将传输到线网net上。

•有多种net 类型用于设计(design-specific)建模和工艺(technology-specific)建模•没有声明的net 的缺省类型为1 位(标量)wire 类型。

但这个缺省类型可由下面的编译指导改变:`default_nettype <nettype>net 类型功能wire, trisupply1, supply0wor, triorwand, triandtriregtri1, tri0标准内部连接线(缺省)电源和地多驱动源线或多驱动源线与能保存电荷的net 无驱动时上拉/下拉综合编译器不支持的net 类型•wire类型是最常用的类型,只有连接功能。

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm 自己算4、EDA 设计流程IP 设计SystemC 模块设计(verilog )版图设计电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys 版权):.db .lib (可读).sdb .slib第2章 器件基础1、保护IC 的输入器件以抗静电荷(ESD 保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

ξC取决于掺杂浓度和外加的垂直电场强度器件在V DS达到V GS --V T 之前就已经进入饱和状态,所以与相应的长沟道器件相比,短沟道器件饱和区范围更大反面整理P63 3.3.2 静态状态下的MOS晶体管相关参数以及公式(尤其是速度饱和)4、MOS管二阶效应阈值变化:随着器件尺寸的缩小,阈值电压变成与L、W、V DS有关短沟效应(漏端感应势垒降低(DIBL)):电压控制耗尽区宽度,V DS提高将会导致势垒降低,甚至过高的V DS将会导致源漏短路,称为源漏穿流窄沟效应:沟道耗尽区并不立即在晶体管边沿终止,而是会向绝缘场氧下面延伸一些,栅电压必须维持这一额外的耗尽电荷才能建立一条导电沟道,在W值较小时将会引起阈值电压升高亚阈值导通:在V GS接近甚至略小于V T时,I D仍然存在热载流子效应:原因:小尺寸器件中的强电场引起高能热电子与晶格碰撞产生电子空穴对,引起衬底电流;电子在强总校电厂的作用下穿过栅氧,引起栅电流。

第二节有比逻辑 VDD 电阻负载 RL F In1 In2 In3 PDN VSS (a 电阻负载 In1 In2 In3 PDN VSS (b 耗尽型NMOS负载耗尽型负载 VT < 0 VSS F In1 In2 In3 PDN VSS (c 伪NMOS F VDD PMOS负载 VDD 目的: 与互补CMOS相比可以减少器件的数目数字大规模集成电路清华大学微电子所周润德第六章(2)第 1 页 2004-10-27有比逻辑 VDD Resistive Load 共 N 个晶体管 + 负载 RL VOH = VDD VOL = F RPN RPN + RL In1 In2 In3 不对称响应 PDN t pL = 0.69 RLCL 有静态功耗 VSS 2004-10-27 数字大规模集成电路清华大学微电子所周润德第六章(2)第 2 页伪NMOS ( Pseudo-NMOS VDD A B C D F CL VOH = VDD (similar to complementary CMOS 2 V OL ⎞ kp ⎛ 2 – ------------- ⎟ = ------ ( V – V – V V k ⎜( V DD Tp n DD Tn OL 2 ⎠ 2 ⎝类似于互补CMOS kp V OL = ( VDD – V T 1 – 1 – ------ (assuming that V T = V Tn = VTp k n SMALLER AREA & LOAD BUT STATIC POWER DISSIPATION!!! 较小的面积和驱动负载,但有静态功耗 2004-10-27 数字大规模集成电路清华大学微电子所周润德第六章(2)第 3 页Pseudo-NMOS 电压传输特性(VTC) VDD 3.0 PMOS负载 VSS Vout [V] 2.5 2.0 W/Lp = 4 F In1 In2 In3 PDN 1.5 W/Lp = 2 1.0 0.5 W/Lp = 0.5 W/Lp = 0.25 W/Lp = 1 VSS 伪NMOS 0.0 0.0 0.5 1.0 1.5 2.0 2.5 Vin [V] 在性能、功耗+噪声容限之间综合考虑 2004-10-27 数字大规模集成电路清华大学微电子所周润德第六章(2)第 4 页伪 nMOS / pMOS 逻辑(1)伪 nMOS 逻辑的基本电路 1. 2. 3. 4. 5. p 管作负载,其栅极接地 n 个输入端的伪 nMOS 电路有 n + 1 个管子 kn k p 的比例影响传输特性的形状及反相器 V OL 的值当驱动管导通时,总有一恒定的 DC 电流(静态功耗)当驱动管和负载管均不导通时,输出电压取决于管子的次开启特性 6. 噪声容限 N M L 比 N M H 差很多 7. 基本方程 8. 应用场合 2004-10-27 数字大规模集成电路清华大学微电子所周润德第六章(2)第 5 页伪 nMOS 逻辑 Vdd 负载 Vout Vin 驱动 GND 伪 pMOS 逻辑 Vdd 驱动 Vin Vout 负载 GND 2004-10-27 数字大规模集成电路清华大学微电子所周润德第六章(2)第 6 页(2)伪 NMOS 的设计:驱动管与负载管的尺寸应有一合适的比率 1. 为减少静态功耗,驱动电流 IL 应当小 2. 为了得到合理的 NML ,VOL = IL(RPDN 应当低 3. 为了减少 t PLH = C L V DD , IL 应当大 2IL 4.为了减少 t PHL = 0.69 R PDN C L ,RPDN 应当小条件 1 与 3 是矛盾的,可见:实现一个较快的门意味着较多的静态功耗及较小的噪声余量。

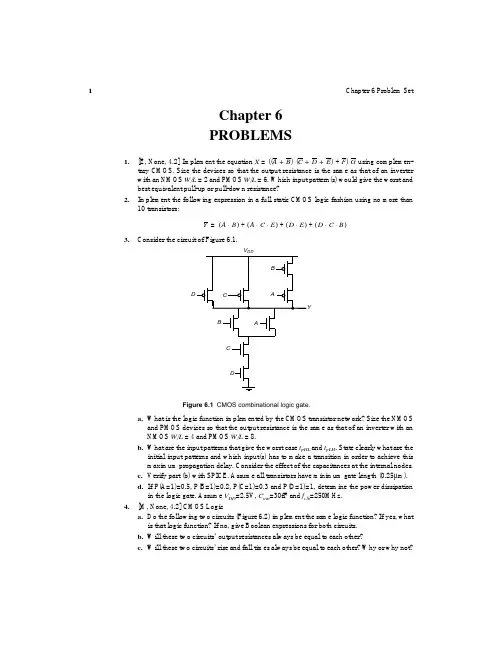

第六章习题

1.使用互补CMOS电路实现逻辑表达式

X A B C D E F G

=++++。

当反相器的NMOS W/L=2, PMOS (()())

W/L=6时输出电阻相同,根据这个确定该网络中各个器件尺寸。

哪一种输入模式将会有最差和最好的上拉和下拉电阻?

2.考虑下图,

a.下面的CMOS晶体管网络实现的是什么逻辑功能?

反相器的NMOS W/L=4, PMOS W/L=8时输出电阻相同,

根据这个确定该网络中各个器件尺寸。

b.当输入是什么模式时

t和p L H t最差。

最初的输入模

pH L

式是什么,必须采用哪一种输入才能取得最大传输延

时?考虑在内部节点中的电容的影响。

3.CMOS组合逻辑

a.下图中的两个电路A和B是否实现同一个逻辑函数?如果是的话,是什么逻辑;如果不是的话,给出两

个电路的布尔表达式。

b.这两个电路的输出电阻是否总是相同?分析解释。

c.这两个电路的上升下降时间是否总是相同?分析解释。

4. 使用DCVSL实现F ABC ACD

=+。

假设A,B,

=+和F A BC ACD

C,D和他们的反作为输入是允许的。

要求使用最少的晶体管。

5.一个复杂逻辑门电路如下图所示。

a.写出输出F和G的布尔表达式。

并说明这个电路实现的是什么功能。

b.这个电路属于哪一类电路。

6.分析下图所示电路实现什么功能。

7.使用NMOS传输管逻辑实现F ABC ABC ABC ABC

=+++。

设计一个DCVSL门实现同样的功能。

假设A,B,C和他们的反都可以实现。