ZKJ晶振3225封装40MHz-15PF-10PPM规格书

- 格式:pdf

- 大小:413.09 KB

- 文档页数:4

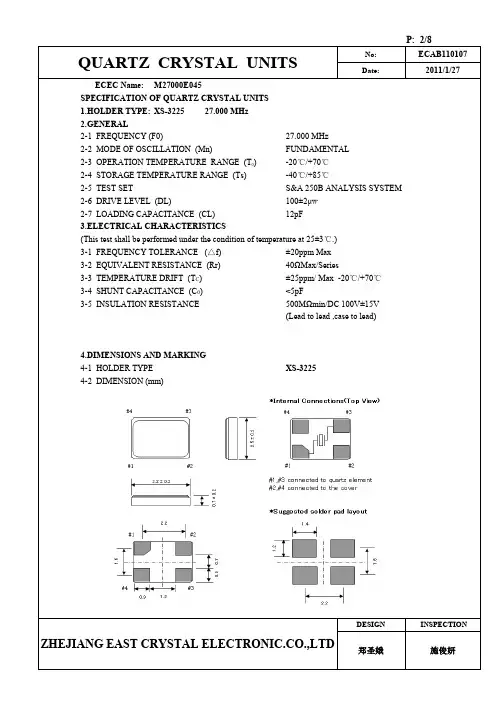

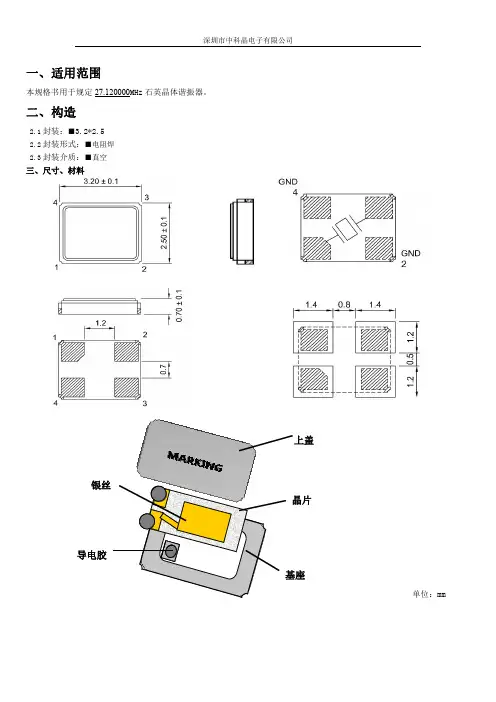

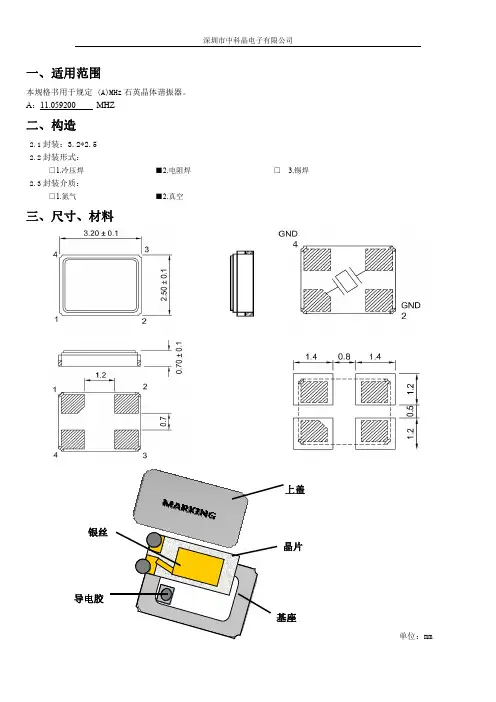

ECEC Name:M27000E045SPECIFICATION OF QUARTZ CRYSTAL UNITS1.HOLDER TYPE:XS-322527.000 MHz2.GENERAL2-1 FREQUENCY (F0) 27.000 MHz2-2 MODE OF OSCILLATION (Mn)FUNDAMENTAL)-20℃/+70℃2-3 OPERATION TEMPERATURE RANGE (T2-4 STORAGE TEMPERATURE RANGE (Ts)-40℃/+85℃2-5 TEST SET S&A 250B ANALYSIS SYSTEM2-6 DRIVE LEVEL (DL)100±2μw2-7 LOADING CAPACITANCE (CL)12pF3.ELECTRICAL CHARACTERISTICS(This test shall be performed under the condition of temperature at 25±3℃.)3-1 FREQUENCY TOLERANCE (△f)±20ppm Max3-2 EQUIVALENT RESISTANCE (Rr)40ΩMax/Series3-3 TEMPERATURE DRIFT (T C)±25ppm/ Max-20℃/+70℃3-4 SHUNT CAPACITANCE (C0)<5pF3-5 INSULATION RESISTANCE 500MΩmin/DC 100V±15V(Lead to lead ,case to lead)4.DIMENSIONS AND MARKING4-1 HOLDER TYPE XS-32254-2 DIMENSION (mm) Array DESIGN INSPECTIONZHEJIANG EAST CRYSTAL ELECTRONIC.CO.,LTD4-4-2 Dimensions of the reel4-4-3 Packing and Label1 Reel=3000pcsBox type(Reel quantity)Box size(L×W×H) mmAtype200×200×140Manufactory name: ZHEJIANG EAST CRYSTAL ELEC.CO.,LTDZHEJIANG EAST CRYSTAL ELECTRONIC.CO.,LTD5-5.REFLOW(WAVE)SOLDERINGFollowing profile of heat stress is applied to resonator,then being place in the naturalcondition for 1 hour,resonator shall be measured.260±5℃ 10~20sec150~190℃ 120sec5-6.SOLDERING DIPTerminals/lead-wires of specimen shall be dipped into solder melter tankat +260℃±5℃ for 3 sec.Dipping depth shall be 2mm from the bottom of specimens body.(Afterapplying ROSIN FLUX) soldering portion shall be covered in over 95% ofTerminals/lead-wires dipped.5-7.HUMIDITYElectrical characteristics shall be satisfied after letting it alone at 65±2℃in humidity of 90~95% for 500 hours.5-8.STORAGE IN LOW TEMPRATUREElectrical characteristics shall be satisfied after letting it alone at -40±2℃for 500 hours.5-9.STORAGE IN HIGH TEMPRATUREElectrical characteristics shall be satisfied after letting it alone at 85±2℃for 500 hours.DESIGN INSPECTION ZHEJIANG EAST CRYSTAL ELECTRONIC.CO.,LTDNo:ECAB110107Date:2011/1/276.Structure IllustrationNo.123456DESIGN INSPECTION郑圣娥施俊妍Internal Electrode PKG(Base)ZHEJIANG EAST CRYSTAL ELECTRONIC.CO.,LTDCERAMIC+Au PLATING Au PLATING QUARTZ CRYSTAL UNITSMaterialsItemsLID(Cap)External Electrode Fe ALLOYAg SiO2Ag+Epoxy Resin Element(Blank)Conductive Adhesive 154326。

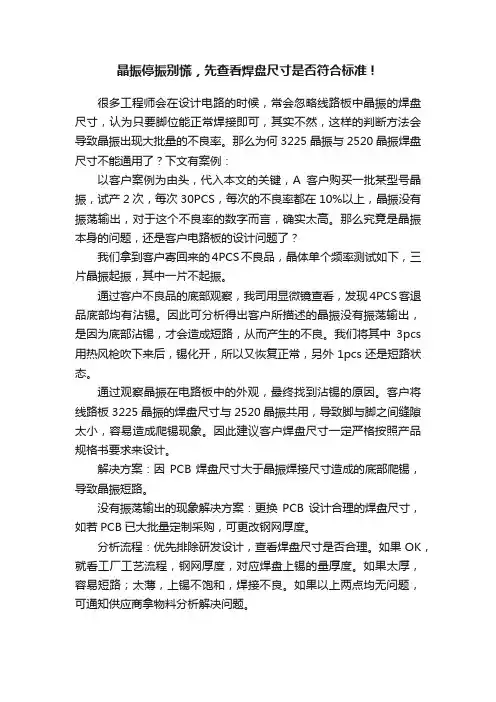

晶振停振别慌,先查看焊盘尺寸是否符合标准!很多工程师会在设计电路的时候,常会忽略线路板中晶振的焊盘尺寸,认为只要脚位能正常焊接即可,其实不然,这样的判断方法会导致晶振出现大批量的不良率。

那么为何3225晶振与2520晶振焊盘尺寸不能通用了?下文有案例:以客户案例为由头,代入本文的关键,A客户购买一批某型号晶振,试产2次,每次30PCS,每次的不良率都在10%以上,晶振没有振荡输出,对于这个不良率的数字而言,确实太高。

那么究竟是晶振本身的问题,还是客户电路板的设计问题了?我们拿到客户寄回来的4PCS不良品,晶体单个频率测试如下,三片晶振起振,其中一片不起振。

通过客户不良品的底部观察,我司用显微镜查看,发现4PCS客退品底部均有沾锡。

因此可分析得出客户所描述的晶振没有振荡输出,是因为底部沾锡,才会造成短路,从而产生的不良。

我们将其中3pcs 用热风枪吹下来后,锡化开,所以又恢复正常,另外1pcs还是短路状态。

通过观察晶振在电路板中的外观,最终找到沾锡的原因。

客户将线路板3225晶振的焊盘尺寸与2520晶振共用,导致脚与脚之间缝隙太小,容易造成爬锡现象。

因此建议客户焊盘尺寸一定严格按照产品规格书要求来设计。

解决方案:因PCB焊盘尺寸大于晶振焊接尺寸造成的底部爬锡,导致晶振短路。

没有振荡输出的现象解决方案:更换PCB设计合理的焊盘尺寸,如若PCB已大批量定制采购,可更改钢网厚度。

分析流程:优先排除研发设计,查看焊盘尺寸是否合理。

如果OK,就看工厂工艺流程,钢网厚度,对应焊盘上锡的量厚度。

如果太厚,容易短路;太薄,上锡不饱和,焊接不良。

如果以上两点均无问题,可通知供应商拿物料分析解决问题。

晶振电路的生产研发条件质量保证命名规则恒温晶体振荡器(OCXOs)OX253B-H-MR-V-10M OX362D-H-MR-V-10MOX20系列10~40SC±0.01~0.20.2S/T/HOX30x系列10~120SC±0.005~0.20.5S/T/H-140/-14556●●9●1215订购表7●OX14B-T-HU-V-10MOX12A-T-HT-V-40M温度补偿晶体振荡器(TCXOs)TX12/TX14/TX15系列10~120±0.5~512/5/3.3S/T/H/CTXG36B-S-KW-R@300M1922命名规则●-55~+85CTX7A-C-GU-V@10M TX12B-T-JW-N@20M注:ppm=10,120MHz以上为倍频输出,可选定制产品;10MHz以下为分频输出;产品概览8●型号频率范围f(MHz)频率温度稳定度压控频率范围工作电压V输出选择*电压控制晶体振荡器(VCXOs)ppmVX12/VX14/VXM14(SMD)ppm压控线性注:ppm=10, 除VXM15系列外,频率>35MHz压控频率范围为±30ppm; 需宽压控频率范围可选倍频输出。

*:S:Sinewave; LC:L VCMOS; LP:LVPECL。

VXM15B-T-HQ-A@100M页码24命名规则●VX12/VX14/VXM14集成晶体振荡器目录封装外形尺寸图35(TMs )±ppmppm时钟模块概述VTM18B-T-HT-001页码TM18系列±4.62/2CMOS5/3.328±0.370.008~32.768●27集成晶体振荡器目录(XTALs )封装页码29命名规则●±5ppm1、完善的晶体谐振器生产线2 我们拥有1000m 资上千万元完整的晶体谐振器生产线,其主要设备从国外引进,可生产高Q、低老化冷压焊和电阻焊(抽真空)SC、AT切晶体。

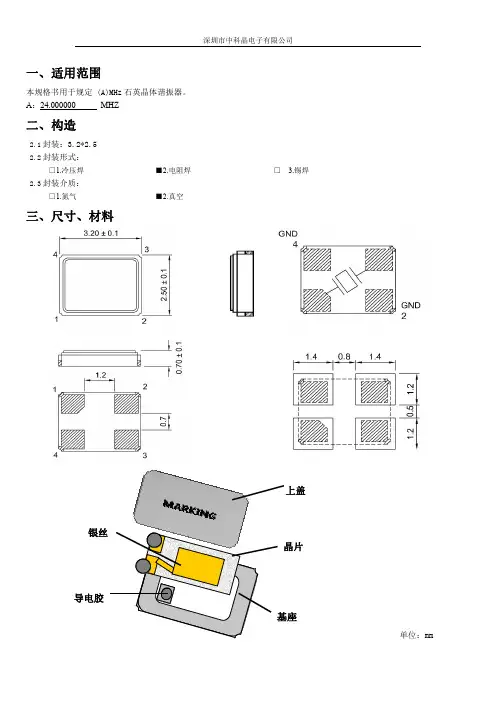

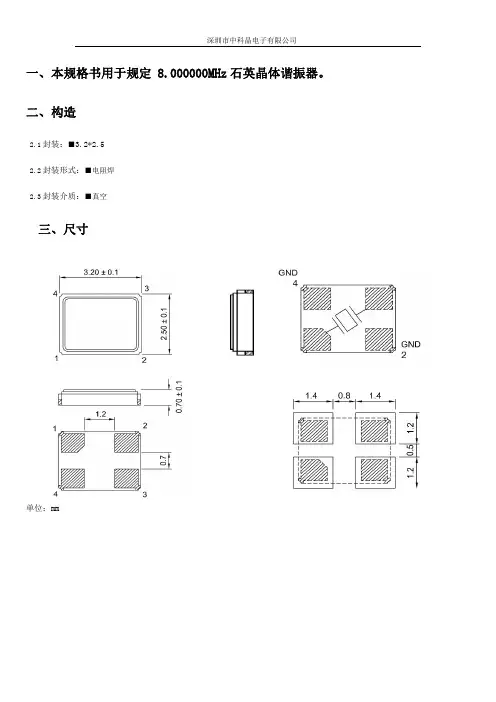

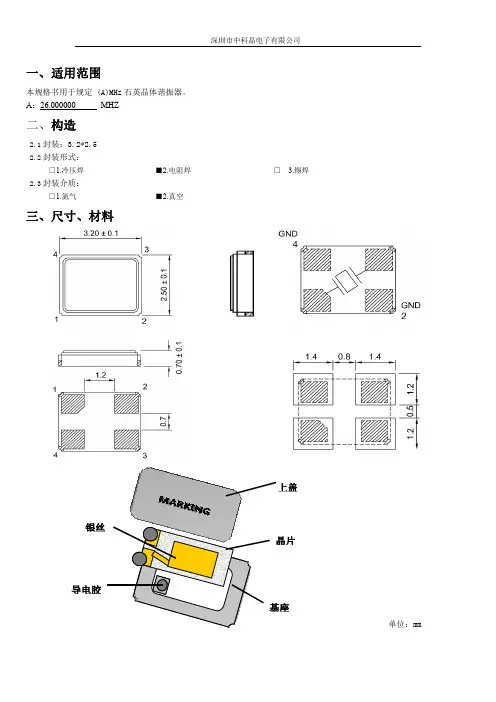

深圳市中科晶电子有限公司一、本规格书用于规定8.000000MHz石英晶体谐振器。

二、构造2.1封装:■3.2*2.52.2封装形式:■电阻焊2.3封装介质:■真空三、尺寸单位:mm四、晶体技术参数指标1.频率:8.000000MHz2.型号:32253.振荡模式:Fundamental(AT)4.频率频差:±20ppm at25℃±3℃5.温度频差:±30ppm温度频差测试的基准温度是:25±2℃6.工作温度范围:-20℃~+70℃7.储存温度范围:-30℃~+85℃8.负载(CL):20.0pF9.激励功率:100uW/Max10.静电容: 2.0pF MAX11.等效电阻:80ΩMax.12.绝缘阻抗:500MΩmin/DC100V13.年老化率:±3ppm/年14.包装方式:卷包3000PCS/Reel15.备注五、可靠性试验六、包装方式6.1带子尺寸(unit:mm )MarkingMarkingA B C D E F G H J K t 2.73.48.03.51.754.02.04.01.551.40.256.2卷盘尺寸(unit:mm )7.注意本产品不能折弯使用,在电路板安装时使用过大的机械压力可能造成产品损坏,同时本规格书只规定了部件本身的品质,应用于您的产品时请确认图纸该产品是否适用。

M N P Q R S U 178.060.211.58.02.511.013.0。

晶振电路的理论与应用计算WTD standardization office【WTD 5AB- WTDK 08- WTD 2C】晶振电路的理论与应用计算图1:典型的Pierce皮尔斯石英晶体振荡电路图2:振荡电路图3:石英晶体等效电路图4:泛音石英晶体振荡电路图5:DIP封装的晶振(石英晶体谐振器)图6:SMD封装的晶振(石英晶体谐振器)图7:SMD封装的晶振图8:SMD封装的钟振(多了下方的振荡电路、IC)常用的“贴片晶振-40MHz-15pF-15ppm-3225-亚陶”,可以从规格书上看到如下参数:1、说明:A、大部分的中低频、要求不是特别高的振荡电路都采用了图1的形式,也许增加了多级反相器(可视为AB类放大器)作为Buffer,也就是说,我们用的大部分的芯片内部就集成了图2振荡电路的”A”部分,如BCM5357、RT5350、IP175D、RT8169等;实际上,我们使用的大部分LVTTL/LVCOMS输出的钟振内部就是这种电路;在已停产的W54R产品上,CPU没有集成振荡电路,为Costdown,我们就直接使用这种电路替代钟振;在BCM6332 方案的ADSL产品上,选用了64Mhz 3次泛音石英晶体振荡电路,与图4有些类似;RF为反馈电阻,RS为串联的隔离电阻,C1、C2为外部的负载电容;B、如图2所示,振荡电路可视为由两大部分组成:放大器A,有电压增益a、相移α;反馈网络F,有传递函数f、相移β;振荡电路工作条件:|f|∗|a|∗exp[j(α+β)]≥1增益:|f|∗|a|≥1相位:(α+β)=2∗n∗π即闭环增益≥1,相移n∗360°;在振荡电路中,石英晶体谐振器与外部匹配元件组成反馈网络,其压电效应起到电子<->机械的耦合作用,对振荡电路起到很好的稳频作用;C、如图3所示,晶振的等效电路中:C0称为”分路/静态”电容(Shunt Capacitance),由晶体片上的电极、封装产生的寄生电容,通常约5pF;L称为动态电感,是由晶体机械振动产生的”动态臂”;通常为mH级,如100mH;C称为动态电容,是由晶体机械振动产生的”动态臂”;通常为fF级,如;R称为动态/ ESR电阻,是由晶体机械振动产生的”动态臂”;通常为?级,如10?;R为消耗性的,且R越小越易起振,但制造因难;2、Frequency Tolerance频率误差:∗1000000 (ppm)(E1)频率误差:?f=fm−fsfs也称为调整频差,10ppm表示百万分之十的误差;在室温条件下晶振实测工作频率fm与标称频率fs的相对误差;∗1000000 (ppm)(E2)稳定性:?ft=ft−fsfs也称为温率频差,指在一定温度范围内晶振的工作频率与其在室温25℃下标称频率的相对误差;3、串联谐振与并联谐振:图9:晶振的电抗频谱线因为R较小可以忽略,所以:晶振阻抗:Z =j ω∗ω2∗L∗C−1(C0+C )−(ω2∗L∗C∗C0) (E3)当晶振工作在串联谐振模式时,表现为纯阻性,Z ->0,XL=XC :串联谐振频率:fs =2π∗L∗C (E4)当晶振工作在并联谐振模式时,表现为感性,Z ->∞,晶振制造商会为其指定负载电容CL :并联谐振频率:fa =2π∗√L∗CL+C0≈fs ∗√1+c c0+CL (E5)因为CL >C0?C ,所以:fa ≈fs ;常见的的振荡电路中,大多工作在并联谐振模式下,在图9电抗线中fs 到fa 的斜线区域内,通过调整晶振的负载,都可以很好地工作,输出频率在fs 到fa 两者之间;4、品质因素:Q =12∗π∗fs∗R∗C (E6)Q 值越高,晶振频率的稳定度就越高5、负载电容CL : 制造商设计时预设的与晶振最佳匹配的负载电容值,通常在15~30pF :负载电容: CL =C1∗C2C1+C2+Cs +Cic (E6) PCB 漂移电容: Cs =a∗b∗εd (E7)a:PCB 走线宽度,b:PCB 走线长度,ε:单位PCB 面积的电容值,d:走线与GND 的间距;最可计算出PCB 走线、PAD 所产生的分布电容难以忽视,因而PCB LAYOUT 时需密切关注; IC 内部及封装电容:Cic =Cin∗CoutCin+Cout +Cfb (E8)Cin:IC 输入电容,Cout:IC 输出电容,Cfb:IC 晶圆电容;负载输出频率:fL =fs ∗(1+C2∗(C0+CL )) (E9) 牵引灵敏度:S =−C 2∗(C0+CL) (E10)表示负载电容对频率的调节能力;图10:负载对频率的牵引;反馈因子: Cf =C1C2 (E11)工作在线性区的反相器(放大器)导入180°或更高一些的相移,而C1、C2构成的电容分压器,在C1=C2的情况下,引入另外的180°相移,从而满足振荡条件;Cf 值偏大时,环路增益大,易于起振,但过大时,振荡电路稳定性会变差;6、反馈电阻Rf 设置反相器(CMOS 放大器)的输入阻抗Ri ,为满足振荡条件,放大器的开环增益必须>1;晶振的并联谐振电阻Rp则由负载电容CL设置;而Rp必须与Ri相匹配,因而有:输入阻抗:Ri=RFa(E12)并联谐振电阻:Rp=1R∗ω∗(C0∗CL)(E13)反馈电阻:Rf=Rp∗a=aR∗ω2∗(C0∗CL)2(E14)实际应用中,为获得高输入阻抗Ri、晶振电路良好地驱动,反馈电阻Rf通常≥1M?,且大多集成在IC中;7、Rs串联的隔离电阻反相器(放大器)额外的相移:α1=fs∗Delay∗360°(E15)Delay是反相器的传输延时,频率越高、延时越大,180°以外的相移越大,需要调节C1、C2、Rs来补偿,以维护振荡电路的稳定性;Rs是放大输出与晶振之间串联的隔离电阻,除串联隔离,其作用大致有:放大输出的源终端匹配电阻、与Rs与C2组成低通滤波,抑制反射、高频谐波阻尼,防EMI;Rs与C2形成分压器,拉低输出电平、降低放大器增益,提高稳定性;但也除低振荡频率、提升相移;限制放大器输出电流,设定晶振DL值,防止晶振过驱动,保证可靠性与寿命; Rs还会影响输出时钟的占空比;Rs≈XC2≈12∗π∗fs∗C2(E16)通常稍小于计算式,大约在1K以内,或者在一些场合不需要,注意! Rs≈XC2将导置50%的压降,因而放大器必须能提供2或以上的增益;8、驱动电平DL,指晶振工作时消耗的功率,通常供应商会在晶振规格书中提供这一个参数,实际应用中需确保在这一限值之内:图11:使用电流探头测量晶振驱动电流I(RMS值)驱动电平(uW):P=I2∗R(E17)受仪器设备限制,可以另一种方法计算:驱动电平(uW):P=U 2R∗(1+C0CL )2(E18)R为晶振动态电阻,I为实测的驱动电流,U为晶振上实测的压降;9、起振条件的测算与分析:图12:振荡电路等效参考模型振荡电路环路增益等于放大器跨导Gm、谐振电路等效并联电阻RL、反馈系数Cf之积,通常Cf被设置为1;增益:|Gain|=|ViVin |=|ViVout|∗|VoutVin|=|G1|∗|G2|=|gm∗RL|≥1(E19)RL=116∗π2∗1fs2∗(C0+CL)2∗R(E20)因此如果推算出的增益大于1并有一定余量,则表示能正常起振;另一种方法为开环测量反相器(集成在IC中放大器)增益G2,看是否能足够的余量来保证|G1|∗|G2|≥1;大致的测量方式为:移除晶振及外部元件,使用信号源输出合适幅值的fs时钟到IC的XTAL_in,使用双通道示波器同时实际测量IC的XTAL_out、XTAL_in信号幅值电压,两者比值即为开环增益G2,因为晶振及其匹配电路的G1为负增益,G2足够高即能正常起振;10、振荡电路的稳定性测算与分析——负性阻抗测量:负性阻抗简单来讲,是指从晶振的两个Pin脚向振荡电路看,所得到振荡电路在谐振频率时的阻抗特性值(注意:不是晶振、而是振而是振荡电路-更多是放大器的参数!);振荡电路必需提供足够的放大增益来补偿晶振在谐振时的机械能损推出;从共振子的角度而言,就是在振荡电路上的“负性阻抗”。

精心整理晶振电路的理论与应用计算图1:典型的Pierce皮尔斯石英晶体振荡电路图2:振荡电路图3:石英晶体等效电路图4:泛音石英晶体振荡电路图5:DIP封装的晶振(石英晶体谐振器)图6:SMD封装的晶振(石英晶体谐振器)图7:SMD封装的晶振图8:SMD封装的钟振(多了下方的振荡电路、IC)常用的“贴片晶振-40MHz-15pF-15ppm-3225-亚陶”,可以从规格书上看到如下参数:1、说明:A、大部分的中低频、要求不是特别高的振荡电路都采用了图1的形式,也许增加了多级反相器(可视为AB 类放大器)作为Buffer,也就是说,我们用的大部分的芯片内部就集成了图2振荡电路的”A”部分,如BCM5357、RT5350、IP175D、RT8169等;实际上,我们使用的大部分LVTTL/LVCOMS输出的钟振内部就是这种电路;在已停产的W54R产品上,CPU没有集成振荡电路,为Costdown,我们就直接使用这种电路替代钟振;在BCM6332方案的ADSL产品上,选用了64Mhz3次泛音石英晶体振荡电路,与图4有些类似;RF为反馈电阻,RS为串联的隔离电阻,C1、C2为外部的负载电容;B、如图2所示,振荡电路可视为由两大部分组成:放大器A,有电压增益a、相移α;反馈网络F,有传递函数f、相移β;振荡电路工作条件:增益:相位:即闭环增益,相移;在振荡电路中,石英晶体谐振器与外部匹配元件组成反馈网络,其压电效应起到电子<->机械的耦合作用,对振荡电路起到很好的稳频作用;C、如图3所示,晶振的等效电路中:C0称为”分路/静态”电容(ShuntCapacitance),由晶体片上的电极、封装产生的寄生电容,通常约5pF;L称为动态电感,是由晶体机械振动产生的”动态臂”;通常为mH级,如100mH;C称为动态电容,是由晶体机械振动产生的”动态臂”;通常为fF级,如0.01pF;R称为动态/ESR电阻,是由晶体机械振动产生的”动态臂”;通常为?级,如10?;R为消耗性的,且R越小越易起振,但制造因难;2、FrequencyTolerance频率误差:频率误差:(E1)也称为调整频差,10ppm表示百万分之十的误差;在室温条件下晶振实测工作频率fm与标称频率fs的相对误差;稳定性:(E2)也称为温率频差,指在一定温度范围内晶振的工作频率与其在室温下标称频率的相对误差;3、串联谐振与并联谐振:图9:晶振的电抗频谱线因为R较小可以忽略,所以:晶振阻抗:(E3)当晶振工作在串联谐振模式时,表现为纯阻性,Z->0,XL=XC:串联谐振频率:(E4)当晶振工作在并联谐振模式时,表现为感性,Z->∞,晶振制造商会为其指定负载电容CL:并联谐振频率:(E5)因为,所以:;常见的的振荡电路中,大多工作在并联谐振模式下,在图9电抗线中fs到fa的斜线区域内,通过调整晶振的负载,都可以很好地工作,输出频率在fs到fa两者之间;4、品质因素:(E6)Q值越高,晶振频率的稳定度就越高5、负载电容CL:制造商设计时预设的与晶振最佳匹配的负载电容值,通常在15~30pF:负载电容:(E6)PCB漂移电容:(E7)a:PCB走线宽度,b:PCB走线长度,ε:单位PCB面积的电容值,d:走线与GND的间距;最可计算出PCB走线、PAD所产生的分布电容难以忽视,因而PCBLAYOUT时需密切关注;IC内部及封装电容:(E8)Cin:IC输入电容,Cout:IC输出电容,Cfb:IC晶圆电容;负载输出频率:(E9)牵引灵敏度:(E10)表示负载电容对频率的调节能力;图10:负载对频率的牵引;反馈因子:(E11)工作在线性区的反相器(放大器)导入或更高一些的相移,而C1、C2构成的电容分压器,在C1=C2的情况下,引入另外的相移,从而满足振荡条件;Cf值偏大时,环路增益大,易于起振,但过大时,振荡电路稳定性会变差;6、反馈电阻Rf设置反相器(CMOS放大器)的输入阻抗Ri,为满足振荡条件,放大器的开环增益必须>1;晶振的并联谐振电阻Rp则由负载电容CL设置;而Rp必须与Ri相匹配,因而有:输入阻抗:(E12)并联谐振电阻:(E13)反馈电阻:(E14)实际应用中,为获得高输入阻抗Ri、晶振电路良好地驱动,反馈电阻Rf通常≥1M?,且大多集成在IC中;7、Rs串联的隔离电阻反相器(放大器)额外的相移:(E15)Delay是反相器的传输延时,频率越高、延时越大,以外的相移越大,需要调节C1、C2、Rs来补偿,以维护振荡电路的稳定性;Rs是放大输出与晶振之间串联的隔离电阻,除串联隔离,其作用大致有:放大输出的源终端匹配电阻、与Rs与C2组成低通滤波,抑制反射、高频谐波阻尼,防EMI;Rs与C2形成分压器,拉低输出电平、降低放大器增益,提高稳定性;但也除低振荡频率、提升相移;限制放大器输出电流,设定晶振DL值,防止晶振过驱动,保证可靠性与寿命;Rs还会影响输出时钟的占空比;(E16)通常稍小于计算式,大约在1K以内,或者在一些场合不需要,注意!将导置50%的压降,因而放大器必须能提供2或以上的增益;8、驱动电平DL,指晶振工作时消耗的功率,通常供应商会在晶振规格书中提供这一个参数,实际应用中需确保在这一限值之内:图11:使用电流探头测量晶振驱动电流I(RMS值)驱动电平(uW):(E17)受仪器设备限制,可以另一种方法计算:驱动电平(uW):(E18)R为晶振动态电阻,I为实测的驱动电流,U为晶振上实测的压降;9、起振条件的测算与分析:图12:振荡电路等效参考模型振荡电路环路增益等于放大器跨导Gm、谐振电路等效并联电阻RL、反馈系数Cf之积,通常Cf被设置为1;增益:(E19)(E20)因此如果推算出的增益大于1并有一定余量,则表示能正常起振;另一种方法为开环测量反相器(集成在IC中放大器)增益G2,看是否能足够的余量来保证;大致的测量方式为:移除晶振及外部元件,使用信号源输出合适幅值的fs时钟到IC的XTAL_in,使用双通道示波器同时实际测量IC的XTAL_out、XTAL_in信号幅值电压,两者比值即为开环增益G2,因为晶振及其匹配电路的G1为负增益,G2足够高即能正常起振;10、振荡电路的稳定性测算与分析——负性阻抗测量:负性阻抗简单来讲,是指从晶振的两个Pin脚向振荡电路看,所得到振荡电路在谐振频率时的阻抗特性值(注意:不是晶振、而是振而是振荡电路-更多是放大器的参数!);振荡电路必需提供足够的放大增益来补偿晶振在谐振时的机械能损推出;从共振子的角度而言,就是在振荡电路上的“负性阻抗”。

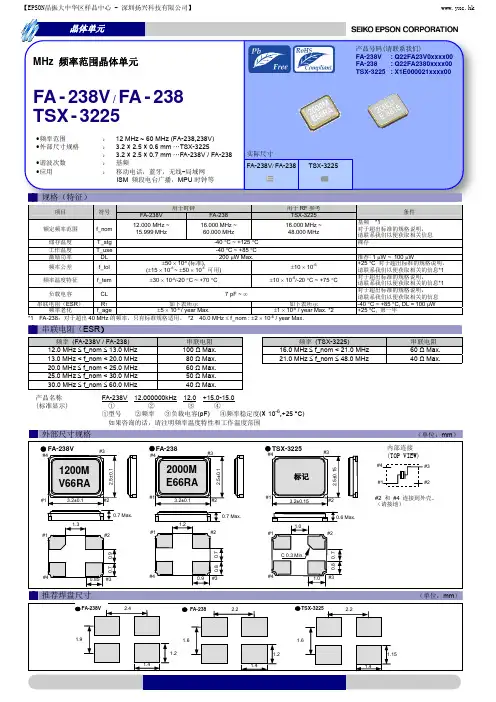

ItemModel Need to specifyMode 振動模式Fund.Fund.Fund.Fund.Series Resistance 諧振電阻100ohmMax.80ohmMax.60ohmMax.40ohmMax. SERIES RESISTANCE 諧振電阻Freq. Range 頻率範圍12~16MHz 16~20MHz 20~24MHz 24~50MHz Aging[first year] 第一年老化率±5ppm Max.25±3℃Insulation Resistance 絕緣阻抗500Mohm Min.DC100V±15V Load Capacitance 負載電容20pF Need to specify Shunt Capacitance 靜態電容7.0pF Max.Drive Level 激勵電平10μw Typical Storage Temp. Range 保存溫度範圍–40~+85℃Need to specify Series Resistance 諧振電阻Refer to the table as below at 25℃Freq. Tol. Over Temp. 溫度頻差±30ppm Need to specify Operating Temp. Range 工作溫度範圍–40~+85℃Need to specify 適合於低功耗的便攜設備For a clock source in digital equipments 適用於數碼設備的所 有時鐘源STANDARD SPECIFICATIONS 標準規格T3225Conditions Frequency Tolerance 調整頻差±10ppm at 25℃Need to specify Frequency Range 頻率範圍12.000MHz ABEL ELECTRONSURFACE MOUNTABLE CRYSTAL UNITS (SMD Package) 贴片石英晶體諧振器 海诺威電子有限公司RoHS Compliant Standard SMD-3225Features 特性Frequency Range:12-50MHz 頻率範圍:12-50MHzSuited for portable devices with low current consumption。