单片机P0~P3口结构与时序

- 格式:docx

- 大小:28.40 KB

- 文档页数:5

51单片机I/O引脚IO口工作原理一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q 及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

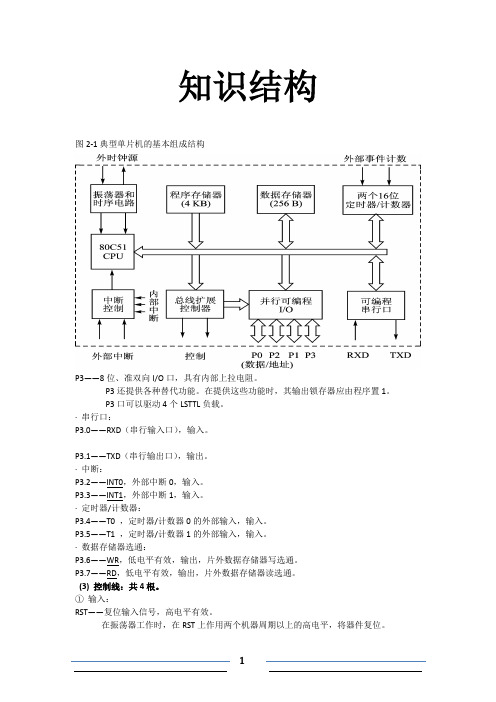

知识结构图2-1典型单片机的基本组成结构P3——8位、准双向I/O口,具有内部上拉电阻。

P3还提供各种替代功能。

在提供这些功能时,其输出锁存器应由程序置1。

P3口可以驱动4个LSTTL负载。

·串行口:P3.0——RXD(串行输入口),输入。

P3.1——TXD(串行输出口),输出。

·中断:P3.2——INT0,外部中断0,输入。

P3.3——INT1,外部中断1,输入。

·定时器/计数器:P3.4——T0 ,定时器/计数器0的外部输入,输入。

P3.5——T1 ,定时器/计数器1的外部输入,输入。

·数据存储器选通:P3.6——WR,低电平有效,输出,片外数据存储器写选通。

P3.7——RD,低电平有效,输出,片外数据存储器读选通。

(3) 控制线:共4根。

①输入:RST——复位输入信号,高电平有效。

在振荡器工作时,在RST上作用两个机器周期以上的高电平,将器件复位。

EA/V PP——片外程序存储器访问允许信号,低电平有效。

在编程时,其上施加21 V或12 V 的编程电压。

②输入、输出:ALE/PROG——地址锁存允许信号,输出。

用做片外存储器访问时,低字节地址锁存。

ALE以1/6的振荡频率稳定速率输出,可用做对外输出的时钟或用于定时。

在EPROM编程期间,作输入。

输入编程脉冲(PROG)。

1ALE 可以驱动8个LSTTL负载。

③输出控制线:PSEN——片外程序存储器选通信号,低电平有效。

在从片外程序存储器取指期间,在每个机器周期中,当PSEN有效时,程序存储器的内容被送上P0口(数据总线)。

PSEN可以驱动8个LSTTL负载。

2) 数据指针DPTR数据指针是80C51中一个功能比较特殊的寄存器。

从结构上说,DPTR是一个16位的特殊功能寄存器,主要功能是作为片外数据存储器寻址用的地址寄存器(间接寻址),故称为数据指针。

访问片外数据存储器的指令为:MOVX A,@DPTR 读MOVX @DPTR,A 写此时,DPTR的输出,即片外数据存储器的地址,与P0、P2口之间的关系如图2--5所示。

第1章习题答案1.什么是单片机?答:将中央处理器(Central Processing Unit,CPU)、随机存储器、只读存储器、中断系统、定时器/计数器以及I/O接口电路等微型计算机的主要部件集成在一块芯片上,使其具有计算机的基本功能,就叫做单片微型计算机(Single Chip Micro Computer,SCMC),简称单片机。

由于单片机的指令功能是按照工业控制的要求设计,所以单片机又称为微控制器(Micro Controller Unit,MCU)。

2.单片机有哪些特点?答: (1)单片机的存储器ROM和RAM是严格区分的。

ROM称为程序存储器,只存放程序、固定常数及数据表格。

RAM则为数据存储器,用作工作区及存放用户数据。

(2)采用面向控制的指令系统。

(3)单片机的I/O引脚通常是多功能的。

(4)单片机的外部扩展能力强。

(5)单片机体积小,成本低,运用灵活,易于产品化。

(6)面向控制,能有针对性地解决从简单到复杂的各类控制任务,因而能获得最佳的性能价格比。

(7)抗干扰能力强,适用温度范围宽。

(8)可以方便地实现多机和分布式控制,使整个控制系统的效率和可靠性大为提高。

3.单片机的应用有哪些?答: (1)工业控制。

单片机可以构成各种工业控制系统、数据采集系统等。

如数控机床、自动生产线控制、电机控制、测控系统等。

(2)仪器仪表。

如智能仪表、医疗器械、数字示波器等。

(3)计算机外部设备与智能接口。

如图形终端机、传真机、复印机、打印机、绘图仪、磁盘/磁带机、智能终端机等。

(4)商用产品。

如自动售货机、电子收款机、电子秤等。

(5)家用电器。

如微波炉、电视机、空调、洗衣机、录像机、音响设备等。

(6)消费类电子产品。

(7)通讯设备和网络设备。

(8)儿童智能玩具。

(9)汽车、建筑机械、飞机等大型机械设备。

(10)智能楼宇设备。

(11)交通控制设备。

4.常见的单片机有哪些类型?答: 1.AVR单片机;2.Motorola单片机;3.MicroChip单片机;4.Scenix单片机;5.EPSON单片机;7.GMS90单片机;8.华邦单片机9.Zilog单片机;10.NS单片机;11.AX1001单片机第2章习题答案1.MCS-51单片机内部包含哪些主要逻辑功能部件?答:(1)1个8位的微处理器CPU。

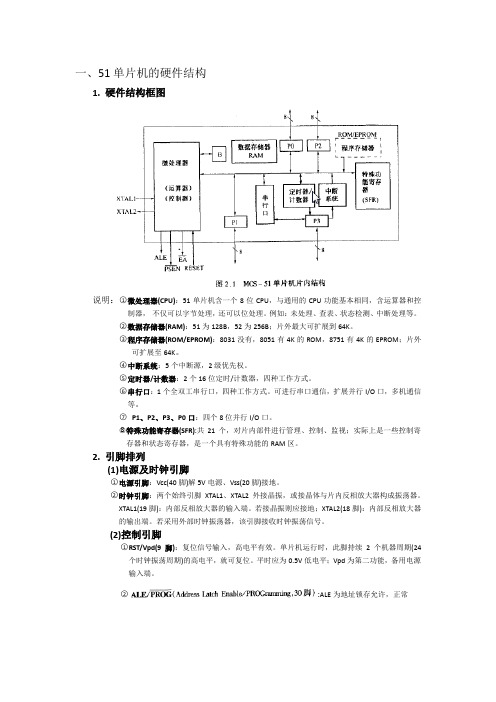

一、51单片机的硬件结构1. 硬件结构框图说明:○1微处理器(CPU):51单片机含一个8位CPU,与通用的CPU功能基本相同,含运算器和控制器,不仅可以字节处理,还可以位处理。

例如:未处理、查表、状态检测、中断处理等。

○2数据存储器(RAM):51为128B,52为256B;片外最大可扩展到64K。

○3程序存储器(ROM/EPROM):8031没有,8051有4K的ROM,8751有4K的EPROM;片外可扩展至64K。

○4中断系统:5个中断源,2级优先权。

○5定时器/计数器:2个16位定时/计数器,四种工作方式。

○6串行口:1个全双工串行口,四种工作方式。

可进行串口通信,扩展并行I/O口,多机通信等。

○7P1、P2、P3、P0口:四个8位并行I/O口。

○8特殊功能寄存器(SFR):共21个,对片内部件进行管理、控制、监视;实际上是一些控制寄存器和状态寄存器,是一个具有特殊功能的RAM区。

2. 引脚排列(1)电源及时钟引脚○1电源引脚:Vcc(40脚)解5V电源、Vss(20脚)接地。

○2时钟引脚:两个始终引脚XTAL1、XTAL2外接晶振,或接晶体与片内反相放大器构成振荡器。

XTAL1(19脚):内部反相放大器的输入端。

若接晶振则应接地;XTAL2(18脚):内部反相放大器的输出端。

若采用外部时钟振荡器,该引脚接收时钟振荡信号。

(2)控制引脚○1RST/Vpd(9脚):复位信号输入,高电平有效。

单片机运行时,此脚持续2个机器周期(24个时钟振荡周期)的高电平,就可复位。

平时应为0.5V低电平;Vpd为第二功能,备用电源输入端。

○2:ALE为地址锁存允许,正常工作时,ALE不断输出正脉冲信号。

当访问外部存储器时,ALE输出信号的负跳变沿用作低8位地址的锁存信号;PROG’为编程脉冲输入端。

○3PSEN’(Program Strobe Enable,29脚):程序存储器允许输出控制端。

低电平是外部程序存储器选通。

单片机P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X 引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

51单片机各针脚介绍51单片机是一款广泛应用于嵌入式系统中的微控制器,它在电子行业中具有重要的地位。

了解51单片机的各个针脚和其功能对于学习和应用它来说至关重要。

本文将为读者介绍51单片机的各个针脚以及它们的功能。

1. VCC和GND:VCC代表供电正极,GND代表接地。

这两个针脚是最基本的供电和接地连接,使用者需要将这两个引脚连接到电源,以提供电压和地线。

2. P0.0 - P0.7:P0口是51单片机最常用的8位通用I/O口之一。

每个引脚可以被配置为输入或输出,用于连接和控制外部设备。

3. P1.0 - P1.7:P1口也是一个8位通用I/O口,具有与P0口相同的功能。

P1口的特点是它具备上拉电阻功能,可以用于外部开关和按钮的输入控制。

4. P2.0 - P2.7:P2口也是一个8位通用I/O口,同样可以作为输入或输出引脚。

与P1口类似,P2口也具备上拉电阻功能。

5. P3.0 - P3.7:P3口是最后一个8位通用I/O口,同样可用作输入或输出引脚。

与P2口类似,P3口具备上拉电阻功能。

6. RST:RST是复位控制引脚,用于将51单片机重启至复位状态。

当对RST引脚施加低电平脉冲时,单片机将会重新启动,并执行初始化操作。

7. EA/VPP:EA/VPP引脚具有两个不同的功能。

在系统中,EA引脚必须连接到GND,以选择外部程序存储器;VPP引脚在烧录代码时使用,通常连接到12V电压。

8. ALE/PROG:ALE/PROG引脚也有两种功能,ALE用于地址锁存器的时钟输入,PROG用于编程电平切换。

在应用中,ALE通常用于与外部设备进行时序协调。

9. PSEN:PSEN引脚用于外部程序存储器的读取操作。

当进行指令获取或通信时,PSEN引脚连接到程序存储器并发送读取控制信号。

10. XTAL1和XTAL2:这两个引脚用于外部晶振或陶瓷谐振器的连接。

XTAL1接收晶振信号输入,XTAL2输出晶振信号。

80C51单片机原理RAM地址寄存器 RAM 128B 程序地址寄存器P0驱动器 P2锁存器 P2驱动器P1锁存器 暂存器2 B 寄存器 4KB ROM暂存器1ACC SP P0锁存器 PC PC 增1 缓冲器 P3锁存器 OSC中断、串行口及定时器PSW ALU DPTRP1驱动器 P3驱动器XTAL1XTAL2 P0.0~P0.7 P2.0~P2.7 P3.0~P3.7 P1.0~P1.7 RST ALEV CCV SS定时控制 指令译码器 指令寄存器 PSEN EA表2-1 P3口各引脚与第二功能表PSW 的各位定义见表80C51 P0~P3接口功能简见大多数口线都有双重功能,介绍如下: 1、P0口具有双重功能:(1) 作为通用I/O ,外接I/O 设备。

(2) 作为地址/数据总线。

在有片外扩展存储器的系统 中,低8位地址和数据由P0口分时传送。

PSW 位地址 PS W.7PSW .6PSW .5 PSW .4 PSW .3 PSW .2 PSW .1 PSW .0 位标志CY ACF0RS1RS0OVF1P2、P1口是唯一的单功能口:作为输入/输出口,P1口的每一位都可作为输入/输出口。

3、P2口具有双重功能:(1)作为输入/输出口。

(2)作为高8位地址总线。

在有片外扩展存储器的系统中,高8位地址由P2口传送。

4、P3口具有双重功能:(1)作第一功能使用时,其功能为输入/输出口。

(2)作第二功能使用时,每一位功能定义如表2.1所示。

80C51单片机的4个I/O口都是8位双向口,这些口在结构和特性上是基本相同的,但又各具特点,以下将分别介绍之。

图2-9 P0口某位的结构图2-10 P1口某位的结构图2-11 P2口某位的结构图2-12 P3口某位的结构P0~P3口使用时应注意事项1、如果80C51单片机内部程序存贮器ROM够用,不需要扩展外部存贮器和I/O接口,80C51的四个口均可作I/O口使用。

单片机IO口结构及上拉电阻

MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口

图1和图2为P0口和P2口其中一位的电路图。

由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图

图2 单片机P2口内部一位结构图

P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口

图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图

作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:

1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

三、P3口

P3口的电路如图4所示,P3口为准双向口,为适应引脚的第二功能的需要,增加了第二功能控制逻辑,在真正的应用电路中,第二功能显得更为重要。

由于第二功能信号有输入输出两种情况,我们分别加以说明。

图4 单片机P0口内部一位结构图

P3口的输入输出及P3口锁存器、中断、定时/计数器、串行口和特殊功能寄存器有关,P3口的第一功能和P1口一样可作为输入输出端口,同样具有字节操作和位操作两种方式,在位操作模式下,每一位均可定义为输入或输出。

我们着重讨论P3口的第二功能,P3口的第二功能各管脚定义如下:

·P3.0串行输入口(RXD)

·P3.1串行输出口(TXD)

·P3.2外中断0(INT0)

·P3.3外中断1(INT1)

·P3.4定时/计数器0的外部输入口(T0)

·P3.5定时/计数器1的外部输入口(T1)

·P3.6外部数据存储器写选通(WR)

·P3.7外部数据存储器读选通(RD)

对于第二功能为输出引脚,当作I/O口使用时,第二功能信号线应保持高电平,与非门开通,以维持从锁存器到输出口数据输出通路畅通无阻。

而当作第二功能口线使用时,该位的锁存器置高电平,使与非门对第二功能信号的输出是畅通的,从而实现第二功能信号的输出。

对于第二功能为输入的信号引脚,在口线上的输入通路增设了一个缓冲器,输入的第二功能信号即从这个缓冲器的输出端取得。

而作为I/O口线输入端时,取自三态缓冲器的输出端。

这样,不管是作为输入口使用还是第二功能信号输入,输出电路中的锁存器输出和第二功能输出信号线均应置“1”。

四、IO口工作原理

1. P0作为地址数据总线时,T1和T2是一起工作的,构成推挽结构。

高电平时,T1打开,T2截止;低电平时,T1截止,T2打开。

这种情况下不用外接上拉电阻.而且,当T1打开,T2截止,输出高电平的时候,因为内部电源直接通过T1输出到P0口线上,因此驱动能力(电流)可以很大,这就是为什么教科书上说可以"驱动8个TTL负载"的原因。

2. P0作为一般端口时,T1就永远的截止,T2根据输出数据0导通和1截止,导通时拉地,当然是输出低电平;要输出高电平,T2就截止,P0口就没有输出了,(注意,这种情况就是所谓的高阻浮空状态),如果加上外部上拉电阻,输出就变成了高电平1。

3. 其他端口P1、P2和P3,在内部直接将P1口中的T1换成了上拉电阻,所以不用外接,但内部上拉电阻太大,电流太小,有时因为电流不够,也会再并一个上拉电阻。

4. 在某个时刻,P0口上输出的是作为总线的地址数据信号还是作为普通I/O口的电平信号,是依靠多路开关MUX来切换的。

而MUX的切换,又是根据单片机指令来区分的。

当指令为外部存储器/IO口读/写时,比如MOVX A,@DPTR ,MUX是切换到地址/数据总线上;而当普通MOV传送指令操作P0口时,MUX是切换到内部总线上的。

5. P0、P1、P2、P3口用于输入时,需要写1使IO下拉的MOS管截止,以免MOS管导通将输入拉底为0,当一直用于输入时不用置1(先使用该IO输出,该IO锁存器里可能是0,再用该IO输入则会使MOS管导通),将IO写1后,该IO锁存器不会变了,所以再一直用于输入不用置1。

p0用于地址数据线时输入不用写1,因为MUX没和锁存器相连。

PS:

Because Ports 1, 2, and 3 have fixed internal pullups, they are sometimes called “quasi- bidirectional” ports.

因为端口1、2、3有固定的内部上拉,所以有时候他们被称为"准双向"口。

Port 0, on the other hand, is considered “true” bidirectional, because when configured as an input it floats.

端口0, 从另外一方面来说,就被认为是"真正的"双向,因为当它被设置为输入的时候是浮空(高阻态)的。

五、P0口上拉电阻选择

如果是驱动led,那么用1K左右的就行了。

如果希望亮度大一些,电阻可减小,最小不要小于200欧姆,否则电流太大;如果希望亮度小一些,电阻可增大,增加到多少呢,主要看亮度情况,以亮度合适为准,一般来说超过3K以上时,亮度就很弱了,但是对于超高亮度的LED,有时候电阻为10K时觉得亮度还能够用。

我通常就用1k的。

对于驱动光耦合器,如果是高电位有效,即耦合器输入端接端口和地之间,那么和LED的情况是一样的;如果是低电位有效,即耦合器输入端接端口和VCC之间,那么除了要串接一个1——4.7k之间的电阻以外,同时上拉电阻的阻

值就可以用的特别大,用100k~500K之间的都行,当然用10K的也可以,但是考虑到省电问题,没有必要用那么小的。

对于驱动晶体管,又分为PNP和NPN管两种情况:对于NPN,毫无疑问NPN管是高电平有效的,因此上拉电阻的阻值用2K~20K之间的,具体的大小还要看晶体管的集电极接的是什么负载,对于LED类负载,由于发管电流很小,因此上拉电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此上拉电阻的阻值最好不要大于4.7K,有时候甚至用2K的。

对于PNP管,毫无疑问PNP管是低电平有效的,因此上拉电阻的阻值用100K以上的就行了,且管子的基极必须串接一个1~10K的电阻,阻值的大小要看管子集电极的负载是什么,对于LED类负载,由于发光电流很小,因此基极串接的电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此基极电阻的阻值最好不要大于4.7K。

对于驱动TTL集成电路,上拉电阻的阻值要用1~10K之间的,有时候电阻太大的话是拉不起来的,因此用的阻值较小。

但是对于CMOS集成电路上拉电阻的阻值就可以用的很大,一般不小于20K,我通常用100K的,实际上对于CMOS 电路,上拉电阻的阻值用1M的也是可以的,但是要注意上拉电阻的阻值太大的时候,容易产生干扰,尤其是线路板的线条很长的时候,这种干扰更严重,这种情况下上拉电阻不宜过大,一般要小于100K,有时候甚至小于10K。

另外有说法是这样的:

不是每个单片机电路都要在P0口加上拉的。

当用P0口驱动LED或是数码管时,可以不接任何的上拉电阻。

一样可以使用,加了上拉反而会增加耗电。

有些资料说要加上拉电阻是为了保证以P0口做数据输出时保证数据的正确。

单片机的其他IO口非高既低。

有明显的状态。

但是,P0口因为没有内部上拉,所以P0口只可以输出低电平,而无法输出高电平。

这样,在与外部逻辑器件链接的时候,因为没有确切的状态,就会导致逻辑错误。

所以,P0口是否连接上拉电阻关键是看具体应用。