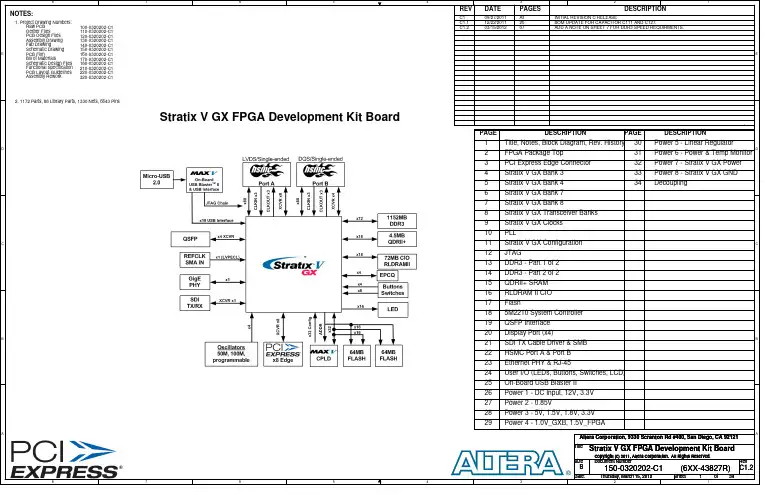

FPGA starter开发板原理图

- 格式:pdf

- 大小:47.23 KB

- 文档页数:1

FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

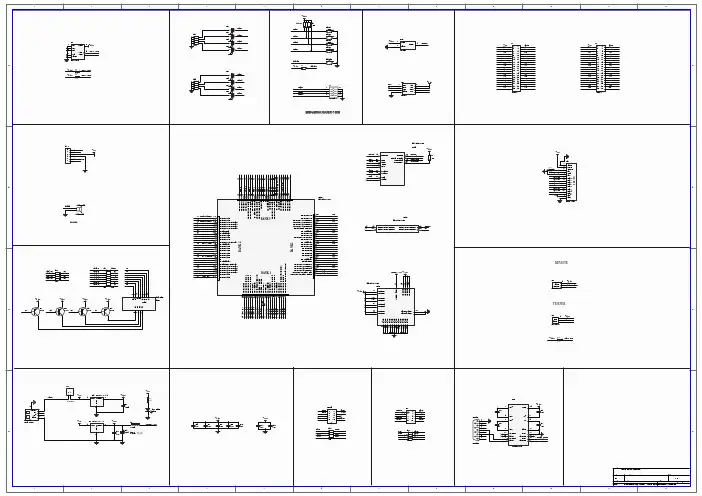

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

Fpga随便也可以通过jtag下载代码到片子里面运行。

Fpga下载到片子里面代码是存放在ram里,所以断电后这些代码马上就没有了。

EP1C3T144FPGAdevelopboardmanual(开发板原理图)FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led 可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

实验注意事项1.做实验前,先连接好下载线,然后才能接上电源。

2.做完实验后,先拨掉实验箱上的电源,然后才能拨下载线。

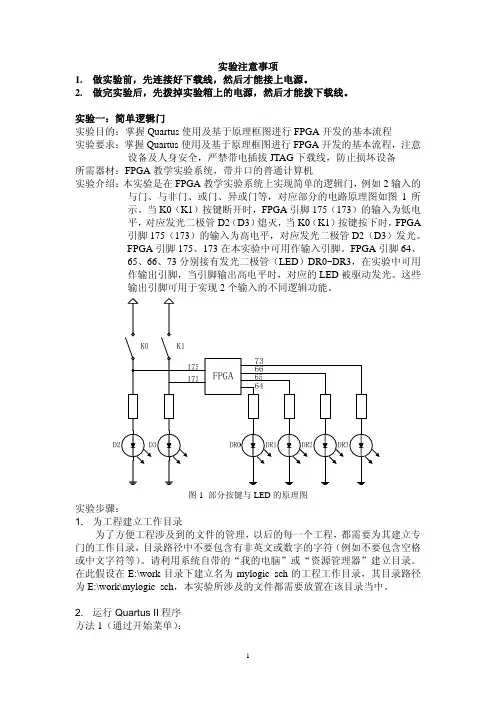

实验一:简单逻辑门实验目的:掌握Quartus使用及基于原理框图进行FPGA开发的基本流程实验要求:掌握Quartus使用及基于原理框图进行FPGA开发的基本流程,注意设备及人身安全,严禁带电插拔JTAG下载线,防止损坏设备所需器材:FPGA教学实验系统,带并口的普通计算机实验介绍:本实验是在FPGA教学实验系统上实现简单的逻辑门,例如2输入的与门、与非门、或门、异或门等,对应部分的电路原理图如图1所示。

当K0(K1)按键断开时,FPGA引脚175(173)的输入为低电平,对应发光二极管D2(D3)熄灭,当K0(K1)按键按下时,FPGA引脚175(173)的输入为高电平,对应发光二极管D2(D3)发光。

FPGA引脚175、173在本实验中可用作输入引脚。

FPGA引脚64、65、66、73分别接有发光二极管(LED)DR0~DR3,在实验中可用作输出引脚,当引脚输出高电平时,对应的LED被驱动发光。

这些输出引脚可用于实现2个输入的不同逻辑功能。

图1 部分按键与LED的原理图实验步骤:1. 为工程建立工作目录为了方便工程涉及到的文件的管理,以后的每一个工程,都需要为其建立专门的工作目录,目录路径中不要包含有非英文或数字的字符(例如不要包含空格或中文字符等)。

请利用系统自带的“我的电脑”或“资源管理器”建立目录。

在此假设在E:\work目录下建立名为mylogic_sch的工程工作目录,其目录路径为E:\work\mylogic_sch,本实验所涉及的文件都需要放置在该目录当中。

2. 运行Quartus II程序方法1(通过开始菜单):开始->程序(P)->Altera->Quartus II 7.2->Quartus II 7.2 (32-Bit)方法2(桌面快捷方式):双击桌面的快捷方式图标打开Quartus II后,其界面如图2所示。

2 Quartus II软件的使用、开发板的使用本章将通过3个完整的例子,一步一步的手把手的方式完成设计。

完成这3个设计,并得到正确的结果,将会快速、有效的掌握在Altera QuartusII软件环境下进行FPGA设计与开发的方法、流程,并熟悉开发板的使用。

2.1 原理图方式设计3-8译码器一、设计目的1、通过设计一个3-8译码器,掌握祝组合逻辑电路设计的方法。

2、初步了解QuartusII采用原理图方式进行设计的流程。

3、初步掌握FPGA开发的流程以及基本的设计方法、基本的仿真分析方法。

二、设计原理三、设计容四、设计步骤1、建立工程文件1)双击桌面上的Quartus II的图标运行此软件。

开始界面2)选择File下拉菜单中的New Project Wizard,新建一个工程。

如图所示。

新建工程向导3)点击图中的next进入工作目录。

新建工程对话框4)第一个输入框为工程目录输入框,用来指定工程存放路径,建议可根据自己需要更改路径,若直接使用默认路径,可能造成默认目录下存放多个工程文件影响自己的设计,本步骤结束后系统会有提示(当然你可不必理会,不会出现错误的)。

第二个输入框为工程名称输入框。

第三个输入框为顶层实体名称输入框,一般情况下保证工程名称与顶层实体名称相同。

设定完成后点击next。

指定工程路径、名称5)设计中需要包含的其它设计文件,在此对话框中不做任何修改,直接点击next。

工程所需其它文件对话框6)在弹出的对话框中进行器件的选择。

在Device Family框中选用Cyclone II,然后在Available device框中选择EP2C35F484C8,点击next进入下一步。

器件选择界面7)下面的对话框提示可以勾选其它的第三方EDA设计、仿真的工具,暂时不作任何选择,在对话框中按默认选项,点击next。

第三方EDA工具选择8)出现新建工程以前所有的设定信息后,点击finish完成新建工程的建立。