第六章时序逻辑电路-习题

- 格式:ppt

- 大小:611.00 KB

- 文档页数:61

触发器及时序电路(5-6章)练习题姓名:_______________________________ 学号:_________________________________一、是非题(请判断下列各题内容正确与否,分别用√及×填在题末( )内。

共计6小题,每小题1分)1. 凡是时序电路,一定有公共的时钟信号CP . ( )2.触发器的输出状态完全取决于同一时刻的输入状态。

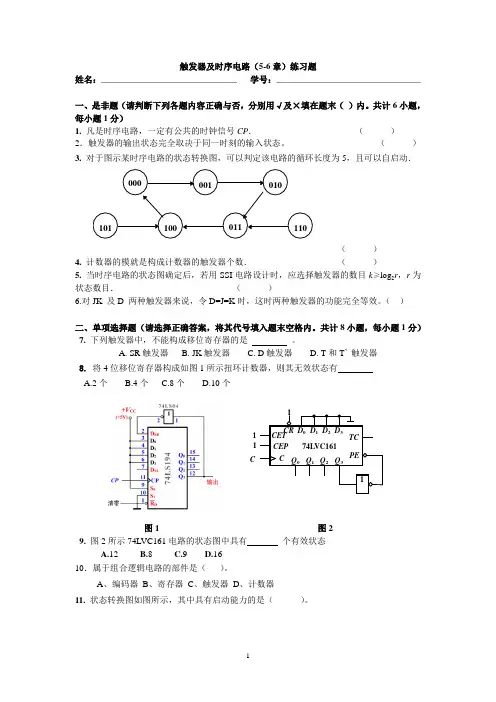

( ) 3. 对于图示某时序电路的状态转换图,可以判定该电路的循环长度为5,且可以自启动.( ) 4. 计数器的模就是构成计数器的触发器个数. ( )5. 当时序电路的状态图确定后,若用SSI 电路设计时,应选择触发器的数目k ≥log 2r ,r 为状态数目. ( )6.对JK 及D 两种触发器来说,令D=J=K 时,这时两种触发器的功能完全等效。

( )二、单项选择题(请选择正确答案,将其代号填入题末空格内。

共计8小题,每小题1分) 7. 下列触发器中,不能构成移位寄存器的是 。

A. SR 触发器B. JK 触发器C. D 触发器D. T 和T ’ 触发器 8. 将4位移位寄存器构成如图1所示扭环计数器,则其无效状态有 A.2个 B.4个 C.8个 D.10个图1 图29. 图2所示74LVC161电路的状态图中具有 个有效状态A.12B.8C.9D.16 10.属于组合逻辑电路的部件是( )。

A 、编码器B 、寄存器C 、触发器D 、计数器 11. 状态转换图如图所示,其中具有启动能力的是( )。

C P12.同步计数器和异步计数器比较,同步计数器的显著优点是( )A 、工作速度高B 、触发器利用率高C 、电路简单D 、不受时钟CP 控制。

13.某移位寄存器的时钟脉冲频率为100KHZ ,欲将存放在该寄存器中的数左移8位,完成该操作需要( )时间。

A 、10μSB 、80μSC 、100μSD 、800ms 14.某电视机水平-垂直扫描发生器需要一个分频器将31500HZ 的脉冲转换为60HZ 的脉冲,欲构成此分频器至少需要( )个触发器。

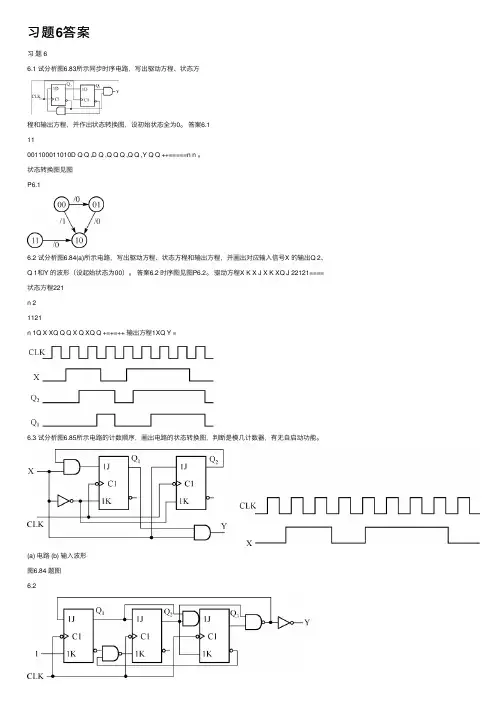

习题6答案习题 66.1 试分析图6.83所⽰同步时序电路,写出驱动⽅程、状态⽅程和输出⽅程,并作出状态转换图,设初始状态全为0。

答案6.111001100011010D Q Q ,D Q ,Q Q Q ,Q Q ,Y Q Q ++=====n n 。

状态转换图见图P6.16.2 试分析图6.84(a)所⽰电路,写出驱动⽅程、状态⽅程和输出⽅程,并画出对应输⼊信号X 的输出Q 2、Q 1和Y 的波形(设起始状态为00)。

答案6.2 时序图见图P6.2。

驱动⽅程X K X J X K XQ J 22121====状态⽅程221n 21121n 1Q X XQ Q Q X Q XQ Q +=+=++ 输出⽅程1XQ Y =6.3 试分析图6.85所⽰电路的计数顺序,画出电路的状态转换图,判断是模⼏计数器,有⽆⾃启动功能。

(a) 电路 (b) 输⼊波形图6.84 题图6.2图6.83 题图6.1第6章时序逻辑电路98图6.85 题图6.3答案 6.3 2323123312121231Q Q Y Q K Q Q J Q Q K Q J 1K Q Q J =======模七进制6.4 试分析图6.86时序电路的逻辑功能,写出电路的驱动⽅程、状态⽅程和输出⽅程,画出电路的状态转换图。

答案6.4 驱动⽅程1K Q Q J 1K 1J 1K Q J 321322131======状态⽅程3121n 3121n 2131n 1Q Q Q Q Q Q Q Q Q Q =↓?==+++6.5 试分析图6.87所⽰的时序电路,写出电路的驱动⽅程、状态⽅程和输出⽅程,画出电路的状态转换图,设初始状态全为0。

答案6.5 D 0 = A ⊕Q 0,T 1 = Q 0,Y = AQ 1,状态转换图见图P6.5。

图6.86 题图6.4 图6.87 题图6.56.6 试分析图6.88所⽰的时序电路,画出在时钟CLK 作⽤下,Q 1的输出波形。

一、填空题1. 基本RS触发器,当R、S都接高电平时,该触发器具有____ ___功能。

2.D 触发器的特性方程为___ ;J-K 触发器的特性方程为______。

3.T触发器的特性方程为。

4.仅具有“置0”、“置1”功能的触发器叫。

5.时钟有效边沿到来时,输出状态和输入信号相同的触发器叫____ _____。

6. 若D触发器的D端连在Q端上,经100 个脉冲作用后,其次态为0,则现态应为。

7.JK触发器J与K相接作为一个输入时相当于触发器。

8. 触发器有个稳定状态,它可以记录位二进制码,存储8 位二进制信息需要个触发器。

9.时序电路的次态输出不仅与即时输入有关,而且还与有关。

10. 时序逻辑电路一般由和两部分组成的。

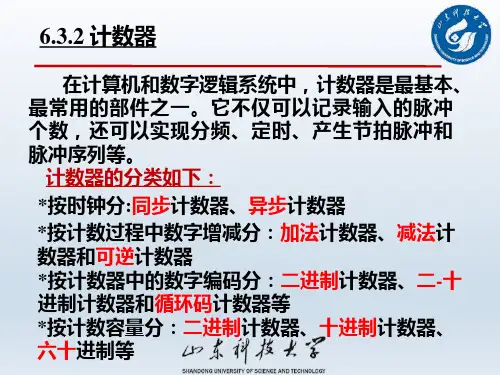

11. 计数器按内部各触发器的动作步调,可分为___ ____计数器和____ ___计数器。

12. 按进位体制的不同,计数器可分为计数器和计数器两类;按计数过程中数字增减趋势的不同,计数器可分为计数器、计数器和计数器。

13.要构成五进制计数器,至少需要级触发器。

14.设集成十进制(默认为8421码)加法计数器的初态为Q4Q3Q2Q1=1001,则经过5个CP脉冲以后计数器的状态为。

15.欲将某时钟频率为32MHz的CP变为16MHz的CP,需要二进制计数器个。

16. 在各种寄存器中,存放N位二进制数码需要个触发器。

17. 有一个移位寄存器,高位在左,低位在右,欲将存放在该移位寄存器中的二进制数乘上十进制数4,则需将该移位寄存器中的数移位,需要个移位脉冲。

18.某单稳态触发器在无外触发信号时输出为0态,在外加触发信号时,输出跳变为1态,因此其稳态为态,暂稳态为态。

19.单稳态触发器有___ _个稳定状态,多谐振荡器有_ ___个稳定状态。

20.单稳态触发器在外加触发信号作用下能够由状态翻转到状态。

21.集成单稳态触发器的暂稳维持时间取决于。

22. 多谐振荡器的振荡周期为T=tw1+tw2,其中tw1为正脉冲宽度,tw2为负脉冲宽度,则占空比应为_______。

时序电路习题一、填空1、寄存器存放数据的方式有____________和___________;取出数据的方式有____________和___________。

2、双拍工作方式的数码寄存器工作时需_____________。

3、按计数器中各触发器翻转时间可分为_________,________。

4、触发器有______个稳定状态,所以也称____________。

5、时序电路主要由________和 ________所构成,是一种具有_______功能的逻辑电路,常见的时序电路类型有___________和__________6、计数器的功能是_______________________,按计数时个触发器状态转换与计数脉冲是否同步,可分为__________和________。

_________计数器是各种计数器的基础。

7、4个触发器构成的8421BCD 码计数器,共有_______个无效状态,即跳过二进制数码_______到_______6个状态。

8、具有3个触发器的二进制计数器,他又_______种计数状态;具有4个触发器的二进制计数器,它有_____种计数状态。

9、10. 1n n n Q JQ KQ +=+是_______触发器的特性方程。

11、1n n Q S RQ +=+是________触发器的特性方程,其约束条件为__________。

12、1n n n Q TQ TQ +=+是_____触发器的特征方程。

13、我们可以用JK 触发器转换成其他逻辑功能触发器,令__________________,即转换成T 触发器;令_______________,即转换为'T触发器;令________________,即转换成D触发器。

二、选择1、存储8位二进制信息要()个触发器。

A.2B.4C.8D.162、对于T触发器,若原态Qn=0,欲使新态Qn+1=1,应使输入T=()。

习题六6.1填空题1.时序电路在逻辑功能上的特点是,电路在任一时刻的输出状态不仅取决于该时刻的,而且与有关。

2.分析异步时序电路不同于同步时序电路,必须同时分析每个触发器的信号。

3.计数器按照计数脉冲输入方式分为计数器、计数器。

4.一个逻辑电路,如果某一给定时刻的输出不仅决定于该时刻的输入,而且还与该时刻前电路所处的状态有关,则此电路为电路。

5.一个逻辑电路,如果某一给定时刻的输出仅决定于该时刻的输入,而与该时刻前电路所处的状态无关,则此电路为电路。

6.型时序电路的输出不仅与电路的内部状态有关,而且与外输入有关。

型时序电路的输出仅与电路的内部状态有关,而与外输入无关。

7.用n级触发器构成的计数器,计数容量最多可为。

8.用来表示时序电路的状态转移规律及相应的输入、输出关系的图形称为。

9.计数器中有效状态的数目,称为计数器的。

10.用二进制异步计数器从0计数到十进制数186,则最少需要个触发器。

11.单向移位寄存器工作于串行输入/并行输出方式,可实现数据的变换。

12.具有8个和12个触发器的异步二进制计数器,它们分别各有和状态。

13.若最简状态表中的状态数为10,则所需的状态变量至少应为。

14.8位移位寄存器,串行输入时经个CP脉冲后,8位数码全部移入寄存器中。

若该寄存器已存满8位数码,欲将其并行输出,则需个CP脉冲后,数码能全部输出;欲将其串行输出,则需个CP脉冲后,数码能全部输出。

15.时序电路一般由和两部分组成。

16.按电路状态的改变方式,时序电路分为和两种;按输入与输出关系,时序电路分为和两种。

17.如果一个计数器能够从无效状态返回到有效状态,就称为该计数器有,否则称为。

6.2选择题1.四位二进制计数器的计数容量是()A、2B、4C、10D、162.能实现数据串行——并行和并行——串行转换的电路是()A、二进制译码器B、数据分配器C、移位寄存器D、编码器3.用n个触发器构成计数器,可得到的最大计数长度为()A、nB、2nC、n2D、2 n4.下列电路中()个不是时序电路。

时序逻辑电路习题与答案一、填空题1.时序逻辑电路按状态转换情况可分为时序电路和时序电路两大类。

2.按计数进制的不同,可将计数器分为、和N进制计数器等类型。

3.用来累计和寄存输入脉冲个数的电路称为。

4.时序逻辑电路在结构方面的特点是:由具有控制作用的电路和具记忆作用电路组成。

、5.、寄存器的作用是用于、、数码指令等信息。

6.按计数过程中数值的增减来分,可将计数器分为为、和三种。

二、选择题A、单拍接收数码寄存器;B、双拍接收数码寄存器;C、单向移位寄存器;D、双向移位寄存器。

2.下列电路不属于时序逻辑电路的是。

A、数码寄存器;B、编码器;C、触发器;D、可逆计数器。

3.下列逻辑电路不具有记忆功能的是。

A、译码器;B、RS触发器;C、寄存器;D、计数器。

4.时序逻辑电路特点中,下列叙述正确的是。

A、电路任一时刻的输出只与当时输入信号有关;B、电路任一时刻的输出只与电路原来状态有关;C、电路任一时刻的输出与输入信号和电路原来状态均有关;D、电路任一时刻的输出与输入信号和电路原来状态均无关。

5.具有记忆功能的逻辑电路是。

A、加法器;B、显示器;C、译码器;D、计数器。

6.数码寄存器采用的输入输出方式为。

A、并行输入、并行输出;B、串行输入、串行输出;C、并行输入、串行输出;D、并行输出、串行输入。

1.如题图12.1所示电路为某寄存器的一位,该寄存器为。

三、判断下面说法是否正确,用“√\或“×\表示在括号1.寄存器具有存储数码和信号的功能。

( ) 2.构成计数电路的器件必须有记忆能力。

( ) 3.移位寄存器只能串行输出。

( ) 4.移位寄存器就是数码寄存器,它们没有区别。

( ) 5.同步时序电路的工作速度高于异步时序电路。

( ) 6.移位寄存器有接收、暂存、清除和数码移位等作用。

()思考与练习题12.1.1 时序逻辑电路的特点是什么? 12.1.2 时序逻辑电路与组合电路有何区别?12.3.1 在图12.1电路作用下,数码寄存器的原始状态Q3Q2Q1Q0=1001,而输入数码D3D2D1D0=0110时,在CP的作用下,Q3Q2Q1Q0状态如何变化?12.3.2 题图12.2所示移位寄存器的初始状态为111,画出连续3个CP脉冲作用下Q2Q1Q0各端的波形和状态表。

《时序逻辑电路》单元基础练习题一、填空题1、触发器具有种稳定状态。

在输入信号消失后,能保持输出状态不变,也就是说它具有功能。

在适当触发信号作用下,从一个稳态变为另一个稳态,因此,触发器可作为信息的存贮单元。

2、主从型触发器可以避免现象的产生。

3、触发器按照逻辑功能来分,类型主要有、、和,以及只具有功能的计数型触发器。

4、与非门构成的基本RS触发器的约束条件是R+S不能为。

5、触发器电路中,S D端、R D端可以根据需要预先将触发器或,而不受的同步控制。

6、JK触发器具有、、和逻辑功能。

7、为提高触发器工作的可靠性,增强抗干扰能力,常用触发器。

其输出状态仅取决于CP 或时触发器的状态。

8、在数字电路中,按照逻辑功能和电路特点,各种数字集成电路可分为逻辑电路和逻辑电路两大类。

9、时序电路一般由具有作用的电路和具有作用的电路两部分组成。

10、常用于接收、暂存、传递数码的时序电路是。

存放n位二进制数码需要个触发器。

11、能实现操作的电路称为计数器。

计数器按CP控制方式不同可分为计数器和计数器。

进制计数器是各种计数器的基础。

12、一个完整的数字译码显示电路通常由,,和四部分组成。

13、数码寄存器采用的方式存储数码,移位寄存器具备的特点。

14、计数电路还常用作器。

15、在频率测试电路中,若在0.0002s内,显示器显示为1000,则待测频率为KH Z。

二、选择题1、基本RS 触发器电路中,触发脉冲消失后,其输出状态( )A :恢复原状态B :保持现状态C :出现新状态D :不能确定 2、触发器与组合逻辑电路比较( )A :两者都有记忆能力B :只有组合逻辑电路有记忆能力C :只有触发器有记忆能力D :两者都没有记忆能力 3、在图中,由JK 触发器构成了( )A :D 触发器B :基本RS 触发器C :T 触发器D :同步RS 触发器 4、D 型触发器逻辑功能为( )A :置0、置1B :置0、置1、保持C 、保持、计数D :置0、置1、保持、计数 5、下列真值表为JK 触发器的真值表的是(A 、B 为输入)( )6、某四位右移寄存器初始并行输出状态为1111,若串行输入数据为1001,则第三个CP 脉冲作用下,并行输出的状态为( )A :1111B :0111C :0011D :1001 7、下列电路中不属于时序电路是( )A :同步计数器B :数码寄存器C :译码器D :异步计数器 8、为了提高电路抗干扰能力,触发脉冲宽度是( )A :越宽越好B :越窄越好C :无关的J KC A B C D9、不能完成计数功能的逻辑图为( )A B C D 10、如图对该触发器波形图说法正确的是( )A :第1时钟脉冲Q 状态错 CP 1 2 3 4B :第2时钟脉冲Q 状态错C :第3时钟脉冲Q 状态错 CPD :第4时钟脉冲Q 状态对 Q 11、下列说法错误的是A :JK 触发器的特性方程是Q n+1=J Q n +K Q nB :n 进制计数器,所计最大十进数为n-1。

时序逻辑电路练习题及答案《时序逻辑电路》练习题及答案[6.1] 分析图P6-1时序电路的逻辑功能,写出电路的驱动⽅程、状态⽅程和输出⽅程,画出电路的状态转换图,说明电路能否⾃启动。

图P6-1[解]驱动⽅程:311Q K J ==,状态⽅程:nn n n n n n Q Q Q Q Q Q Q 13131311⊕=+=+;122Q K J ==,n nn n n n n Q Q Q Q Q Q Q 12212112⊕=+=+; 33213Q K Q Q J ==,, n nn n Q Q Q Q 12313 =+;输出⽅程:3Q Y =由状态⽅程可得状态转换表,如表6-1所⽰;由状态转换表可得状态转换图,如图A6-1所⽰。

电路可以⾃启动。

表6-1n n n Q Q Q 123 Y Q Q Q n n n 111213+++ n nn Q Q Q 123 Y Q Q Q n n n 111213+++ 000 00 1 010 01 1 0010 0100 0110 1000 100 10 1 110 11 1 000 1 011 1 010 1 001 1图A6-1电路的逻辑功能:是⼀个五进制计数器,计数顺序是从0到4循环。

[6.2] 试分析图P6-2时序电路的逻辑功能,写出电路的驱动⽅程、状态⽅程和输出⽅程,画出电路的状态转换图。

A 为输⼊逻辑变量。

图P6-2[解]驱动⽅程:21Q A D =, 212Q Q A D = 状态⽅程:n n Q A Q 211=+, )(122112n nn n n Q Q A Q Q A Q +==+输出⽅程:21Q Q A Y = 表6-2由状态⽅程可得状态转换表,如表6-2所⽰;由状态转换表可得状态转换图,如图A6-2所⽰。

电路的逻辑功能是:判断A 是否连续输⼊四个和四个以上“1”信号,是则Y=1,否则Y=0。

图A6-2[6.3] 试分析图P6-3时序电路的逻辑功能,写出电路的驱动⽅程、状态⽅程和输出⽅程,画出电路的状态转换图,检查电路能否⾃启动。