华为verilog培训教程

- 格式:pdf

- 大小:329.15 KB

- 文档页数:41

verilog数字系统设计教程Verilog数字系统设计教程作者:XXX引言:数字系统设计是现代电子工程中非常重要的一部分。

Verilog作为一种硬件描述语言,提供了一种方便且专业的方法来设计和描述数字系统。

本教程旨在为初学者提供关于Verilog数字系统设计的详细介绍和指导。

1. Verilog简介Verilog作为一种硬件描述语言,用于描述数字系统的功能、结构和时序行为。

它类似于C语言,但更专注于硬件级别。

Verilog可以用于设计各种数字系统,例如处理器、嵌入式系统、通信设备等。

2. Verilog基本语法2.1 模块定义Verilog的基本单位是模块。

模块是数字系统的基本组成部分,可以看作是一个独立的功能单元。

模块可以包含输入、输出、内部信号以及其它子模块等。

2.2 信号声明在Verilog中,可以声明各种类型的信号,包括输入信号、输出信号和内部信号等。

信号声明定义了信号的类型、宽度和方向。

3. Verilog建模3.1 组合逻辑建模组合逻辑是数字系统中最基本的部分。

Verilog提供了各种组合逻辑建模的方法,包括逻辑运算、选择结构和多路复用器等。

3.2 时序逻辑建模时序逻辑是数字系统中需要考虑时序关系的部分。

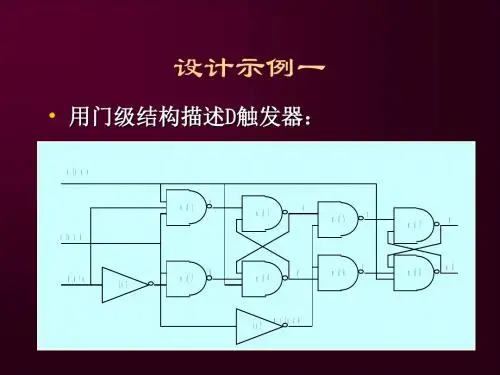

Verilog提供了时序逻辑建模的方法,包括触发器、计数器和时序控制等。

4. Verilog仿真4.1 仿真器介绍仿真器是用于验证数字系统设计的工具。

Verilog可以与各种仿真器配合使用,用于验证设计的正确性和性能。

4.2 仿真流程仿真流程包括编写测试平台和测试用例、编译和仿真等步骤。

本节将介绍基本的仿真流程和相关技巧。

5. Verilog综合5.1 综合概述综合是将Verilog代码转换为逻辑门级描述的过程。

综合器通过将Verilog代码映射到实际的硬件库中,生成能够实现指定功能的逻辑电路。

5.2 综合流程综合流程包括综合前的优化和综合本身两个阶段。

本节将介绍综合的基本流程和主要考虑因素。

共41页资源类别: HDL 语言内部公开1.0密级版本文档编号文档中心Verilog HDL 入门教程(仅供内部使用)yyyy/mm/dd日期:批准:日期:中研基础批准:2004.8.3日期:中研基础拟制:版权所有 不得复制修订记录初稿完成1.002004.8.3作者描述修订版本日期绝密请输入文档编号Verilog HDL 入门教程2004-08-16第2页,共41页版权所有,侵权必究目 录285 结构建模..............................................................274.8 case 语句. (25)4.7 条件语句 (25)4.6.6 连接运算符 (25)4.6.5 条件运算符 (24)4.6.4 按位逻辑运算符 (23)4.6.3 逻辑运算符 (22)4.6.2 关系运算符 (21)4.6.1 算术运算符 (21)4.6 运算符和表达式 (20)4.5.2 寄存器类型 (20)4.5.1 线网类型 (20)4.5 数据类型 (18)4.4.2 常量 (18)4.4.1 值集合 (18)4.4 数字值集合 (18)4.3 格式 (17)4.2 注释 (17)4.1.3 书写规范建议 (17)4.1.2 关键词 (17)4.1.1 定义 (17)4.1 标识符 (17)4 Verilog HDL 基本语法....................................................163.3.4 混合设计描述.. (15)3.3.3 行为描述方式 (14)3.3.2 数据流描述方式 (12)3.3.1 结构化描述方式 (12)3.3 三种建模方式 (11)3.2 时延 (11)3.1.3 模块语法 (10)3.1.2 模块的结构 (9)3.1.1 简单事例 (9)3.1 模块 (9)3 Verilog HDL 建模概述.....................................................72.4.2 能力. (7)2.4.1 历史 (7)2.4 Verilog HDL 简介 (6)2.3 设计方法学 (6)2.2 硬件描述语言 (5)2.1 数字电路设计方法 (5)2 HDL 设计方法学简介......................................................51 前言...................................................................绝密请输入文档编号Verilog HDL 入门教程2004-08-16第3页,共41页版权所有,侵权必究4010 附录A Verilog 保留字...................................................399 习题..................................................................398 其他方面..............................................................377.4 行为建模具体实例...................................................367.3 过程赋值语句......................................................357.2 顺序语句块........................................................357.1 简介.............................................................357 行为建模..............................................................346.3 数据流建模具体实例.................................................346.2 阻塞赋值语句......................................................346.1 连续赋值语句......................................................346 数据流建模............................................................315.4 结构化建模具体实例.................................................295.3 实例化语句........................................................285.2 模块端口..........................................................285.1 模块定义结构......................................................绝密请输入文档编号Verilog HDL 入门教程2004-08-16第4页,共41页版权所有,侵权必究Verilog HDL 入门教程关键词:摘 要:本文主要介绍了Verilog HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL设计方法,初步了解并掌握Verilog HDL 语言的基本要素,能够读懂简单的设计代码并能够进行一些简单设计的Verilog HDL 建模。

文档编号版本密级文档中心内部公开资源类别:HDL语言共41页Verilog HDL入门教程(仅供内部使用)拟制:中研基础日期:批准:中研基础日期:批准:日期:yyyy/mm/dd版权所有不得复制修订记录日期修订版本描述作者初稿完成目录1 前言. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 2 HDL设计方法学简介. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 数字电路设计方法. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 硬件描述语言. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 设计方法学. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Verilog HDL简介. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 历史. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 能力. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 3 Verilog HDL 建模概述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 模块. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 简单事例. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 模块的结构. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10模块语法. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11时延. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11三种建模方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12结构化描述方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12数据流描述方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14行为描述方式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15混合设计描述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 4 Verilog HDL 基本语法. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17标识符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17定义. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17关键词. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17书写规范建议. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .数字值集合. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18值集合. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18常量. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18数据类型. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20线网类型. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20寄存器类型. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20运算符和表达式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21算术运算符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21关系运算符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22逻辑运算符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23按位逻辑运算符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24条件运算符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25连接运算符. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25条件语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25case 语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 5 结构建模. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .282004-08-16 第3页,共41页版权所有,侵权必究模块定义结构. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .模块端口. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .实例化语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .结构化建模具体实例. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 数据流建模. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .连续赋值语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .阻塞赋值语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .数据流建模具体实例. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 行为建模. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .简介. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .顺序语句块. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .过程赋值语句. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .行为建模具体实例. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 其他方面. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 习题. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 附录A Verilog 保留字. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282829 31 34 34 343435 35353637 393940Verilog HDL 入门教程关键词:摘要:本文主要介绍了Verilog HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL 设计方法,初步了解并掌握Verilog HDL语言的基本要素,能够读懂简单的设计代码并能够进行一些简单设计的Verilog HDL建模。

FPGA设计流程指南前言本部门所承担的FPGA设计任务主要是两方面的作用:系统的原型实现和ASIC的原型验证。

编写本流程的目的是:●在于规范整个设计流程,实现开发的合理性、一致性、高效性。

●形成风格良好和完整的文档。

●实现在FPGA不同厂家之间以及从FPGA到ASIC的顺利移植。

●便于新员工快速掌握本部门FPGA的设计流程。

由于目前所用到的FPGA器件以Altera的为主,所以下面的例子也以Altera为例,工具组合为modelsim + LeonardoSpectrum/FPGACompilerII + Quartus,但原则和方法对于其他厂家和工具也是基本适用的。

目录1. 基于HDL的FPGA设计流程概述 (1)1.1 设计流程图 (1)1.2 关键步骤的实现 (2)1.2.1 功能仿真 (2)1.2.2 逻辑综合 (2)1.2.3 前仿真 (3)1.2.4 布局布线 (3)1.2.5 后仿真(时序仿真) (4)2. Verilog HDL设计 (4)2.1 编程风格(Coding Style)要求 (4)2.1.1 文件 (4)2.1.2 大小写 (5)2.1.3 标识符 (5)2.1.4 参数化设计 (5)2.1.5 空行和空格 (5)2.1.6 对齐和缩进 (5)2.1.7 注释 (5)2.1.8 参考C语言的资料 (5)2.1.9 可视化设计方法 (6)2.2 可综合设计 (6)2.3 设计目录 (6)3. 逻辑仿真 (6)3.1 测试程序(test bench) (7)3.2 使用预编译库 (7)4. 逻辑综合 (8)4.1 逻辑综合的一些原则 (8)4.1.1 关于LeonardoSpectrum (8)4.1.1 大规模设计的综合 (8)4.1.3 必须重视工具产生的警告信息 (8)4.2 调用模块的黑盒子(Black box)方法 (8)参考 (10)修订纪录 (10)1. 基于HDL的FPGA设计流程概述1.1 设计流程图说明:●逻辑仿真器主要指modelsim,Verilog-XL等。

Verilog HDL培训第一部分初级篇第一章Verilog的基本知识1.1硬件描述语言HDL硬件描述语言HDL(Hardware Description Language)是一种形式化方法来描述数字电路和系统的语言。

1.2Verilog HDL的历史Verilog HDL是硬件描述语言的一种,用于数字电子系统设计。

设计者可用它进行各种级别的逻辑设计,可用它进行数字逻辑系统的仿真验证、时序分析、逻辑综合。

它是目前应用最广泛的一种硬件描述语言。

Verilog HDL是在1983年,由GDA(GateWay Design Automation)公司的Phil Moorby 首创的。

1.3Verilog HDL和VHDL的比较Verilog HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。

Verilog HDL和VHDL做为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的行为和结构;支持逻辑设计中层次与范围的描述;可借用高级语言的精巧结构来简化电路行为的描述;具有电路仿真与验证机制以保证设计的正确性;支持电路描述由高层到低层的综合转换;硬件描述与实现工艺无关;便于文档管理;易于理解和设计重用。

Verilog HDL和VHDL各有其自己的特点。

V erilog HDL的最大优点:它是一种非常容易掌握的硬件描述语言,只要有C语言的编程基础,一般可以再2~3个月内掌握这种设计技术。

掌握VHDL设计技术就比较困难。

因为VHDL不是很直观,需要有Ada编程基础,一般认为至少需要半年以上的专业培训,才能掌握VHDL的基本设计技术。

1.4Verilog HDL的设计流程简介1.4.1 自顶向下(Top-Down)设计的基本概念自顶向下的设计是从系统级开始,把系统划分为若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接用EDA元件库中的基本元件来实现为止。

Verilog_HDL教程

1.简介

Verilog HDL是由美国电气和电子工程师协会(IEEE)于1984年开

发的一种硬件描述语言。

它是一种面向数据流的语言,主要用于描述数字

逻辑电路的行为和结构。

Verilog HDL可以用于设计和仿真各种数字电路,如计算机处理器、存储器、控制逻辑和通信接口等。

2.基本语法

下面是Verilog HDL的基本语法元素:

2.1模块

模块是Verilog HDL中的最基本的构建单元。

每个模块都有一个名称

和一个端口列表。

端口可以是输入或输出,也可以是双向的。

2.2数据类型

2.3信号赋值

可以使用赋值运算符(=)将值赋给变量或信号。

还可以使用阻塞或

非阻塞赋值运算符来实现顺序或并发的赋值操作。

3.设计结构

4.运算符

5.仿真和验证

总结:

本教程简要介绍了Verilog HDL的基本语法和用法。

Verilog HDL是一种被广泛应用于数字电路设计的硬件描述语言。

通过学习本教程,您将能够开始使用Verilog HDL进行数字电路的设计和验证。

共41页 资源类别: HDL语言

内部公开1.0密级版本文档编号文档中心

Verilog HDL入门教程(仅供内部使用)

yyyy/mm/dd日期:批准:日期:中研基础批准:2004.8.3日期:中研基础拟制:

版权所有 不得复制修订记录初稿完成1.002004.8.3作者描述修订版本日期

绝密请输入文档编号Verilog HDL 入门教程

2004-08-16第2页,共41页版权所有,侵权必究目 录285 结构建模..............................................................

274.8 case 语句..........................................................

254.7 条件语句..........................................................

254.6.6 连接运算符....................................................

254.6.5 条件运算符....................................................

244.6.4 按位逻辑运算符................................................

234.6.3 逻辑运算符....................................................

224.6.2 关系运算符....................................................

214.6.1 算术运算符....................................................

214.6 运算符和表达式.....................................................

204.5.2 寄存器类型 ...................................................

204.5.1 线网类型......................................................

204.5 数据类型..........................................................

184.4.2 常量.........................................................

184.4.1 值集合.......................................................

184.4 数字值集合........................................................

184.3 格式.............................................................

174.2 注释.............................................................

174.1.3 书写规范建议..................................................

174.1.2 关键词.......................................................

174.1.1 定义.........................................................

174.1 标识符............................................................

174 Verilog HDL 基本语法....................................................

163.3.4 混合设计描述..................................................

153.3.3 行为描述方式..................................................

143.3.2 数据流描述方式................................................

123.3.1 结构化描述方式................................................

123.3 三种建模方式......................................................

113.2 时延.............................................................

113.1.3 模块语法......................................................

103.1.2 模块的结构....................................................

93.1.1 简单事例.......................................................

93.1 模块..............................................................

93 Verilog HDL 建模概述.....................................................

72.4.2 能力..........................................................

72.4.1 历史..........................................................

72.4 Verilog HDL简介.....................................................

62.3 设计方法学.........................................................

62.2 硬件描述语言.......................................................

52.1 数字电路设计方法....................................................

52 HDL设计方法学简介......................................................

51 前言...................................................................

绝密请输入文档编号Verilog HDL 入门教程

2004-08-16第3页,共41页版权所有,侵权必究4010 附录A Verilog 保留字...................................................

399 习题..................................................................

398 其他方面..............................................................

377.4 行为建模具体实例...................................................

367.3 过程赋值语句......................................................

357.2 顺序语句块........................................................

357.1 简介.............................................................

357 行为建模..............................................................

346.3 数据流建模具体实例.................................................

346.2 阻塞赋值语句......................................................

346.1 连续赋值语句......................................................

346 数据流建模............................................................

315.4 结构化建模具体实例.................................................

295.3 实例化语句........................................................

285.2 模块端口..........................................................

285.1 模块定义结构......................................................

绝密请输入文档编号Verilog HDL 入门教程

2004-08-16第4页,共41页版权所有,侵权必究