第二章 DSP芯片内的CPU外围电路

- 格式:ppt

- 大小:4.07 MB

- 文档页数:141

DSP芯片外围电路典型设计(数字信号处理器芯片TMS320FDSP芯片外围电路典型设计(数字信号处理器芯片TMS320F206):引言DSP(数字信号处理器)芯片是一种能够实时快速地实现各种数字信号处理算法控制的微处理器,已经在通信与信息系统、信号与处理、自动控制、雷达、航空航天、医疗等许多领域得到了广泛的应用。

目前生产DSP芯片的厂家主要有TI公司、AD 公司、Motorola公司等。

其中TI公司推出的TMS320C2XX系列是继TMS320C2X 和TMA320C5X之后的一种低价格、高性能16位定点运算DSP。

TMS320F206是2DSP芯片外围电路典型设计(数字信号处理器芯片T MS320F206) :引言DSP(数字信号处理器)芯片是一种能够实时快速地实现各种数字信号处理算法控制的微处理器,已经在通信与信息系统、信号与处理、自动控制、雷达、航空航天、医疗等许多领域得到了广泛的应用。

目前生产DSP芯片的厂家主要有TI公司、AD公司、Motorola公司等。

其中TI公司推出的TMS320C2XX系列是继TMS320C2X和 TMA320C5X之后的一种低价格、高性能16位定点运算DSP。

TMS320F206是2XX系列的代表之一,性价比高,应用广泛,目前已成为高档单片机的理想替代。

TMS320F206的性能特点如下:指令周期达25 ns;可寻址64 k程序空间、64 k数据空间、64 k I/O空间以及32 k全局存储空间;片内集成有32 kB Flash存储器;32位算术逻辑单元、32位累加器、16位并行乘法器;丰富的片内外设,可编程等待状态发生器、锁相环、同步串行口、异步串行口等;与IEEE 1149.1标准兼容的JTAG串行逻辑扫描电路。

DSP芯片外围电路设计是用好DSP芯片最关键的第1步。

本文以TMS320F206为例介绍DSP芯片前向通道和后向通道接口电路、外存存储器扩展等典型的设计思路及方法。

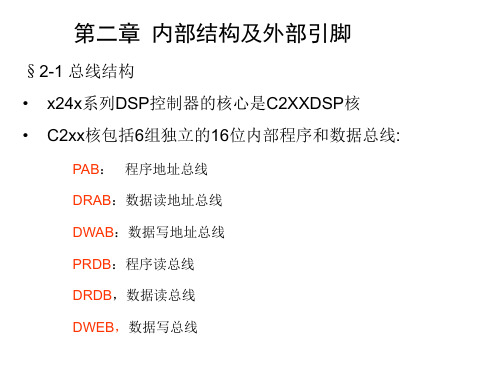

第2章DSP的硬件结构DSP的硬件结构:DSP与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP和一般的CPU 又有不同, DSP有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA总线和控制器等。

Von Neuman结构与Harvard结构:Harvard结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90亿次浮点运算/秒(9000MFLOPS)。

MIPS--Million Instruction Per SecondMFLOPS--Million Floating Operation Per Second流水操作(pipeline):独立的硬件乘法器:在卷积、数字滤波、FFT、相关、矩阵运算等算法中,都有A(kB(n-k一类的运算,大量重复乘法和累加。

通用计算机的乘法用软件实现,用若干个机器周期。

DSP有硬件乘法器,用MAC指令(取数、乘法、累加)在单周期内完成。

独立的DMA总线和控制器:有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU工作的条件下,DMA速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10个机器周期,乘法是一系列的移位和加法,需要数十个机器周期。

DSP的CPU设置硬件乘法器,可以在单周期内完成乘法和累加.移位:通用微处理器的移位,每调用一次移位指令移动1-bitDSP可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换.溢出:通用CPU中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP把移位输出的最高位(MSB)存放在一个位检测状态寄存器中,检测到MSB=1时,就通知下一次会发生溢出,可以采取措施防止.数据地址发生器(DAG):在通用CPU中,数据地址的产生和数据的处理都由ALU来完成在DSP中,设置了专门的数据地址发生器(实际上是专门的ALU),来产生所需要的数据地址,节省公共ALU的时间.外设(peripherals):时钟发生器(振荡器与PLL)定时器(Timer)软件可编程等待状态发生器通用I/O同步串口(SSP)与异步串口(ASP)JTAG扫描逻辑电路(IEEE 1149.1标准便于对DSP作片上的在线仿真和多DSP条件下的调试’C54x的内部结构:中央处理器CPU 、内部总线控制、特殊功能寄存器、数据存储器RAM 、程序存储器ROM、I/O功能扩展接口、串行口、、主机通信接口HPI、定时系统、中断系统。

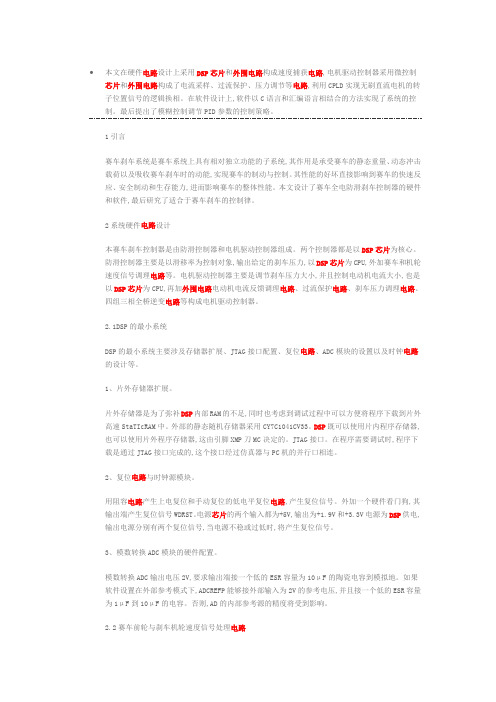

本文在硬件电路设计上采用DSP芯片和外围电路构成速度捕获电路,电机驱动控制器采用微控制芯片和外围电路构成了电流采样、过流保护、压力调节等电路,利用CPLD实现无刷直流电机的转子位置信号的逻辑换相。

在软件设计上,软件以C语言和汇编语言相结合的方法实现了系统的控制。

最后提出了模糊控制调节PID参数的控制策略。

1引言赛车刹车系统是赛车系统上具有相对独立功能的子系统,其作用是承受赛车的静态重量、动态冲击载荷以及吸收赛车刹车时的动能,实现赛车的制动与控制。

其性能的好坏直接影响到赛车的快速反应、安全制动和生存能力,进而影响赛车的整体性能。

本文设计了赛车全电防滑刹车控制器的硬件和软件,最后研究了适合于赛车刹车的控制律。

2系统硬件电路设计本赛车刹车控制器是由防滑控制器和电机驱动控制器组成。

两个控制器都是以DSP芯片为核心。

防滑控制器主要是以滑移率为控制对象,输出给定的刹车压力,以DSP芯片为CPU,外加赛车和机轮速度信号调理电路等。

电机驱动控制器主要是调节刹车压力大小,并且控制电动机电流大小,也是以DSP芯片为CPU,再加外围电路电动机电流反馈调理电路、过流保护电路、刹车压力调理电路、四组三相全桥逆变电路等构成电机驱动控制器。

2.1DSP的最小系统DSP的最小系统主要涉及存储器扩展、JTAG接口配置、复位电路、ADC模块的设置以及时钟电路的设计等。

1、片外存储器扩展。

片外存储器是为了弥补DSP内部RAM的不足,同时也考虑到调试过程中可以方便将程序下载到片外高速StaTIcRAM中。

外部的静态随机存储器采用CY7C1041CV33。

DSP既可以使用片内程序存储器,也可以使用片外程序存储器,这由引脚XMP刀MC决定的。

JTAG接口。

在程序需要调试时,程序下载是通过JTAG接口完成的,这个接口经过仿真器与PC机的并行口相连。

2、复位电路与时钟源模块。

用阻容电路产生上电复位和手动复位的低电平复位电路,产生复位信号。

外加一个硬件看门狗,其输出端产生复位信号WDRST。