VHDL花样彩灯_实验报告

- 格式:pdf

- 大小:272.48 KB

- 文档页数:14

一、设计目的本课程设计的目的是熟练掌握相关软件的使用和操作。

能对VHD1语言程序进行编译,调试,以及通过计算机仿真,得到正确的仿真波形图,并根据所得仿真波形图分析判断并改进所设计的电路。

在成功掌握软件操作基础上,将所数字电路的基础课知识与VHD1语言的应用型知识结合起来并与实际设计,操作联系起来,即“理论联系实际:深入了解VHD1语言的作用与价值,对用硬件语言设计一个电路系统开始具备一个较完整的思路与较专业的经验。

对EDA技术有初步的认识,并开始对EDA技术的开发创新有初步的理解。

二、设计内容及操作1、设计循环彩灯控制器1.1设计内容设计一个循环彩灯控制器,该控制器控制红,绿,黄三个发光管循环点亮。

要求红发光管亮3秒,绿发光管亮2秒,黄发光管亮1秒。

1.2程序设计1IBRARYIEEE;USEIEEE.STD_10GIC_1164.A11;USEIEEE.STD_1OGIC_UNSIGNED.A11;ENTITYcaideng_2ISPORT(e1k:INSTD_1OGIC;red,green,ye11ow:OUTSTD1OGIC);ENDENTITYCaideng_2;ARCHITECTUREexamp1eOFcaideng_2ISSIGNA1dout:STD_1OGIC_VECTOR(2DoWNTO0);SIGNA1m:STD_10GIC_VECT0R(2DOWNTO0);BEGINred<=dout(2);green<=dout(1);ye11ow<=dout(0);PROCESS(e1k)ISBEGINIF(c1k,EVENTANDC1k=T')THENIF(In="110")THENm<="001";E1SEm<=m+1;ENDIF;CASEmISWHEN"001"=〉dout<=〃100〃;WHEN"010"=>dout<=T00";WHEN,/0ir=>dout<="100";WHEN"100"=>dout<="010";WHEN"101"=>dout<="010";WHEN"110"=>dout<="001";WHENOTHERS=>dout<="000";ENDCASE;ENDIF;ENDPROCESS;ENDARCHITECTURE;1.3仿真波形图14波形图分析在仿真时已经设置好开始时间和结束时间,根据以上的波形图可知,当e1k 信号处于高电平(高低电平可以根据自己所设计的情况自己定义),红发光管最先亮灯(高电平表示亮灯),时间为3s,3s之后绿发光管开始亮灯2s,2s结束黄发光管亮1s,以此循环亮灯,直到仿真结束时间。

实验名称:彩灯控制电路设计与实现实验任务要求:用VHDL 语言设计并实现一个彩灯控制电路,仿真并下载验证其功能。

彩灯有两种工作模式 ,可通过拨码开关或按键进行切换。

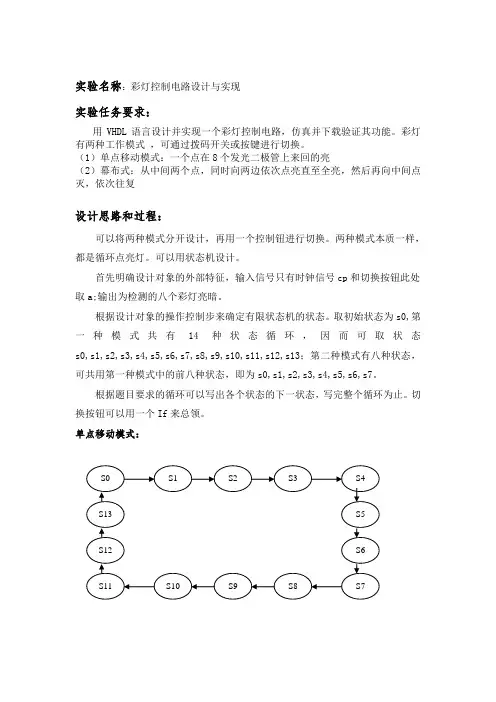

(1)单点移动模式:一个点在8个发光二极管上来回的亮(2)幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复设计思路和过程:可以将两种模式分开设计,再用一个控制钮进行切换。

两种模式本质一样,都是循环点亮灯。

可以用状态机设计。

首先明确设计对象的外部特征,输入信号只有时钟信号cp 和切换按钮此处取a;输出为检测的八个彩灯亮暗。

根据设计对象的操作控制步来确定有限状态机的状态。

取初始状态为s0,第一种模式共有14种状态循环,因而可取状态s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13;第二种模式有八种状态,可共用第一种模式中的前八种状态,即为s0,s1,s2,s3,s4,s5,s6,s7。

根据题目要求的循环可以写出各个状态的下一状态,写完整个循环为止。

切换按钮可以用一个If 来总领。

单点移动模式:S0 S5S13 S7S8 S9 S10 S11 S1 S2 S3 S4S12 S6幕布式:流程图:彩灯电路设计语言:library ieee;use ieee.std_logic_1164.all;entity pmd isport(a,cp:in std_logic; %输入信号deng: out std_logic_vector(7 downto 0) %输出灯信号);end pmd;architecture arch of pmd istype all_state is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13);%枚举状态机状态 S0 S7 S6 S1 S5 S4S2 S3signal state:all_state; %状态转换符号begin %开始程序process(cp)beginif (cp'event and cp='1')then %时钟信号开始计数if(a='1')then %单点循环模式case state iswhen s0=> state<=s1;deng<="00000001"; %状态循环when s1=> state<=s2;deng<="00000010";when s2=> state<=s3;deng<="00000100";when s3=> state<=s4;deng<="00001000";when s4=> state<=s5;deng<="00010000";when s5=> state<=s6;deng<="00100000";when s6=> state<=s7;deng<="01000000";when s7=> state<=s8;deng<="10000000";when s8=> state<=s9;deng<="01000000";when s9=> state<=s10;deng<="00100000";when s10=> state<=s11;deng<="00010000";when s11=> state<=s12;deng<="00001000";when s12=> state<=s13;deng<="00000100";when s13=> state<=s0;deng<="00000010";when others =>state<=s0;deng<="00000000";end case;Else %切换为幕布式case state iswhen s0=> state<=s1;deng<="00011000";when s1=> state<=s2;deng<="00111100";when s2=> state<=s3;deng<="01111110";when s3=> state<=s4;deng<="11111111";when s4=> state<=s5;deng<="01111110";when s5=> state<=s6;deng<="00111100";when s6=> state<=s7;deng<="00011000";when s7=> state<=s0;deng<="00000000";when others =>state<=s0;deng<="00000000";end case;end if;end if;end process; end arch;输入波形:添加五十分频后的仿真程序:library ieee;use ieee.std_logic_1164.all;entity cd isport(a,clk:in std_logic;q: out std_logic_vector(7 downto 0));end cd;architecture a of cd istype all_state is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13);signal state:all_state;signal cnt : integer range 0 to 24999999; %50分频状态signal clk_tmp : std_logic;beginprocess(clk)Begin %开始运行分频信号if (clk'event and clk='1') thenif cnt=24999999 thencnt<=0;clk_tmp<= not clk_tmp;elsecnt<=cnt+1;end if;end if;if (clk_tmp'event and clk_tmp='1')then %分频后运行彩灯程序if(a='1')thencase state iswhen s1=> state<=s2;q<="00000010";when s2=> state<=s3;q<="00000100";when s3=> state<=s4;q<="00001000";when s4=> state<=s5;q<="00010000";when s5=> state<=s6;q<="00100000";when s6=> state<=s7;q<="01000000";when s7=> state<=s8;q<="10000000";when s8=> state<=s9;q<="01000000";when s9=> state<=s10;q<="00100000";when s10=> state<=s11;q<="00010000";when s11=> state<=s12;q<="00001000";when s12=> state<=s13;q<="00000100";when s13=> state<=s0;q<="00000010";when others =>state<=s0;q<="00000000";end case;elsecase state iswhen s0=> state<=s1;q<="00011000";when s1=> state<=s2;q<="00111100";when s2=> state<=s3;q<="01111110";when s3=> state<=s4;q<="11111111";when s5=> state<=s6;q<="00111100";when s6=> state<=s7;q<="00011000";when s7=> state<=s0;q<="00000000";when others =>state<=s0;q<="00000000";end case;end if;end if;end process;end a;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity cd isport(a,clk:in std_logic;q: out std_logic_vector(7 downto 0));end cd;architecture a of cd istype all_state is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13); signal state:all_state;beginprocess(clk)beginif (clk'event and clk='1') thenif(a='1') thencase state iswhen s0=> state<=s1;q<="00000001";when s1=> state<=s2;q<="00000010";when s2=> state<=s3;q<="00000100";when s3=> state<=s4;q<="00001000";when s4=> state<=s5;q<="00010000";when s5=> state<=s6;q<="00100000";when s6=> state<=s7;q<="01000000";when s7=> state<=s8;q<="10000000";when s8=> state<=s9;q<="01000000";when s9=> state<=s10;q<="00100000";when s10=> state<=s11;q<="00010000";when s11=> state<=s12;q<="00001000";when s12=> state<=s13;q<="00000100";when s13=> state<=s0;q<="00000010";when others =>state<=s0;q<="00000000";end case;elsecase state iswhen s0=> state<=s1;q<="00011000";when s1=> state<=s2;q<="00111100";when s2=> state<=s3;q<="01111110";when s3=> state<=s4;q<="11111111";when s4=> state<=s5;q<="01111110";when s5=> state<=s6;q<="00111100";when s6=> state<=s7;q<="00011000";when s7=> state<=s0;q<="00000000";when others =>state<=s0;q<="00000000";end case;end if;end if;end process;end a;故障及问题分析:1.编写这个程序时,很自然地想到用一个输入信号控制两种模式的切换,但把这个输入放在哪里,如何放,开始出现了几种想法。

基于VHDL实现多路彩灯控制器设计应用关键词:VHDL 彩灯控制07通信工程本科班沈治文摘要:设计一个彩灯控制程序器。

可以实现四种花型循环变化,有复位开关。

整个系统共有三个输入信号CLK,RST,Sel,八个输出信号控制八个彩灯。

时钟信号CLK脉冲由系统的晶振产生。

各种不同花样彩灯的变换由Sel控制.此彩灯控制系统设定有四种花样变化,这四种花样可以进行切换,四种花样分别为:(1) 彩灯从左到右逐次闪亮。

(2)彩灯从左向右逐次点亮,且亮后不熄灭。

(3) 彩灯两边同时亮两个,然后逐次向中间点亮。

(4) 全部彩灯亮与熄灭交替。

Abstract: The design of a control program Lantern device. Four kinds of flowers can be achieved circulation change, reset switch. The whole system has three input signals CLK, RST, Sel, 8 output signal control 8 lights. The clock signal CLK pulses generated by the system of the crystal. Lanterns of different patterns of transformation controlled by Sel. The lights control system configuration there are four patterns change, four kinds of patterns can be switched, four kinds of patterns are as follows:(1) successive flashing lights from left to right.(2) successive lantern lit from left to right, and the light is not extinguished after.(3) The two bright lights on both sides at the same time, and then successively to the center light.(4) All lights turn bright and quenching在日常生活中,为了增加聚会或是过节氛围,经常要使用到彩灯循环点亮。

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

实验二彩灯实验一、实验项目彩灯控制实验:利用开发实验平台上的8 个LED 实现常见彩灯实验。

二、实验目的1、学习QuatusII开发软件的基本操作。

2、熟悉教学实验板的使用。

3、初步掌握VHDL语言的设计、输入、编译、仿真和调试过程。

4、掌握USB-BLASTER下载工具的安装、以及程序下载方法。

三、实验内容1、首先编译下载给定的VHDL硬件描述语言编写的彩灯控制示例程序,仔细观察在实验板上的现象。

2、用VHDL语言编辑彩灯控制程序,通过按键控制开发实验平台上的8个LED灯的点亮顺序:(1)按键可选择核心板上的按键,或EDA主板上矩阵键盘作为按键,或DKA系列按键;(2)通过一个按键控制8个LED灯从左向右依次循环点亮;(3)通过一个按键控制8个LED灯从右向左依次循环点亮;(4)通过一个按键控制8个LED灯从中间向两边依次循环点亮;(5)通过一个按键控制8个LED灯从两边向中间依次循环点亮;(6)通过一个按键控制8个LED灯全部点亮;(7)通过一个按键控制8个LED灯全部熄灭。

(8)以上共使用了六个按键控制六种点亮方式3、扩展内容:能够设置8个LED灯的点亮频率(通过时钟、分频器实现)。

4、使用三个按键控制LED点亮的六种方式。

5、在QuatusII平台上进行波形仿真,保存一组通过按键控制8个LED灯从中间向两边依次循环点亮的仿真波形图。

6、描述在实验板上观察到的现象。

四、实验仪器计算机、USB-BLASTER下载线、数字系统实验箱、5V稳压电源。

五、实验原理1、EDA主板上8个LED灯的电路连接如图1所示。

8个LED采用74LS244进行隔离驱动,当FPGA对应I/O口为高电平时,相应的LED灯点亮;为低电平时,灯熄灭。

2、表1是对应的FPGA映射管脚表,即编译通过后,进行器件管脚分配时必须按照相应的管脚号进行分配,否则就无法进行硬件验证测试。

图1 8个LED灯的电路连接图表1 LED灯对应的FPGA映射管脚表器件名网络名FPGA映射管脚LED-0SD0165LED-1SD1166LED-2SD2167LED-3SD3168LED-4SD4169LED-5SD5170LED-6SD6173LED-7SD71743、FPGA时钟连接电路及管脚分配分别如图2和表2所示。

实验四————LED数码管显示数字实验内容:在四个七段LED数码管上显示数字“1234”。

实验原理:实现LED数码管数字显示电路的输入和输出端口控制信号如图所示clkLed_bit reset led_seg输入和输出端口信号图中clk信号为50MHz时钟信号。

reset信号为复位按键输入信号,当reset按键按下时,reset信号为低电平。

输出信号led_bit为驱动LED数码管的位码信号,因为有四个LED 数码管,需要四根信号线,控制四个LED数码管中的哪一个LED数码管显示。

输出信号led_seg为驱动LED数码管的段码信号,共有八根信号线,分别是a,b,c,d,e,f,g,dp段,输出信号led_seg能够控制一个LED数码管中的哪一段显示。

四个七段LED数码管的排列如下图所示:四个LED数码管LED数码管采用共阳极发光二极管,如下图所示,需要点亮数码管中的某一段时,应该在对应段的段码信号输出低电平。

共阳极LED数码管由于每个LED数码管有八个发光二极管,八个发光二极管同时导通时需要提供比较大的电流,需要给共阳极加驱动电路,如下图所示,当需要某一LED数码管显示数字时,就给该行的控制信号led_bit(i)提供一个低电平信号。

共阳极LED数码管的阳极驱动电路原理图实验内容:本次实验采用了两个进程:1.scanclk_get:获取扫描时序控制信号2.led_selest_get:选择数码管并显示数字流程图:Clknum scan_cntr reset led_bit<3:0>源代码:library IEEE;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity EXP4_M isport(clk,rst:in std_logic;led_bit:out std_logic_vector(3 downto 0); led_seg:out std_logic_vector(7 downto 0)); end EXP4_M;进程scanclk_get 产生LED 数码管扫描时序控制电路 Led_select_d isplay 进程选择要显示的数据和对应的数码管 七段译码器architecture Behavioral of EXP4_M issignal scanclk:std_logic_vector(17 downto 0);beginscanclk_get:process(clk,rst)beginif rst='0' thenscanclk<=(others=>'0');elsif rising_edge(clk) thenscanclk<=scanclk+1;end if;end process scanclk_get;led_select_display:process(scanclk)begincase scanclk(17 downto 16) iswhen "00" =>led_bit<="1110";led_seg<="10011111" ;when "01"=>led_bit<="1101";led_seg<="00100101" ;when "10"=>led_bit<="1011";led_seg<="00001101" ;when "11"=>led_bit<="0111";led_seg<="10011001" ;when others =>null;end case;end process led_select_display;end Behavioral;UCF文件:net "clk" loc =Y11;net "rst" loc =J3;net "led_bit(0)" loc =M5;net "led_bit(1)" loc =M4;net "led_bit(2)" loc =M3;net "led_bit(3)" loc =M2;net "led_seg(0)" loc =R4;net "led_seg(1)" loc =T3;net "led_seg(2)" loc =T2;net "led_seg(3)" loc =T1;net "led_seg(4)" loc =N4;net "led_seg(5)" loc =N3;net "led_seg(6)" loc =N2;net "led_seg(7)" loc =N1;实验结果:实验箱数码管依次显示“1234”。

实验报告课程名称可编程逻辑器件实验项目名称彩灯学生班级学生姓名2013年 04 月 21 日目录一、实验目的和要求二、实验方案设计及其原理三、硬件要求四、源程序和下载结果五、实验结果分析六、实验收获和体验一、实验目的和要求熟悉分频的分频原理,并将之进行多次分频,将50MHZ的频率信号分为小频率输入,实现彩灯的闪烁快慢,进一步了解可编程程序的编写,熟用可编程的基本语句,能够独立思考并且完成一个的方案。

要求:1、要有4种花型变化2、多种花型可以自动变换、循环往复3、彩灯的快慢可以选择4、具有清零的开关二、实验方案设计及其原理经过对问题的分析和初步的整体思考,拟定以下方案:先将信号进行多次分频,以便使得彩灯的节奏可以选择,再用两个开关控制得到的四个频率,接着进行花型选择.第一次分出的频率为20HZ,第二次为10HZ,第三次为5HZ,第四次为0.5HZ;花型变换第一种:红灯先逐一亮起,接着是黄灯,最后是绿灯。

第二种:先依次亮前两盏红灯、黄灯、绿灯,再依次亮后面的两盏。

第三种:依次亮起四盏红灯、黄灯、绿灯。

第四种:亮起首尾的两盏红灯,中间的两盏黄灯,首尾的两盏绿灯,再中间的两盏红灯,首尾的两盏黄灯,中间的两盏绿灯。

三、硬件要求主芯片EPM240T100C5,3个开关,12个具有红黄绿的灯。

四、源程序和下载结果1.源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity caideng isport(rst,clk:in std_logic;speed:in std_logic_vector(0 to 1);r:out std_logic_vector(0 to 3);red,y,g:out std_logic);end;architecture one of caideng issignal d:integer range 0 to 26;signal clk1,clk2,clk3,clk4:std_logic; signal w:std_logic;beginprocess(clk)variable cnt1:integer range 0 to 1000; variable cnt2:integer range 0 to 1250; beginif clk'event and clk='1' thenif cnt1=1000 thencnt1:=0;if cnt2=1250 thencnt2:=0;clk1<=not clk1;elsecnt2:=cnt2+1;end if;elsecnt1:=cnt1+1;end if;end if;end process;process(clk1)variable cnt1:integer range 0 to 1; beginif clk1'event and clk1='1' then if cnt1=1 thencnt1:=0;clk2<=not clk2;elsecnt1:=cnt1+1;end if;end if;end process;process(clk2)variable cnt1:integer range 0 to 1; beginif clk2'event and clk2='1' then if cnt1=1 thencnt1:=0;clk3<=not clk3;elsecnt1:=cnt1+1;end if;end if;end process;process(clk3)variable cnt1:integer range 0 to 5; beginif clk3'event and clk3='1' thenif cnt1=5 thencnt1:=0;clk4<=not clk4;elsecnt1:=cnt1+1;end if;end if;end process;process(speed)begincase speed iswhen "00"=>w<=clk1;when "01"=>w<=clk2;when "10"=>w<=clk3;when "11"=>w<=clk4;end case;end process;process(w)beginif w'event and w='1' thenif d=26 thend<=0;else d<=d+1;end if;end if;end process;process(rst,d)variable r1:std_logic_vector(0 to 3); variable red1,y1,g1:std_logic; beginif rst='0' thenr1:="1111";red1:='0';y1:='0';g1:='0';elsecase d iswhen 0=>r1:="0111";red1:='1';y1:='0';g1:='0';when 1=>r1:="1011";red1:='1';y1:='0';g1:='0';when 2=>r1:="1101";red1:='1';y1:='0';g1:='0';when 3=>r1:="1110";red1:='1';y1:='0';g1:='0';when 4=>r1:="0111";red1:='0';y1:='1';g1:='0';when 5=>r1:="1011";red1:='0';y1:='1';g1:='0';when 6=>r1:="1101";red1:='0';y1:='1';g1:='0';when 7=>r1:="1110";red1:='0';y1:='1';g1:='0';when 8=>r1:="0111";red1:='0';y1:='0';g1:='1';when 9=>r1:="1011";red1:='0';y1:='0';g1:='1';when 10=>r1:="1101";red1:='0';y1:='0';g1:='1';when 11=>r1:="1110";red1:='0';y1:='0';g1:='1'; --一种亮法when 12=>r1:="0011";red1:='1';y1:='0';g1:='0';when 13=>r1:="0011";red1:='0';y1:='1';g1:='0';when 14=>r1:="0011";red1:='0';y1:='0';g1:='1';when 15=>r1:="1100";red1:='0';y1:='0';g1:='1';when 16=>r1:="1100";red1:='0';y1:='1';g1:='0';when 17=>r1:="1100";red1:='1';y1:='0';g1:='0'; --二种亮法when 18=>r1:="0000";red1:='1';y1:='0';g1:='0';when 19=>r1:="0000";red1:='0';y1:='1';g1:='0';when 20=>r1:="0000";red1:='0';y1:='0';g1:='1'; --三种亮法when 21=>r1:="0110";red1:='1';y1:='0';g1:='0';when 22=>r1:="1001";red1:='0';y1:='1';g1:='0';when 23=>r1:="0110";red1:='0';y1:='0';g1:='1';when 24=>r1:="1001";red1:='1';y1:='0';g1:='0';when 25=>r1:="0110";red1:='0';y1:='1';g1:='0';when 26=>r1:="1001";red1:='0';y1:='0';g1:='1'; --四种亮法end case;end if;r<=r1;red<=red1;y<=y1;g<=g1;end process;end;2.下载结果灯按照前面所示的花型进行亮着,并通过其中两个控制频率大小的开关(speed)可以进行控制灯闪烁的快慢,清零信号端(rst)可以执行所需要的要求,即当rst为1时,灯会按照所编写程序的要求运作。

《EDA技术》课程实验报告学生姓名:所在班级:电信1001指导教师:记分及评价:一、实验名称实验8:花样彩灯控制器的设计二、任务及要求【基本部分】5分1、在QuartusII平台上,采用文本输入设计方法,通过编写VHDL语言程序,设计一花样彩灯控制器,实现对实验箱8个LED发光二极管的显示控制,至少4种以上的花样。

2、实验箱上选择恰当的模式进行验证,目标芯片为ACEX1K系列EP1K30TC144-3。

【发挥部分】5分实现不同的花样播放不同的背景音乐的功能。

三、实验程序【基本部分】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CECAIDENG ISPORT(CLK,RST:IN STD_LOGIC;SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END CECAIDENG;ARCHITECTURE COLOR OF CECAIDENG ISTYPE STATE_1 IS(S0,S1,S2,S3,S4,S5,S6,S7);SIGNAL STATE_2:STATE_1;BEGINPR_1:PROCESS(CLK,RST)BEGINIF RST='1'THEN STATE_2<=S0;ELSIF(CLK'EVENT AND CLK='1')THENCASE STATE_2 ISWHEN S0=> STATE_2 <=S1;WHEN S1=> STATE_2 <=S2;WHEN S2=> STATE_2 <=S3;WHEN S3=> STATE_2 <=S4;WHEN S4=> STATE_2 <=S5;WHEN S5=> STATE_2 <=S6;WHEN S6=> STATE_2 <=S7;WHEN S7=> STATE_2 <=S0;END CASE;END IF;END PROCESS PR_1;PR_2:PROCESS(SEL,STATE_2)BEGINIF SEL="000"THEN CASE STATE_2 ISWHEN S0=> Y <="10000000";WHEN S1=> Y <="01000000";WHEN S2=> Y <="00100000";WHEN S3=> Y <="00010000";WHEN S4=> Y <="00001000";WHEN S5=> Y <="00000100";WHEN S6=> Y <="00000010";WHEN S7=> Y <="00000001";END CASE;ELSIF SEL="001" THENCASE STATE_2 ISWHEN S0=> Y <="10000000";WHEN S1=> Y <="11000000";WHEN S2=> Y <="11100000";WHEN S3=> Y <="11110000";WHEN S4=> Y <="11111000";WHEN S5=> Y <="11111100";WHEN S6=> Y <="11111110";WHEN S7=> Y <="11111111";END CASE;ELSIF SEL="010" THENCASE STATE_2 ISWHEN S0=> Y <="10000001";WHEN S1=> Y <="01000010";WHEN S2=> Y <="00100100";WHEN S3=> Y <="00011000";WHEN S4=> Y <="00100100";WHEN S5=> Y <="01000010";WHEN S6=> Y <="10000001";WHEN S7=> Y <="11111111";END CASE;ELSIF SEL="011" THENWHEN S0=> Y <="00000000"; WHEN S1=> Y <="11111111"; WHEN S2=> Y <="00000000"; WHEN S3=> Y <="11111111"; WHEN S4=> Y <="00000000"; WHEN S5=> Y <="11111111"; WHEN S6=> Y <="00000000"; WHEN S7=> Y <="11111111"; END CASE;ELSIF SEL="100" THENCASE STATE_2 ISWHEN S0=> Y <="10000001"; WHEN S1=> Y <="11000011"; WHEN S2=> Y <="11100111"; WHEN S3=> Y <="11111111"; WHEN S4=> Y <="00100100"; WHEN S5=> Y <="11000011"; WHEN S6=> Y <="10000001"; WHEN S7=> Y <="11111111"; END CASE;ELSIF SEL="101" THENCASE STATE_2 ISWHEN S0=> Y <="10000000"; WHEN S1=> Y <="11000000"; WHEN S2=> Y <="11100000"; WHEN S3=> Y <="11110000"; WHEN S4=> Y <="00000001"; WHEN S5=> Y <="00000011"; WHEN S6=> Y <="00000111"; WHEN S7=> Y <="00001111"; END CASE;ELSIF SEL="110" THENCASE STATE_2 ISWHEN S0=> Y <="11110000"; WHEN S1=> Y <="00001111"; WHEN S2=> Y <="00000000"; WHEN S3=> Y <="11111111"; WHEN S4=> Y <="00001111"; WHEN S5=> Y <="11110000"; WHEN S6=> Y <="11011011"; WHEN S7=> Y <="11111111"; END CASE;ELSIF SEL="111" THENWHEN S0=> Y <="01010101";WHEN S1=> Y <="10101010";WHEN S2=> Y <="00000000";WHEN S3=> Y <="11111111";WHEN S4=> Y <="00100100";WHEN S5=> Y <="11011011";WHEN S6=> Y <="00001111";WHEN S7=> Y <="11111111";END CASE;END IF;END PROCESS PR_2;END COLOR;设计思路:这次实验是采用文本输入设计方法,通过编写VHDL语言程序,设计一花样彩灯控制器,实现对实验箱8个LED发光二极管的显示控制,因为要设计出不同的花样,所以要利用典型摩尔状态机来实现。

用v h d l设计十六路彩灯控制器程序仿真图报告-CAL-FENGHAI.-(YICAI)-Company One1课程设计报告题 目 用VHDL 设计十六路彩灯控制器课 程 名 称 创新电子系统设计 院 部 名 称 信息技术学院 专 业 电子信息工程班 级 08电子信息工程(1)班 学 生 姓 名 学 号 课程设计地点 实验楼 课程设计学时 60学时 指 导 教 师金陵科技学院教务处成绩一、课程设计目的与要求 (4)二、课程设计的题目及内容 (4)三、设计过程 (5)3.1 模块设计 (5)3.2时序制电路模块程序及器件原理图 (7)3.3 显示模块电路程序及器件原理图 (9)3.4 顶出模块设计程序及器件原理图 (11)四、设计结果 (12)(1)仿真波形图 (12)①时序控制模块仿真波形: (12)②显示模块仿真波形: (13)③多路彩灯控制仿真波形: (13)(2)管脚连接对应表 (14)(3)硬件实物图 (14)五、总结 (16)一、课程设计目的与要求“创新电子系统设计”课程是专业教学计划中设置的独立实践环节,其主要目的为加强对学生创新意识、创新精神和创新能力的培养,鼓励和倡导学生积极参加学科竞赛、课外科技和科研活动、创造发明活动和各类社会实践活动,提高学生综合素质,促进学生个性发展。

要求学生能在老师的指导下,自主完成一个较复杂综合电子系统设计与制作的全过程,或者通过参加各类各级和通信、电子相关课外科技活动及竞赛得到真正的实战训练。

二、课程设计的题目及内容题目:用VHDL语言设计十六路彩灯控制器内容:1.设计一个多路彩灯控制器,十六种彩灯能循环变化,有清零开关,可以变化彩灯闪动频率即是可以选择快慢两种节拍。

2.整个系统有三个输入信号,分别为控制快慢的信号OPT,复位清零信号CLR,输出信号是16路彩灯输出状态。

系统框图如:图 2.1.1 系统总体框图3.主要模块组成:时序控制电路模块和显示电路模块,时序控制电路是根据输入信号的设置得到相应的输出信号,并将此信号作为显示电路的时钟信号;显示电路输入时钟信号的周期,有规律的输出设定的六种彩灯变化类型。

湖南科技大学信息与电气工程学院《VHDL语言》课程设计报告题目: VHDL语言课程设计专业:班级:姓名:学号:课程设计任务书一、课程设计的目的:1,通过本次课程设计,熟练掌握MAX-PLUS2的应用,操作,并对VHDL语言的编程做一实践检验,编出程序,并进行仿真,并根据所得仿真图形分析和推断并改进所涉及的程序,让程序在现实生活中得以更贴近的应用。

2,本次操作的命题一是:循环彩灯控制器,本设计的要求是:设计一个循环彩灯控制器,该控制器控制红,绿,黄三个发光管循环点亮。

要求红发光管亮3秒,绿发光管亮2秒,黄发光管亮1秒。

3,本次操作的命题二是:数字显示的秒表,本设计的要求是:设计一块用数码管显示的秒表,能够准确的计时并显示。

最大计时为59秒,最小精确到0.1秒。

二、设计方案的论证:命题一循环彩灯控制器的方案一:在本题中要求控制器可以控制红,绿,黄三个发光管循环点亮,并且要求发光的时间不一样,这样,本质设计思想是循环累加,即时钟信号高电平开始,m值开始累加,CASE m ISWHEN "001"=>dout<="100";WHEN "010"=>dout<="100";WHEN "011"=>dout<="100";WHEN "100"=>dout<="010";WHEN "101"=>dout<="010";WHEN "110"=>dout<="001";WHEN OTHERS=>dout<="111";END CASE;前三个值都将赋值给dout1,也就是红灯发光的三秒,然后两个赋值给绿灯,最后一秒赋值给黄灯。

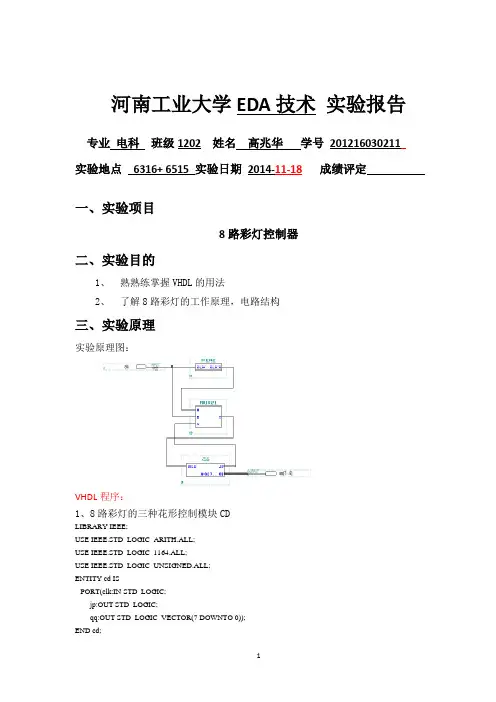

河南工业大学EDA技术实验报告专业电科班级1202 姓名高兆华学号201216030211实验地点6316+ 6515 实验日期2014-11-18成绩评定一、实验项目8路彩灯控制器二、实验目的1、熟熟练掌握VHDL的用法2、了解8路彩灯的工作原理,电路结构三、实验原理实验原理图:VHDL程序:1、8路彩灯的三种花形控制模块CDLIBRARY IEEE;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cd ISPORT(clk:IN STD_LOGIC;jp:OUT STD_LOGIC;qq:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END cd;ARCHITECTURE behav OF cd ISCONSTANT w:INTEGER:=7;SIGNAL q:STD_LOGIC_VECTOR(7 DOWNTO 0); BEGINPROCESS(clk)VARIABLE flag:BIT_VECTOR(2 DOWNTO 0):="000"; VARIABLE jp1: STD_LOGIC:='0';BEGINIF clk'EVENT AND clk='1'THENIF flag="000"THENq<="11"&q(w DOWNTO 2);IF q(2)='1'THENflag:="001";END IF;ELSIF flag="001"THENq<=q(w-2 DOWNTO 0)&"00";IF q(5)='0'THENflag:="010";END IF;ELSIF flag="010"THENq(w DOWNTO 4)<=q(w-2 DOWNTO 4)&"11";q(w-4 DOWNTO 0)<="11"&q(w-4 DOWNTO 2);IF q(2)='1'THENflag:="011";END IF;ELSIF flag="011"THENq(w DOWNTO 4)<="00"&q(w DOWNTO 6);q(w-4 DOWNTO 0)<=q(w-6 DOWNTO 0)&"00";IF q(1)='0'THENflag:="100";END IF;ELSIF flag="100"THENq(w DOWNTO 4)<="11"&q(w DOWNTO 6);q(w-4 DOWNTO 0)<="11"&Q(w-4 DOWNTO 2);IF q(2)='1'THENflag:="101";END IF;ELSIF flag="101"THENq<="00000000";jp1:=NOT jp1;flag:="000";END IF;END IF;qq<=q;jp<=jp1;END PROCESS;END behav;2、二选一多路选择器模块MUX21 library ieee;use ieee.std_logic_1164.all;entity mux21 isport(a,b,s:in std_logic;y:out std_logic);end mux21;architecture ar of mux21 isbeginprocess(a,b,s)beginif s='0'theny<=a;elsey<=b;end if;end process;end ar;3、二分频模块FEN2library ieee;use ieee.std_logic_1164.all;entity fen2 isport(clk:in std_logic;clkk:out std_logic);end fen2;architecture behav of fen2 isbeginprocess(clk)variable clkk1:std_logic:='0';beginif clk'event and clk='1'thenclkk1:=not clkk1;end if;clkk<=clkk1;end process;end behav;四、仿真结果及分析第一个脉冲到来时,q6、q7为高电平,所以连个灯同时点亮,第二个脉冲到来时q5、q4也变为高电平,两个灯也被点亮,一次类推,直到q0、q1变为高电平,第一种花型完成。

实验报告书实验项目名称:彩灯循环控制器的设计实验项目性质:综合性实验所属课程名称:VHDL程序设计实验实验计划学时:4一、实验目的掌握VHDL程序设计方法二、实验内容和要求1)彩灯能够自动循环点亮2)彩灯循环显示且频率快慢可调(可选)。

3)该控制电路具有8路以上输出在软件工具平台上,进行VHDL语言的各模块编程输入、编译实现和仿真验证。

三、实验主要仪器设备和材料计算机四、实验方法、步骤及结构测试1.方案设计与功能描述彩灯的循环是通过clk的计数实现的,当有一个高电平来到的时候,则通过Q=Q+1计数来实现。

当Q的值从“000”逐次加“1”到“111”的时候,通过判断Q的值是否为“111”的时候,进行清“0”,即变为“000”再次重新计数。

那么通过Q的状态值从“000”->“001”->“010” ->“011”->“100” ->“101”->“110” ->“111”->“000”的循环,实现了彩灯的循环。

彩灯的亮灭是通过判断Q的值来选择的,用case_when语句。

对于频率的调节,则是通过timer来控制,由人为的设定timer 的值,通过赋不同的初值来改变频率。

也是通过计数来分频的2.程序代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity light8a isport (clk,en,rst:in std_logic;timer:in std_logic_vector(3 downto 0);a,b,c,d,e,f,g,h:out std_logic);end light8a;architecture one of light8a issignal w:std_logic_vector(3 downto 0);signal couts:std_logic;beginprocess(clk,timer) ----------分频进程variable x : std_logic_vector(3 downto 0):=timer; beginif clk'event and clk='1' thenif x<4 then x:=x+1;else x:=timer;end if;end if;if x="0100" then couts<='1';else couts<='0';end if;end process;process(clk,en,rst,couts) ----------计数循环进程variable Q : std_logic_vector(3 downto 0);beginif rst='0'then Q:=(others=>'0');elsif clk'event and clk='1' thenif couts='1' thenif en='1' thenif Q<8 thenQ:=Q+1;w<=Q;if Q="1000" then Q:=(others=>'0'); -end if;end if;end if;end if;end if;end process;process(w) --------选择灯亮灭,即控制彩灯循环进程begincase w iswhen"0001"=>a<='1';b<='0';c<='0';d<='0';e<='0';f<='0';g<='0';h<='0'; when"0010"=>a<='0';b<='1';c<='0';d<='0';e<='0';f<='0';g<='0';h<='0'; when"0011"=>a<='0';b<='0';c<='1';d<='0';e<='0';f<='0';g<='0';h<='0'; when"0100"=>a<='0';b<='0';c<='0';d<='1';e<='0';f<='0';g<='0';h<='0'; when"0101"=>a<='0';b<='0';c<='0';d<='0';e<='1';f<='0';g<='0';h<='0'; when"0110"=>a<='0';b<='0';c<='0';d<='0';e<='0';f<='1';g<='0';h<='0'; when"0111"=>a<='0';b<='0';c<='0';d<='0';e<='0';f<='0';g<='1';h<='0'; when"1000"=>a<='0';b<='0';c<='0';d<='0';e<='0';f<='0';g<='0';h<='1'; when others=>null;end case;end process;end architecture one;4仿真分析当设定timer的值为1的时候,仿真图如下:当设定timer的值为3的时候,仿真图如下:通过仿真可知,timer可以控制频率快慢,且彩灯a,b,c,d,e,f,g,h能循环点亮5总结:通过这次是上机实验,进一步的巩固了我的VHDL的知识,基本掌握了VHDL的编程方法等。

一、实训目的本次实训旨在通过学习花样彩灯的设计与制作,提高学生的电子设计能力和实践操作技能。

通过对单片机、电路设计、编程等方面的学习,让学生掌握花样彩灯的设计原理、制作方法和实际应用,为今后从事电子设计和相关领域工作打下坚实基础。

二、实训内容1. 花样彩灯设计原理(1)彩灯种类:本次实训主要涉及LED彩灯,其具有体积小、亮度高、色彩丰富、寿命长等优点。

(2)电路设计:根据设计需求,设计电路原理图,包括单片机、驱动电路、电源电路等。

(3)编程:编写单片机程序,实现彩灯的控制,如循环显示、闪烁、呼吸灯等效果。

2. 花样彩灯制作(1)元器件准备:根据电路设计,准备所需的元器件,如LED灯珠、电阻、电容、单片机等。

(2)焊接:按照电路原理图,进行元器件的焊接,确保焊接质量。

(3)调试:在彩灯电路搭建完成后,进行调试,确保彩灯能正常工作。

三、实训过程1. 学习单片机基础知识了解单片机的结构、工作原理、编程方法等,为后续设计打下基础。

2. 学习电路设计原理学习电路元件的特性、电路分析方法、电路设计方法等,掌握电路设计的基本技能。

3. 学习编程语言学习C语言编程,掌握单片机编程的基本方法,为编写彩灯程序做准备。

4. 设计花样彩灯根据设计要求,设计彩灯电路原理图,并编写单片机程序,实现彩灯的循环显示、闪烁、呼吸灯等效果。

5. 制作与调试根据电路原理图,制作彩灯电路,并进行调试,确保彩灯能正常工作。

四、实训成果1. 完成花样彩灯电路设计,包括电路原理图、PCB布线图等。

2. 编写单片机程序,实现彩灯的循环显示、闪烁、呼吸灯等效果。

3. 制作完成花样彩灯,并进行展示。

五、实训心得1. 通过本次实训,我对单片机、电路设计、编程等方面的知识有了更深入的了解,提高了自己的实践操作能力。

2. 在设计过程中,学会了如何根据需求进行电路设计,以及如何编写程序实现彩灯效果。

3. 实训过程中,遇到了许多问题,通过与同学和老师的交流,逐一解决了这些问题,提高了自己的解决问题的能力。

实验一彩灯实验

一、实验目的

1 通过实验初步了解EDA的基本概念。

2 能理解VHDL语言实现硬件设计的思路。

3 能熟练掌握EDA开发软件的使用。

二、实验原理

在本实验中,8个彩灯共阴接地,阳极分别为FPGA的8个I/O相连,I/O输出变化的电平,来控制彩灯的点亮。

三、实验内容与步骤

1 打开Quartus II软件,依次点击菜单栏中的“File-Open Project”,打开EDA/LIGHT文件夹,在对话框中选择项目LIGHT,再点击打开即可;

2 双击项目管理器中的顶层项目LIGHTALL,顶层文件打开;

3 分别双击原理图表中PIN1HZ、light模块,打开即可看到源文件:

(1)light模块源程序

light模块方针波形如图所示:

程序分析:

(2)PIN1HZ模块源程序

PIN1HZ模块方针波形如图所示:

程序分析:

4 重新设置器件Cyclone EP1C6Q240C8 和配置芯片EPCS1;

5 根据配套的硬件资源分配表进行管脚分配,分配后的结果如图所示:

6 然后再编译一次;

7 下载程序到目标芯片。

四、实验现象

八个彩灯采用不同的模式被点亮。

五、思考题

试着改变程序,使得LED灯的切换速度发生变化。

只要改变PIN1HZ模块源程序的分频比,即可使得LED灯的切换速度发生变化。

例如,把50MHz分频为2Hz的程序如下:。

可编程逻辑器件应用项目报告书项目名称:花样彩灯指导老师:姓名:学号:班级:广东水利电力职业技术学院(以后写报告要包含以下一些内容:)一、设计要求--------------------------------------------------------------------------------二、设计目的--------------------------------------------------------------------------------三、设计方案--------------------------------------------------------------------------------四、设计程序---------------------------------------------------------------------------------五、管脚分配---------------------------------------------------------------------------------六、硬件下载实现现象描述------------------------------------------七、体会、对设计工作的总结与展-------------------------------------------一、设计要求:要求设计一个8路彩灯控制器,能控制8路彩灯按照两种节拍、三种花型循环变化。

两种节拍分别为0.25s和0.5s。

三种花型分别是:①8路彩灯从左至右按次序渐亮,全亮后逆次序渐灭。

②从中间到两边对称的渐亮,全亮后仍由中间向两边逐次渐灭。

③8路彩灯分成两半,从左至右顺次渐亮,全亮后则全灭。

二、设计方案:(1)、采用状态机的方式,用点阵在硬件上实现各种花形彩灯,并使用复位键(2)、用0.25s和0.5s两种频率的选择,并采用按键控制输出(3)、对于点阵的扫描是采用了1s三、程序语言:LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;USE IEEE.std_logic_ARITH.ALL;USE IEEE.std_logic_UNSIGNED.ALL;----------------------------------------------------ENTITY caideng ISport(clk,rst:INstd_logic; ---------------12-------------- aj:in std_logic;-------------频率选择30Light:out std_logic_vector(7 downto 0);------点阵列-----(82-73)hang:out std_logic_vector(7 downto 0) -------------(90-83));end caideng;architecture one of caideng istype states is(s0,s1,s2,s3,s4);------表示状态------signal state: states;signal clk_hz,clk_1s:std_logic:='0';signal cnt1:std_logic_vector(3 downto 0):="0000";signal cnt2:std_logic_vector(2 downto 0):="000";signal cnt3:std_logic_vector(2 downto 0):="000";signal cnt4:std_logic_vector(2 downto 0):="000";signal cnt5:std_logic_vector(3 downto 0):="0000";BEGINhang<="11111111";--------------------频率选择-----------------process(clk)variable cnt1:integer range 0 to 6250000;------------4hz 即0.25svariable cnt2:integer range 0 to 12500000;------------2hz即0.5sbeginif clk'event and clk='1' thencase aj is--------------------拨码按键控制2种频率的输出when '0' =>if cnt1=6250000 thencnt1:=0;clk_hz <=not clk_hz;elsecnt1:=cnt1+1;end if;when '1' =>if cnt2=12500000 thencnt2:=0;clk_hz <=not clk_hz;elsecnt2:=cnt2+1;end if;when others =>null;end case;end if;end process;--------------------------------------------------------- process(clk)variable cnt1: integer range 0 to 20000; variable cnt2: integer range 0 to 10000; beginif clk'event and clk='1' thenif cnt1=20000 thencnt1:=0;if cnt2=10000 thencnt2:=0;clk_1s<=not clk_1s;elsecnt2:=cnt2+1;end if;elsecnt1:=cnt1+1;end if;end if;end process;process(rst,clk_hz)beginif(rst='0')thenstate<=s0;elsif(clk_1s'EVENT AND clk_1s='1')then case state iswhen s0 => state <=s1;when s1 => state <=s2;when s2 => state <=s3;when s3 => state <=s4;when s4 => state <=s0;end case;end if;end process;---------------------------------------------------------- process(state,clk_hz)beginif rst='0' thenlight<="00000000";elseif(clk_hz'EVENT AND clk_hz='1')then case state iswhen s0=>if cnt1="1111" thencnt1<="0000";elsecnt1<= cnt1+1;end if;case cnt1 iswhen "0000"=>light<="01111111";when "0001"=>light<="00111111";when "0010"=>light<="00011111";when "0011"=>light<="00001111";when "0100"=>light<="00000111";when "0101"=>light<="00000011"; when "0110"=>light<="00000001";when "0111"=>light<="00000000";when "1000"=>light<="00000000";when "1001"=>light<="00000001"; when "1010"=>light<="00000011";when "1011"=>light<="00000111";when "1100"=>light<="00001111";when "1101"=>light<="00011111";when "1110"=>light<="00111111";when others=>light<="01111111"; end case;when s1=>if cnt2="111" thencnt2<="000";else cnt2<= cnt2+1;end if;case cnt2 iswhen "001"=>light<="11000011"; when "010"=>light<="10000001"; when "011"=>light<="00000000"; when "100"=>light<="00000000"; when "101"=>light<="10000001"; when "110"=>light<="11000011"; when others=>light<="11100111"; end case;when s2=>if cnt3="111" thencnt3<="000";else cnt3<=cnt3+1;end if;case cnt3 iswhen "000"=>light<="01110111"; when "001"=>light<="00110011"; when "010"=>light<="00010001"; when "011"=>light<="00000000"; when "100"=>light<="10000001"; when "101"=>light<="11000011"; when "110"=>light<="11100111";when others=>light<="00000000"; end case;when s3=>if cnt4="100" thencnt4<="000";else cnt4<= cnt4+1;end if;case cnt4 iswhen "000"=>light<="01110111"; when "001"=>light<="00110011"; when "010"=>light<="00010001"; when "011"=>light<="00000000"; when "100"=>light<="11111111"; when others=>light<="00000000"; end case;when s4=>if cnt5="1111" thencnt5<="0000";else cnt5<=cnt5+1;end if;case cnt5 iswhen "0000"=>light<="10000000";when "0001"=>light<="01000000";when "0010"=>light<="00100000";when "0011"=>light<="00010000";when "0100"=>light<="00001000";when "0101"=>light<="00000100";when "0110"=>light<="00000010";when "0111"=>light<="00000100";when "1000"=>light<="00001000";when "1001"=>light<="00010000";when "1010"=>light<="00100000";when "1011"=>light<="01000000";when "1100"=>light<="10000000";when others=>light<="00000000";end case;end case;end if;end if;end process;end one;四、管脚分配五、硬件下载实现现象描述硬件上的实现是有两种频率,分别是0.25s和0.5s,总共有5种花形——(1)点阵从左至右按次序渐亮,全亮后逆次序渐灭;(2)从中间到两边对称的渐亮,全亮后仍由中间向两边逐次渐灭;(3)8路彩灯分成两半,从左至右顺次渐亮,全亮后则全灭;(4)分成两半,从左至右顺次渐亮,然后从右至左逆次渐灭;六:体会、对设计工作的总结及展望这次的花样彩灯,让我学会了使用状态机编程,清楚了状态机编程的特点,同时对于点阵的了解也更进一步了。

VHDL 彩灯控制电路的设计与实现一、实验目的1.进一步了解时序电路设计方法2.熟悉状态机的设计方法二、实验所用仪器及元器件1、计算机2、直流稳压电源3、数字系统与逻辑设计实验开发板三、实验内容用VHDL语言设计并实现一个彩灯控制(8个发光二极管)电路,仿真并下载验证其功能。

彩灯有两种工作模式,可以通过拨码开关或者按键进行切换。

(1)单点移动模式:一个点在8个发光二极管上来回的亮(2)幕布模式:从中间两个点,同时向两边一次点亮直至全亮,然后再向中间点灭,依次往复四、设计思路与过程根据实验要求,需要实现在拨码开关或者按键的控制下实现两种状态机的转换。

首先,确定输入输出变量:输入:拨码开关a:实现两种模式的转换;时钟clk::提供有效时钟沿;输出:8维向量b:连接8个发光二极管。

其次,确定电路工作状态因为在单点移动模式和幕布模式都要满足灯来回亮,共计工作状态23种:a=0时,实现单点移动模式,工作状态有s0~s13共14种状态;a=1时,实现幕布模式,工作状态有s14~s22共9种状态。

再次,大致确定VHDL编写思路确定好输入输出变量和电路状态后,考虑结构体中需要的进程需要完成以下两个功能——分频和实现状态机,故我使用了4个进程。

其功能分别如下:P0:分频,将实验板上提供的50MHz的时钟信号,即输入clk分为频率为1Hz的低频信号clk_out,以便观察现象;P1:为当前状态储存的下一状态;P2:当时钟有效沿到来时,当前状态转入下一状态;(P1、P2共同实现状态机的转换)P3:控制LED灯的输出,达到实验要求效果具体程序如下。

五、VHDL程序library ieee;use ieee.std_logic_1164.all;entity light isport (clk: in std_logic;a: in std_logic;b:out std_logic_vector(7 downto 0));end light;architecture light_1 of light istype state_type is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15,s16,s17,s18,s19,s20,s21,s22); signal current_state,next_state: state_type;signal clk_out:std_logic;signal tmp: integer range 0 to ;beginp0:process(clk) --分频器,把50MHz的时钟clk分为1Hz的时钟clk_out beginif clk'event and clk='1' thenif tmp= thentmp<=0;elsetmp<=tmp+1;end if;if tmp= thenclk_out<='1';elseclk_out<='0';end if;end if;end process;p1:process(current_state,a) --当前状态在开关函数a作用下所储存的下一状态begincase current_state iswhen s0=> if(a='0') then next_state<=s1;else next_state<=s14; end if;when s1=> if(a='0') then next_state<=s2;else next_state<=s14; end if;when s2=> if(a='0') then next_state<=s3;else next_state<=s14; end if;when s3=> if(a='0') then next_state<=s4;else next_state<=s14; end if;when s4=> if(a='0') then next_state<=s5;else next_state<=s14; end if;when s5=> if(a='0') then next_state<=s6;else next_state<=s14; end if;when s6=> if(a='0') then next_state<=s7;else next_state<=s14; end if;when s7=> if(a='0') then next_state<=s8;else next_state<=s14; end if;when s8=> if(a='0') then next_state<=s9;else next_state<=s14; end if;when s9=> if(a='0') then next_state<=s10;else next_state<=s14; end if;when s10=> if(a='0') then next_state<=s11;else next_state<=s14; end if;when s11=> if(a='0') then next_state<=s12;else next_state<=s14; end if;when s12=> if(a='0') then next_state<=s13;else next_state<=s14; end if;when s13=> if(a='0') then next_state<=s0;else next_state<=s14; end if;when s14=> if(a='1') then next_state<=s15;else next_state<=s0; end if;when s15=> if(a='1') then next_state<=s16;else next_state<=s0; end if;when s16=> if(a='1') then next_state<=s17;else next_state<=s0; end if;when s17=> if(a='1') then next_state<=s18;else next_state<=s0; end if;when s18=> if(a='1') then next_state<=s19;else next_state<=s0; end if;when s19=> if(a='1') then next_state<=s20;else next_state<=s0; end if;when s20=> if(a='1') then next_state<=s21;else next_state<=s0; end if;when s21=> if(a='1') then next_state<=s22;else next_state<=s0; end if;when s22=> if(a='1') then next_state<=s14;else next_state<=s0; end if;end case;end process;p2:process(clk_out) --时钟clk_out作用下的状态转换函数beginif(clk_out'event and clk_out='1') thencurrent_state<=next_state;end if;end process;p3:process(current_state) --当前状态所对应的输出函数begincase current_state iswhen s0=>b<="";when s1=>b<="";when s2=>b<="";when s3=>b<="";when s4=>b<="";when s5=>b<="";when s6=>b<="";when s7=>b<="";when s8=>b<="";when s9=>b<="";when s10=>b<="";when s11=>b<="";when s12=>b<="";when s13=>b<="";when s14=>b<="";when s15=>b<="";when s16=>b<="";when s17=>b<="";when s18=>b<="";when s19=>b<="";when s20=>b<="";when s21=>b<="";when s22=>b<="";end case;end process;end light_1;六、仿真波形说明:为了仿真需要,在进行仿真事,将分频部分p0去掉,直接用clk作用进程p2 其中:End time=2msa period time=60usclk period time=2us七、故障及问题分析本次实验整体比较顺利,但仍旧出现了几个问题:开始并未设置分频器,clk的频率为50MHz,这个频率过高,若是直接用于提供时钟,不但不能看清现象,还会因为周期过短(可能会短于电路的延迟时间),导致输出错误。