基于MSI芯片74160设计模为100的计数器

- 格式:doc

- 大小:995.00 KB

- 文档页数:14

用74160集成计数器构成任意进制计数器的电路设计单嵛琼;单长吉【摘要】74160 is die for 10 synchronous counter addition,take advantage of its reset and the number of pre-set function can make mould for any number of counters.So as to solve the problem that we can't buy any kind of counter.%74160是模为10的同步加法计数器,利用它的清零和预置数功能可以构成模为任意数的计数器,从而解决了我们需要计数器但市场上又买不到这种计数器的困难。

【期刊名称】《大学物理实验》【年(卷),期】2016(029)003【总页数】3页(P15-17)【关键词】计数器;清零;置数;有效状态【作者】单嵛琼;单长吉【作者单位】昭通学院,云南昭通 657000;昭通学院,云南昭通 657000【正文语种】中文【中图分类】O453市场上能买到的集成计数器芯片一般为4位二进制计数器和十进制计数器,如果需要其它进制计数器,可用现有的4位二进制计数器和十进制计数器芯片进行设计。

74160是8421BCD码同步加法十进制计数器,可以用它来构成任意进制计数器。

74160是8421BCD码同步加法计数器[1-2],图1是它的逻辑符号:是清零端,端是预置数端,EP、ET是两个使能端,CP端是时钟脉冲端,RCO是进位输出端,D3、D2、D1、D0是四个预置数据输入端,Q3、Q2、Q1、Q0是四个数据输出端。

其中进位输出端的逻辑表达式为[3]:RCO=ET·Q3·Q1。

由表1可知,74160具有异步清零、同步置数、计数和保持的功能。

用74160构成模小于10的计数器的计数器时通常有两种方法:异步清零法和同步置数法[4].文章中选取用74160构成五进制计数器来说明这两种方法的应用。

74160是一种4位可编程同步计数器,可以实现计数器的功能。

该计数器有四个并行输入,包括清零输入、时钟输入、并行加载输入和输出控制输入,以及四个异步输出,可以用来控制其他数字电路的工作。

74160计数器的功能表如下:Q1111 0 1 0 1 0 1 0 1 DQ其中,CP表示计数器的时钟输入,MR表示清零输入,PL 表示并行加载输入,PE表示输出控制输入,Q3、Q2、Q1、Q0表示计数器的异步输出,D3、D2、D1、D0表示并行加载时的输入数据。

在计数器工作时,当CP为高电平时,计数器会按照以下顺序依次输出Q0、Q1、Q2、Q3,直到计数器的计数值达到15,然后重新从0开始计数。

当MR为高电平时,计数器会被清零,输出恢复为0000。

当PL为高电平时,计数器的输出值会被设置为输入的值,即将D0-D3设置为需要的计数值。

当PE 为高电平时,计数器的输出被锁定,不再计数,而是输出锁存的计数值。

74160计数器的原理是基于 JK 触发器实现的。

每个 JK 触发器可以存储两个比特位的信息,其中 J 和 K 输入控制着触发器的输出状态,而时钟输入用于时序控制。

在计数器中,每个JK 触发器的输出被连接到下一个JK 触发器的时钟输入上,形成一个级联的 JK 触发器网络。

当 CP 为高电平时,时钟信号被传递到每个 JK 触发器的时钟输入,使得计数器的计数值递增。

当计数值达到15时,所有 JK 触发器的输出都变为0,计数器重新从0开始计数。

在并行加载模式下,输入数据被加载到 JK 触发器中,从而可以设置计数器的初始值。

在输出控制模式下,PE 为高电平时,计数器的输出被锁定,不再计数,而是输出锁存的计数值。

附录一:基于原理图的模100BCD码计数器的设计1目的:1)练习用原理图输入设计;2)如何用数码管和二极管显示设计;3)如何仿真;4)如何绑定管脚。

2过程2.1新建原理图文件。

点击file->new->block diagram file->OK,如图2-1,图2-2,出现图2-3。

图2-1 新建文件。

点击file->new。

图2-2 新建原理图文件。

点击block diagram file->OK。

图2-3. 原理图设计输入区域。

双击工作区域。

图2-4 宏单元输入界面。

点击Library下的+。

图2-5 选用宏单元。

键入74160。

2.2 输入设计。

双击图2-3的工作区,出现图2-4。

在+megafunctions,+others,+primitives中寻找需要的宏单元。

也可在Name下输入知道名字的宏单元,如“74160”,“GND”,“VCC”等,如图2-5。

输入设计,如图2-6。

存盘为m100_jishuqi,如图2-7。

图2-6 模100BCD码计数器。

图2-7 保存文件。

2.2为本设计建立工程,并放在文件夹..\m100_jishuqi\中。

在图2-7中点击是(或点击file->newproject)出现图2-8;点击next,出现图2-9;输入工程名字和顶层设计名字;点击next,出现图2-10,加入设计文件;点击next,出现图2-11,选择器件(cycloneII系列EP2C70F896C6);点击next->next->finish。

图2-8 新建工程。

点击Next。

图2-9 输入工程名字和顶层设计名字:mo100_jishuqi。

图2-10 把设计文件加入工程。

图2-11 选择器件:cycloneII系列EP2C70F896C6。

2.3把FPGA没有用到的引脚设定为 as input tri-stated。

点击assignment->device,如图2-12;点击Device and Pin Options,如图2-13所示,把Unused Pins设定为as input tri-stated。

用74160集成计数器构成任意进制计数器的电路设计

要用74160集成计数器构成任意进制计数器的电路设计,首先需要确定所需计数的进制数。

以六进制计数器为例,74160是一个四位计数器,可以用来计

数0-15的数字。

六进制计数器需要计数0-5的数字,所以要

将74160的计数范围从0-15映射到0-5。

假设计数器的输出为ABCDEF,其中A、B、C、D分别表示

四个位的输出。

为了将0-15映射到0-5,可以使用以下逻辑门

电路:

1. 将A和B连接到一个与门中,输出X1。

2. 将A、B、C和D连接到一个或门中,输出X2。

3. 将X1和X2连接到一个非门中,输出X3。

4. 将X3反馈到计数器的复位输入端。

这样设计的电路可以实现六进制的计数功能。

每当计数达到5时,X3输出为高电平,触发计数器复位,重新从0开始计数。

以上是以六进制为例的电路设计方法,其他进制的计数器可以采用类似的思路,只需根据进制数来确定与门和或门的输入组合和连接方式。

74ls160芯片工作原理

74LS160芯片是一种二进制同步计数器,用于计数和存储二进制数据。

它是一种高性能、低功耗的集成电路,广泛应用于数字电子设备中。

该芯片采用JK触发器实现计数功能。

它有四个独立的计数器,每个计数器都可以计数到十六进制的十五。

当计数器达到十五时,它会自动复位为零,重新开始计数。

74LS160芯片的工作原理是基于时钟信号的输入。

当时钟信号上升沿到达时,计数器会根据输入的控制信号进行计数操作。

控制信号可以是一个外部信号,也可以是其他计数器的输出信号。

除了计数功能,74LS160芯片还具有存储功能。

它可以将当前计数器的值存储在内部存储器中,并在需要时读取出来。

这使得它可以在计数过程中暂停和恢复计数操作。

该芯片的工作电压范围为4.75V至5.25V,工作温度范围为0°C至70°C。

它具有快速的响应时间和稳定的性能,适用于各种数字电路应用。

74LS160芯片是一种可靠且灵活的计数器,具有高性能和低功耗的特点。

它在数字电子设备中发挥着重要的作用,为我们提供了方便和可靠的计数和存储功能。

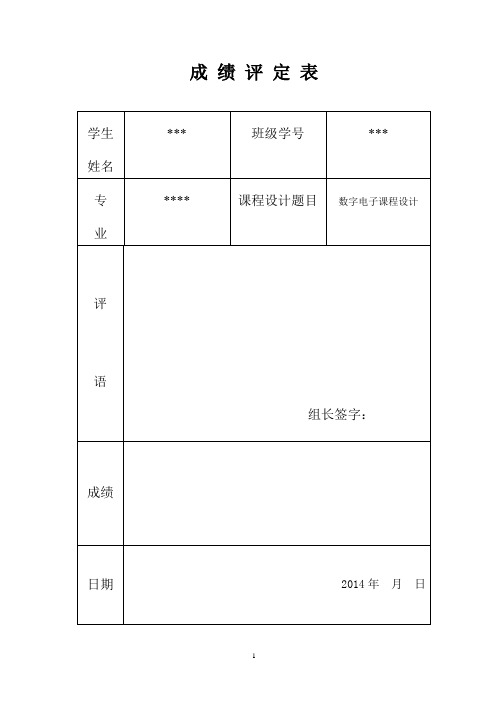

成绩评定表学生*** 班级学号***姓名**** 课程设计题目数字电子课程设计专业评语组长签字:成绩日期 2014年月日课程设计任务书学院*** 专业***学生姓名** 班级学号**课程设计题目1、六进制同步减法计数器(无效态:001,101)2、基于74163芯片仿真设计24进制加法计数器并显示计数过程实践教学要求与任务:1)采用实验箱设计、连接、调试三位二进制计数器。

2)采用实验箱设计、连接、调试串行序列检测器。

3)采用multisim 仿真软件建立复杂的计数器电路模型;4)对电路进行理论分析;5)在multisim环境下分析仿真结果,给出仿真时序图;6)撰写课程设计报告。

工作计划与进度安排:第1天:1. 布置课程设计题目及任务。

2. 查找文献、资料,确立设计方案。

第2-3天:在实验室中设计、连接、调试三位二进制计数器及串行序列检测器电路。

第4天:1. 安装multisim软件,熟悉multisim软件仿真环境。

在multisim环境下建立电路模型,学会建立元件库。

2. 对设计电路进行理论分析、计算。

3. 在multisim环境下仿真电路功能,修改相应参数,分析结果的变化情况。

第5天:1. 课程设计结果验收。

2. 针对课程设计题目进行答辩。

3. 完成课程设计报告。

指导教师:袁凤莲2014年月日专业负责人:2014年月日学院教学副院长:2014 年月日目录1.课程设计的目的与作用 (4)2.设计任务 (4)2.1.六进制同步减法计数器(无效态:001,101) (5)2.2、串行序列检测器的设计(检测序列101011) (5)2.3.基于74163芯片仿真设计24进制加法计数器并显示计数过程 (5)3 multisim软件环境介绍 (5)4数据处理 (5)4.1六进制同步减法计数器(无效态:001,101)的数据处理 (5)4.1.1状态图 (6)4.1.2 求输出方程 (7)4.1.3卡诺图 (7)4.1.4状态方程和驱动方程 (8)4.1.5时钟方程 (8)4.1.6电路图 (8)4.1.7检查自启动 (9)4.2串行序列检测器的设计(发生序列101011) (9)4.2.1基本原理 (9)4.2.2系统设计框图 (9)4.2.3理论分析及计算 (10)4.2.4运行结果分析 (10)4.2.5电路图 (11)4.3基于74163芯片仿真设计24进制加法计数器并显示计数过程 (11)4.3.1利用同步置数端获得24进制计数器 (12)4.3.2求归零逻辑--同步置数端控制信号的逻辑表达式 (13)4.3.3电路图 (13)5 仿真结果分析 (13)5.1六进制同步减法计数器(无效态:001,101) (13)5.1.1结果分析 (13)5.1.2仿真结果 (14)5.2串行序列检测器的设计(检测序列101011) (15)5.2.1结果分析 (15)5.2.2仿真结果 (15)5.3.基于74163芯片仿真设计24进制加法计数器并显示计数过程 (17)5.3.1结果分析 (17)5.3.2仿真结果 (17)6 设计总结 (18)7 参考文献 (18)1.课程设计的目的与作用(1)巩固所学的相关理论知识;(2)实践所掌握的电子制作技能;(3)会运用Multisim工具对所作出的理论设计进行模拟仿真测试,进一步完善理论设计;(4)通过查阅手册和文献资料,熟悉常用电子器件的类型和特性,并掌握合理选用元器件的原则;(5)掌握模拟电路的安装\测量与调试的基本技能,熟悉电子仪器的正确使用方法,能力分析实验中出现的正常或不正常现象(或数据)独立解决调试中所发生的问题;(6)学会撰写课程设计报告;(7)培养实事求是,严谨的工作态度和严肃的工作作风;(8)完成一个实际的电子产品,提高分析问题、解决问题的能力。

74LS160 芯片同步十进制计数器(直接清零)·用于快速计数的内部超前进位·用于n 位级联的进位输出·同步可编程序·有置数控制线·二极管箝位输入·直接清零·同步计数本电路是由4 个主从触发器和用作除2计数器及计数周期长度为除5的3位2进制计数器所用的附加选通所组成。

有选通的零复位和置9输入。

为了利用本计数器的最大计数长度(十进制),可将B输入同QA 输出连接,输入计数脉冲可加到输入A上,此时输出就如相应的功能表上所要求的那样。

LS90可以获得对称的十分频计数,办法是将QD 输出接到A输入端,并把输入计数脉冲加到B输入端,在QA输出端处产生对称的十分频方波。

74160引脚图交流波形图:图1 时钟到输出延迟计数图2 主复位输出延迟,主复位时钟频率,脉冲宽度脉冲宽度,和主复位恢复时间状态图VHDL十进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity count10 isport (clk:in std_logic;f:buffer integer range 0 to 15;cout:out std_logic);end;architecture aa of count10 isbeginprocess(clk)beginif falling_edge(clk) thenif f=9 thenf<=0;cout<='1';elsef<=f+1;end if;elsenull;end if;end process;end;十进制计数器VHDLlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--**************实体*****************entity shijinzhi isport(clk: in std_logic;reset: in std_logic;s : out std_logic_vector(5 downto 0);out1: out std_logic_vector(7 downto 0));end shijinzhi;--*****************结构体***********************architecture one of shijinzhi issignal clk_500 : std_logic;--扫描时钟signal clk_1 : std_logic;--1s时钟begin--*************500Hz分频程序********************process(clk)variable cnt1 : integer range 0 to 200;variable cnt2 : integer range 0 to 250;beginif clk'event and clk='1' thenif cnt1=200 thencnt1:=0;if cnt2=250 thencnt2:=0;clk_500<=not clk_500;elsecnt2:=cnt2+1;end if;elsecnt1:=cnt1+1;end if;end if;end process;--***********1Hz分频程序和扫描信号产生********************process(clk_500)variable cnt3 : integer range 0 to 250;beginif clk_500'event and clk_500='1' thenif cnt3=250 thencnt3:=0;clk_1<=not clk_1;elsecnt3:=cnt3+1;end if;end if;end process;--****************************************process(clk_1,reset)variable count1:integer range 0 to 9;beginif reset='0' then count1:=0;elsif clk_1'event and clk_1='1' thenif count1=9 thencount1:=0;elsecount1:=count1+1;end if;end if;if clk_500='1' thencase count1 isWHEN 0 =>s<="111110";out1<="10111111";WHEN 1 =>s<="111110";out1<="10000110";WHEN 2 =>s<="111110";out1<="11011011";WHEN 3 =>s<="111110";out1<="11001111";WHEN 4 =>s<="111110";out1<="11100110";WHEN 5 =>s<="111110";out1<="11101101";WHEN 6 =>s<="111110";out1<="11111101";WHEN 7 =>s<="111110";out1<="10000111";WHEN 8 =>s<="111110";out1<="11111111"; WHEN 9 =>s<="111110";out1<="11101111";when others=>out1<="00000000";end case;end if;end process;end one;。

multisim建立100进制计数器步骤Multisim是一款非常流行的电路仿真软件,它可以帮助我们快速地设计各种电路并模拟其工作过程。

在实际的电路设计中,计数器经常被使用。

100进制计数器可以实现对0~99的数字进行计数和展示。

下面我们将介绍如何通过Multisim来建立一个简单的100进制计数器。

首先,我们需要打开Multisim软件并新建一个电路图。

在新建电路图的界面中,我们可以选择“文件”->“新建”->“电路图”来创建一个新的电路图文件。

创建好之后,我们就可以开始设计我们的计数器电路了。

第一步,我们需要选择适当的计数器芯片。

在Multisim中,我们可以直接从工具栏中拖拽各种芯片模块到电路图中。

我们需要选择一个100进制的计数器芯片,比如CD4017。

将CD4017拖拽到电路图中。

第二步,我们需要为芯片提供合适的时钟输入。

在Multisim中,我们可以在工具栏中找到各种电子元器件,包括时钟发生器。

我们需要将一个合适的时钟发生器拖拽到电路图中,然后将输出连接到计数器的时钟输入端口上。

第三步,我们需要将计数器的输出连接到适当的显示器上,以展示当前计数器的计数值。

在Multisim中,我们可以选择各种显示器模块,包括数字显示器。

我们需要选择一个100进制数字显示器,并将计数器的输出连接到其输入端口上。

第四步,我们需要为计数器提供复位功能,以便在需要时将计数器的值重置为0。

在Multisim中,我们可以使用一个按钮模块来实现复位功能。

我们需要将按钮的输出连接到计数器的复位端口上。

第五步,我们需要为电路添加电源。

在Multisim中,我们可以通过选择电池模块或一个直流电源来为电路提供电源。

我们需要将电源的正负极分别连接到电路的正负极端口上。

最后,我们需要检查一遍我们的电路图,并确认每个元器件的连接方式和参数设置都是正确的。

如果一切都准备好了,我们就可以开始仿真电路的工作过程,看看我们的计数器是否能够正常工作。

74192是一种常见的集成电路,通常用于实现二进制或十进制的计数器。

虽然74192本身是二进制的计数器,但我们可以通过逻辑设计来将其转换为100进制计数器。

以下是实现100进制计数器的基本原理:

1. 使用四个74192:由于74192是四位计数器,我们需要使用四个74192芯片来构建100进制计数器。

每个74192芯片负责计数器的一个数位。

2. 设置计数范围:根据100进制,我们需要设置计数范围为0-99。

这意味着每个数位需要以100为基数进行计数。

因此,我们需要将每个74192的计数范围设置为0-99。

3. 连接输出:将四个74192芯片的计数输出相连,以形成完整的100进制计数器。

低位计数器的进位输出(Carry Out)将连接到高位计数器的时钟输入(Clock In),以实现进位。

4. 重置和启动:在开始计数之前,需要将所有74192芯片的复位输入(Reset)设置为逻辑高电平,以将计数器复位为0。

然后,通过将任意一个74192的时钟输入(Clock In)设置为逻辑高电平来启动计数器。

5. 结果显示:将每个74192芯片的计数输出连接到适当的显示设备,如数码管或LED灯,以显示计数器的当前值。

通过这种方式,我们可以利用多个74192芯片实现一个100进制计数器。

该实验需要适当的电路设计和连接,以及对集成电路的正确使用和配置。

基于MSI芯片74160设计模为100的计数器1、实验目的:基于MSI芯片74160,利用QuartusII软件设计并实现一个计数器的逻辑功能,通过电路的仿真和硬件验证,进一步了解计数器的特性和功能。

2、实验原理:利用集成计数器MSI芯片的清零端和置数端实现归零,可以按自然态序进行计数的N进制计数器的方法。

集成计数器中,清零、置数均采用异步方式的有74LS163;均采用异步方式的有74LS193、74LS197、74LS192;清零端采用异步方式、置数端采用同步方式的有74LS161、74LS160。

74161/74160功能真值表表1图13、实验环境:PC机(Windowsxp,QuartusII)4、实验内容:按照第五章相关内容,完成计数器的实际,包括原理图输入、编译、综合、适配、仿真,并将此计数器电路设计成一个硬件符号入库。

最后利用两个MSI芯片74160完成一个模为60的计数器的设计,包括原理图的输入、编译、综合、适配、仿真。

5、实验步骤:Step1.启动QuartusII“开始”菜单“所有程序”中的“Altera”程序框中选择“QuartusII”如图1所示:Step2.建立工作库目录文件夹以便设计工程项目的存储EDA工具中的任何一项设计都是一项工程(PROJECT),应首先为此工程建立一个放置与此工程相关的文件的文件夹,此文件夹将被EDA软件默认为工作库(WORK LIBRARY).一般不同的设计项目最好放在相应的文件夹中,注意,一个设计项目可以包含多个设计文件夹。

本项目中的文件夹取名为counter_100,路径为:E:/数字逻辑/作业/100511217/。

注意:文件夹名不能用中文,且不可带空格。

Step3.输入设计(1)打开QuartusII,选择File|New命令。

在New窗口中(如图2所示)的DeviceDesign File中选择硬件设计文件类型为Block Diagram/Schematic File,然后在框图设计文件编辑窗中输入源程序图1的文件。

武汉工业学院数字逻辑实验报告姓名张聪院(系) 数学与计算机学院专业电气信息类学号100511217指导教师刘昌华武汉工业学院数学与计算机学院2011-11-30基于MSI芯片74160设计模为100的计数器1、实验目的:基于MSI芯片74160,利用QuartusII软件设计并实现一个计数器的逻辑功能,通过电路的仿真和硬件验证,进一步了解计数器的特性和功能。

2、实验原理:利用集成计数器MSI芯片的清零端和置数端实现归零,可以按自然态序进行计数的N 进制计数器的方法。

集成计数器中,清零、置数均采用异步方式的有74LS163;均采用异步方式的有74LS193、74LS197、74LS192;清零端采用异步方式、置数端采用同步方式的有74LS161、74LS160。

表1图13、实验环境:PC机(Windows xp,QuartusII)4、实验内容:按照第五章相关内容,完成计数器的实际,包括原理图输入、编译、综合、适配、仿真,并将此计数器电路设计成一个硬件符号入库。

最后利用两个MSI芯片74160完成一个模为60的计数器的设计,包括原理图的输入、编译、综合、适配、仿真。

5、实验步骤:Step1.启动QuartusII“开始”菜单“所有程序”中的“Altera”程序框中选择“QuartusII”如图1所示:Step2.建立工作库目录文件夹以便设计工程项目的存储EDA工具中的任何一项设计都是一项工程(PROJECT),应首先为此工程建立一个放置与此工程相关的文件的文件夹,此文件夹将被EDA软件默认为工作库(WORK LIBRARY).一般不同的设计项目最好放在相应的文件夹中,注意,一个设计项目可以包含多个设计文件夹。

本项目中的文件夹取名为counter_100,路径为:E:/数字逻辑/作业/100511217/。

注意:文件夹名不能用中文,且不可带空格。

Step3.输入设计(1)打开QuartusII,选择File|New命令。

在New窗口中(如图2所示)的Device Design File 中选择硬件设计文件类型为Block Diagram/Schematic File,然后在框图设计文件编辑窗中输入源程序图1的文件。

图2(2)放置元件在原理图空白处双击鼠标,跳出Symbol选择窗口(或单击右键选择Inster→Symbol…),出现元件对话框图2图3为了设计一位全加器,可参考图1,分别调入元件input、output、与门AND4、MSI芯片74160,并连接好。

然后分别在input和output的PIN NAME上双击使其变黑,再用键盘分别输入各引脚名:CLRN,CLK(时钟),CO(输出),Q[7..0](两个74160共8个输出)。

以及Q[0]到Q[7]输出。

(3)文件存盘从菜单File中选择Save as 命令,选择刚才为自己工程建立的目录E:/数字逻辑/作业/100511217/,将设计好的图文件取名为:counter_100(注意后缀是.bdf),并存盘在E:/数字逻辑/作业/100511217/ 目录内,如图4所示。

图4Step4.新建工程(1)单击File/New Project Wizard,弹出“工程设置”对话框,如图5图5第1行的E:/数字逻辑/作业/100511217/ 表示工程所在的工作库文件夹,第2行表示该工程的工程名,此工程名可以取任何其他的名,也可以用顶层文件实体名作为工程名;第3行是当前工程顶层文件的实体名(此处输入的顶层文件实体名与之后的设计文件实体名相同,默认的顶层文件名与工程名相同),此处即为counter_100。

(2)加入设计文件单击Next按钮,在弹出的对话框中单击File栏中的“…”,将于工程相关的所有文件加入工程中,单击Add按钮进入此工程,即可得如图6所示的情况。

图6 添加设计文件(3)选择目标芯片(用户必须选择与开发板相应的FPGA器件型号):这时弹出选择目标芯片的窗口,首先在Family栏选择目标芯片系列,在此选择Cylone 系列,如图7所示。

再次单击Next按钮,选择此系列的具体芯片EP1C6Q240C8,这里EP1C6表示Cylone系列及此器件的规模,Q表示PQFP封装,C8表示速度级别。

图7 选择目标芯片(4)选择仿EDA工具:设计中可能用到的EDA工具有时序分析工具、仿真工具和综合工具。

单击图7中Next按钮,可从弹出的窗口中选择EDA工具类型,如果都选None,表示选QuartusII中自带的EDA工具。

(5)单击Next按钮后进入下一步。

弹出“工程设置统计”窗口,如图8所示。

图8 工程设计统计(6)结束设置。

最后单击Finish按钮,即表示已设定好此工程,并出现counter_100的工程管理窗口(亦称Compilation Hierarchies窗口),该窗口主要显示该项目的层次结构和各层次的实体名,如图9所示。

完成设置后可以看到窗口左上角显示所设工程路径的变化。

QuartusII将工程信息文件存储在工程配置文件(.qsf)中。

它包括设计文件、波形文件、SignalTapII文件、内存初始化文件,以及构成工程的编译器、仿真器的软件构件设置等有关QuartusII工程的所有信息。

图9Step5.编译综合QuartusII默认把所有编译结果放在工程根目录中,为了让QuartusII像Visual Studio等IDE 一样把编译结果放在一个单独的目录中,需要指定编译结果的输出路径。

单击菜单项Assignment→settings,选中Compilation processSetting 选项卡,勾选右边的Save Project output files inspecified directory,输入路径(release or debug),如下图:QuarterII编译器是由一系列处理模块构成,这些模块负责对设计项目检错,逻辑综合、结构综合、输出结果的编辑配置,以及时序分析。

单击菜单选项Processing→Start→Start Analysis&Synthesis执行分析与综合项目检错(或Ctrl+K),如果仅仅需要检测语法,那么执行Analysis&Elaboration(分析与解析),但这一步生成的数据并不对应FPGA器件的物理结构,生成的网表中节点的名称也不与FPGA器件的Cell名称对应。

更多情况下直接执行Start Analysis&Synthesis。

执行分析与综合后,生成的数据库对应FPGA器件的物理结构,映射后的数据库包含FPGA底层Cell的位置信息和Cell的时序信息。

上面所有工作做好后,执行QuartusII主窗口的Processing菜单的Star Compilation 选项,启动全程编译。

编译好后的工程管理窗口如图10所示。

图10编译过程中应注意工程管理窗下方的Processing栏中的编译信息。

如果编译有错,启动编译后下方Processing栏会显示出来,可双击错误提示,即弹出对应用深色标记的相关错误位置,再次编译直至排除所有错误。

在图10中单击Report可得到如图11所示的界面,此界面左上角是工程管理窗口,单击其中各项可了解编译和分析结果。

如单击Flow Summary,将在右栏显示此工程的硬件耗用报告:Timing Analyzer 项,则能看到当前工程所有相关时序特性的报告。

图11Step6.仿真测试该工程编译通过后,必须对其功能和时序性能进行仿真检测,以验证设计结果是否满足设计要求。

整个时序仿真测试流程一般有建立波形文件、输入信号节点、设置波形参数、编辑输入信号、波形文件存盘、运行仿真器和分析仿真波形等步骤。

现给出以.vwf文件方式的仿真测试流程的具体步骤如下:(1)建立仿真波形文件选择QuartusII主窗口主窗口的File菜单的New选项,在弹出的文件类型编辑对话框中,选择Verification/Debugging Files 中的Vector Weaveform Files 项,单击OK按钮,打开波形文件编辑窗口。

单击File→Save As,即出现如图12所示:图12(2)设置仿真参数选择Assigment 中的settings 对话框,可以进行如仿真激励文件、毛刺检测、功耗估计、输出等设置,一般情况下选默认值。

如图13所示:图13本题中整个仿真时间区域蛇为10µs、时间轴周期为100ns,其设置步骤是在Edit菜单中选择End Time,在弹出窗口中Time 出填入10,单位选择µs,同理在Gride Size中Time Period 输入50ns,单击OK按钮,设置结束。

(3)输入工程的信号节点单击Edit→Insert→Insert Node or BUS…,即可弹出如图14的对话框,单击Nodes Found选项,在Nodes Found对话框Filter项中选择Pins:All,然后单击List按钮,在下方的窗口中出现设计中的工程的所有窗口的引脚名,选择欲观察信号节点,用中间的“≥”将需要观察的信号选到右边,如图15所示,单击OK按钮,回到Insert Node or BUS 对话框,再单击OK按钮即可,如图16所示。

图14.图15图16(4)设计输入信号波形单击图16窗口的输入信号CP使之变成蓝色条,再单击右键,选择Value设置中的Clock对话框(如图17所示),设置其周期为50ns,同理分别设置其他信号的波形,波形编辑结果如图19所示。

双击图16所示输出信号CO、Q[7..0],将弹出信号输出格式设置对话框图18所示,在对话框的Radix中有6中选择,将在后续试验中要用到。

图17 图18图19(5)启动仿真器,观察结果所有设置完成后,选择“File”中的“Save As”项,将波形文件以默认名存盘后,即可启动仿真器Processing|Start Simulation,直到出现Simulation was successful,仿真结束。

QuartusII9.0中默认的Simulation mode 为Timing(时序仿真)仿真波形输出文件Simulation Report 将自动弹出如图20所示,通过该图可查看实际设计的电路运行时是否满足延时要求。

注意,QuartusII的仿真波形文件中,波形编辑文件(*.bdf)与波形仿真报告输出文件(Simulation Report)是分开的,而MaxplusII的激励波形编辑文件与波形仿真报告输出文件是合二为一的。

图20(6)包装元件入库分析仿真结果正确无误后,选择File→Create/update→Create Symbol File for CurrentFile,将当前文件变成了一个包装好的单一元件(counter_100.bsf),并放置在工程路径指定的目录中以备后用。