等精度测频法的频率计设计——开题报告

- 格式:doc

- 大小:45.00 KB

- 文档页数:4

频率计设计开题报告频率计设计开题报告一、研究背景频率计是一种用于测量信号频率的仪器,广泛应用于电子、通信、无线电等领域。

目前市场上存在各种类型的频率计,但在某些特定应用场景下,仍存在一些问题,如精度不高、测量范围有限等。

因此,本次研究旨在设计一种新型的频率计,以提高测量精度和拓展测量范围。

二、研究目标本次研究的主要目标是设计一种基于数字信号处理技术的高精度频率计。

具体目标包括:1. 提高频率计的测量精度,使其能够满足更高精度要求的应用场景;2. 拓展频率计的测量范围,使其能够适应更广泛的频率范围;3. 优化频率计的性能指标,如响应速度、稳定性等。

三、研究内容本次研究的主要内容包括以下几个方面:1. 频率计原理研究:对现有频率计的工作原理进行深入研究,分析其优缺点,为设计新型频率计提供理论基础;2. 数字信号处理算法研究:探索适用于频率计的数字信号处理算法,提高测量精度和响应速度;3. 电路设计与优化:设计新型频率计的硬件电路,优化电路结构和参数,提高稳定性和抗干扰能力;4. 系统集成与测试:将数字信号处理算法和电路设计相结合,进行系统集成,并进行实验测试,验证设计的可行性和性能指标。

四、研究方法本次研究将采用以下研究方法:1. 文献综述:对相关领域的文献进行综述,了解现有频率计的研究进展和存在的问题;2. 理论分析:对频率计的原理进行深入分析,探索提高测量精度和拓展测量范围的方法;3. 数字信号处理算法的仿真与验证:使用MATLAB等工具进行数字信号处理算法的仿真和验证,评估其性能;4. 电路设计与优化:使用EDA工具进行电路设计和优化,提高电路的性能指标;5. 系统集成与测试:将数字信号处理算法和电路设计相结合,进行系统集成,并进行实验测试,验证设计的可行性和性能指标。

五、研究意义本次研究的意义主要体现在以下几个方面:1. 提高测量精度:设计一种高精度的频率计,满足更高精度要求的应用场景,提高测量精度;2. 拓展测量范围:设计一种能够适应更广泛频率范围的频率计,满足不同应用场景的需求;3. 推动技术发展:通过研究新型频率计的设计,推动相关领域的技术发展,为电子、通信、无线电等领域的应用提供更好的测量工具。

摘要摘要频率测量是电子学测量中最为基本的测量之一。

频率计主要是由信号输入和放大电路、单片机模块、分频模块及显示电路模块组成。

AT89C52单片机是频率计的控制核心,来完成它待测信号的计数,译码,显示以及对分频比的控制。

利用它内部的定时/计数器完成待测信号频率的测量。

在整个设计过程中,所制作的频率计采用外部分频,实现1Hz-1kHz的频率测量及1ms-100ms的脉宽测量,而且可以实现量程自动切换流程。

以AT89C52单片机为核心,通过单片机内部定时/计数器的门控时间,方便对频率计的测量。

其待测频率值使用LCD液晶显示器显示,并可以自动切换量程。

本次采用单片机技术设计一种数字显示的频率计,具有测量准确度高,响应速度快,体积小等优点。

关键词:频率计,单片机,LCD液晶显示器。

I西安交通大学城市学院本科生毕业设计(论文)I IABSTRACTABSTRACTFrequency measurement is one of the most basic measurement electronics measurement. Frequency counter is dominated by the signal input and the amplifier circuit, microcontroller module, frequency module and the display circuit module. AT89C52 microcontroller is to control the core frequency meter to complete its measured signal counting, decoding, display and control divider ratio. Use its internal timer / counter to complete the test signal frequency measurements.Throughout the design process, by making use of external parts of the frequency meter frequency to achieve frequency measurement and pulse width measurement 1ms-100ms of 1Hz-1kHz, and can realize automatic range switching processes. To AT89C52 microcontroller as the core, through the internal microcontroller timer / counter gate time, easy measurement of the frequency meter. Its measured frequency value using the LCD display, and can automatically switch range. The use of microcomputer technology to design a digital display of frequency meter, have a measurement of high accuracy, fast response, small size and so on.KEYWORDS: Frequency meter, Single chip, LCD display.III西安交通大学城市学院本科生毕业设计(论文)I V目录目录1 绪论 (1)1.1 数字频率计简介 (1)1.2 单片机系统的研究现状 (2)1.3 频率计的研究现状 (2)1.4设计的技术要求和主要内容 (3)2 等精度频率计的原理与应用 (5)2.1 等精度频率计测量的原理 (5)2.2 脉冲宽度的测量方法 (6)2.3 等精度频率计的误差分析 (6)2.4 本章小结 (8)3 硬件电路设计 (9)3.1单片机周边电路 (9)3.2 51单片机及AT89C52介绍 (9)3.2.1 单片机简介 (9)3.2.2 AT89C52简介 (10)3.2.3 管脚说明 (11)3.2.4 AT89C52主要性能 (13)3.3 各部分电路图及电路工作原理分析 (13)3.3.1 时钟脉冲电路 (13)3.3.2 同步门逻辑控制电路 (14)3.3.3 LCD显示电路 (15)3.3.4 复位电路 (17)4 软件设计 (19)4.1 KEIL51软件简介 (19)4.2 软件的模块化设计及各部说明 (19)4.2.1 定时中断模块 (19)4.2.2 测量模块 (20)4.2.3 显示模块 (20)V西安交通大学城市学院本科生毕业设计(论文)V I 4.2.4 软件流程图 (20)5 系统仿真与调试 (21)5.1 Proteus软件简介 (21)5.2 Proteus的电路仿真 (22)5.3误差分析 (24)总结 (27)致谢 (29)参考文献 (31)附录 (33)1 程序 (33)2 附图 (41)3 外文翻译 (44)绪论1 绪论1.1 数字频率计简介数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。

采用等精度测频原理的频率计的设计一.设计要求1.设计一个用等精度测频原理的频率计。

2.频率测量测量范围1~9999;3.用4位带小数点数码管显示其频率;二.测频原理及误差分析1.常用的直接测频方法主要有测频法和测周期法两种。

2.测频法就是在确定的闸门时间Tw内,记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:fx=Nx/Tw。

3.测周期法需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fx=fs/Ns。

4.这两种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Nx或Ns有关。

为了保证测试精度,一般对于低频信号采用测周期法;对于高频信号采用测频法,因此测试时很不方便,所以人门提出等精度测频方法。

5.等精度测频方法是在直接测频方法的基础上发展起来的。

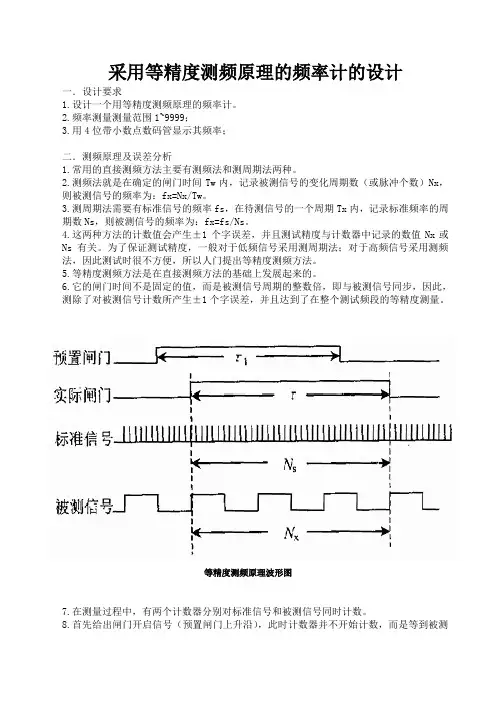

6.它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,测除了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。

等精度测频原理波形图7.在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。

8.首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。

然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。

可以看出,实际闸门时间τ与预置闸门时间τ1并不严格相等,但差值不超过被测信号的一个周期9.设在一次实际闸门时间τ中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。

10.标准信号的频率为fs,则被测信号的频率为11.由式(1)可知,若忽略标频fs的误差,则等精度测频可能产生的相对误差为12.δ=(|fxc-fx|/fxe)×100% (2)13.其中fxe为被测信号频率的准确值。

数字频率计摘要以FPGA(EP2C8Q208C8N)为控制核心设计数字频率计,设计采用硬件描述语言Verilog 该作品主要包括FPGA控制、数码管模块、信号发生器、直流电源模块、独立按键、指示灯模块。

主要由直流电源供电、数字信号发生器输出信号,FPGA 控制信号的采集、处理、输出,数码管显示数据,按键切换档位,指示灯显示档位。

作品实现了测频、测周、测占空比,能准确的测量频率在10Hz 到100kHz之间的信号。

关键字: 频率计等精度 FPGA (EP2C8Q208C8N)信号发生器Verilog语言一、系统方案论证与比较根据题目要求,系统分为以下几个模块,各模块的实现方案比较选择与确定如下:1.主控器件比较与选择方案一:采用FPGA(EP2C8Q208C8N)作为核心控制,FPGA具有丰富的I/O 口、内部逻辑和连线资源,采集信号速度快,运行速度快,能够显示大量的信息,分频方便。

方案二:采用SST89C51作为主控器件,虽然该款单片机较便宜,但运行速度较慢,不适合对速度有太大要求的场合,并且不带AD,增加了外围电路。

综上所述,主控器件我选择方案一。

2.测量方法的比较与选择方案一:采用测频法测量。

在闸门时间内对时钟信号和被测信号同时计数,由于在闸门闭合的时候闸门时间不能是被测信号的整数倍,导致计数相差为一个被测信号时间,所以测频法只适合频率较高的测量。

方案二:采用测周法测量。

用被测信号做闸门,在闸门信号内对时钟信号计数,由于在闸门闭合的时候闸门时间不能是时钟信号的整数倍,导致计数相差为一个时钟信号时间,所以测周法只适合较低频率的测量。

方案三:采用等精度法和测周法结合的方法。

用等精度发测量1KHZ以上的频率,测周法测量1KHZ一下的频率。

这种方法取长补短,既能准确的测高频又能测低频。

综上所述,测量方法我选用方案三。

3. 界面显示方案的选择方案一:采用数码管显示,控制程序简单,价格便宜,显示直观。

方案二:液晶5110,虽然体积小,可以显示各种文字,字符和图案。

开题报告通信工程数字频率计设计一、课题研究意义及现状频率计又称频率计数器,是一种专门对被测信号频率进行测量的电子测量仪器,频率测量的原理归结成一句话就是:单位时间内对被测信号进行计数。

在传统的电子测量仪器中,频率计的应用范围越来越广,它不仅可以测量普通的如正弦波信号的频率,在教学、科研、高精度仪器测量、工业控制等领域也都有广泛的应用。

示波器虽然可以对信号进行频率测量,但缺点是精度较低,误差较大。

频谱仪虽然有也准确的测量频率和显示被测信号的频谱的优点,但它的测量速度比较慢,比较耗时间,也不能实时精确的捕捉到被测信号频率的变化情况。

但频率计却能够快速精确的捕捉到被测信号频率的变化,所以,频率计在各个重要的领域中被普遍使用到。

例如:在传统的生产制造企业中,频率计被广泛的应用在生产线的生产测试中。

当生产线中有故障的晶振产品时,频率计就可以快速准确的定位到发生故障的那件晶振产品,生产人员就可以及时的采取措施,以确保产品的质量保证。

在计量实验室中,频率计也可以对各种电子测量设备等产品的本地振荡器进行校准。

在无线通讯测试中,就可以用频率计对无线通讯基站的主时钟进行校准,还可以对无线电台的跳频信号和频率调制信号进行分析。

虽然目前使用的频率计产品很多,但基本上都是采用专用技术芯片(如ICM7240等)和数字逻辑电路组成,由于这些芯片本身的工作频率不高(如ICM7240仅有15MHZ左右),从而限制了产品工作频率的提高,远不能达到在一些特殊场合需要测量很高频率的要求,而且测量精度也收到芯片本身的极大限制。

随着社会的进步、科技的发展,频率计所测量的频率范围极影越来越大,精度也越来越高,但最重要的是如今的频率计已不仅仅是简单的用来测量频率和一些具有周期特性的频率:经过改装,做成数字式脉宽测量仪,就可以测量脉冲宽度;也可以经过改装后做成可以测量电容的数字式电容测量仪;还可以在电路中增加传感器,使之可以测量长度、重量、压力、温度等非电量的测量。

等精度数字频率计的设计李艳秋摘要基于传统测频原理的频率计的测量精度将随着被测信号频率的下降而降低,在实用中有很大的局限性,而等精度频率计不但有较高的测量精度,而且在整个测频区域内保持恒定的测试精度。

运用等精度测量原理,结合单片机技术设计了一种数字频率计,由于采用了屏蔽驱动电路及数字均值滤波等技术措施,因而能在较宽定的频率范围和幅度范围内对频率,周期,脉宽,占空比等参数进行测量,并可通过调整闸门时间预置测量精度。

选取的这种综合测量法作为数字频率计的测量算法,提出了基于FPGA 的数字频率计的设计方案。

给出了该设计方案的实际测量效果,证明该设计方案切实可行,能达到较高的频率测量精度。

关键词等精度测量,单片机,频率计,闸门时间,FPGAⅡABSTRACTAlong with is measured based on the traditional frequency measurement principle frequency meter measuring accuracy the signalling frequency the drop but to reduce, in is practical has the very big limitation, but and so on the precision frequency meter not only has teaches the high measuring accuracy, moreover maintains the constant test precision in the entire frequency measurement region. Using and so on the precision survey principle, unified the monolithic integrated circuit technical design one kind of numeral frequency meter, because has used the shield actuation electric circuit and technical measure and so on digital average value filter, thus could in compared in the frequency range and the scope scope which the width decided to the frequency, the cycle, the pulse width, occupied parameter and so on spatial ratio carries on the survey, and might through the adjustment strobe time initialization measuring accuracy. Selection this kind of synthesis measured the mensuration took the digital frequency meter the survey algorithm, proposed based on the FPGA digital frequency meter design proposal. Has produced this design proposal actual survey effect, proved this design proposal is practical and feasible, can achieve the high frequency measurement precisionKeywords Precision survey, microcontroller, frequency meter, strobe time,field programmable gate arrayⅡ目录目录摘要 (I)ABSTRACT··························································································I II1 绪论 (1)2 系统设计方案 (2)2.1系统设计方案的选择 (2)2.1.1 频率测量模块 (2)2.1.2 周期测量模块 (4)2.1.3 脉宽测量模块 (4)2.1.4 占空比测量模块 (4)3 系统总体设计方案 (5)4 CPLD/FPGA测频专用模块的VHDL程序设计 (6)4.1 测频模块逻辑结构 (6)4.2 各模块功能和工作步骤如下: (6)4.2.1 测频/测周期的实现 (7)4.2.2 控制部件设计 (7)4.2.3 脉冲宽度测量和占空比测量模块设计 (7)4.2.4 电路显示模块 (8)4.2.5 数码管的编码表 (10)5 单片机控制与运算程序的设计 (11)5.1 AT89C51RC单片机简介 (11)5.2 软件调试系统 (19)5.3具体试验过程 (20)5.3.1 第一次测试 (20)5.3.2 第二次计算 (22)5.4 系统调试的方法 (23)5.4.1 调试的软/硬件 (23)5.4.2 系统的仿真结果 (23)5.5 设计技巧分析 (25)5.6 系统扩展思路 (25)6 VHDL程序语言和FPGA简介 (26)6.1 vhdl程序语言介绍: (26)6.2 FPGA 简介 (28)6.3 VHDL 在FPGA中的运用 (29)攀枝花学院本科毕业设计(论文)目录结论 (32)附录A:单片机程序和VHDL程序 (33)参考文献 (56)致谢 (57)IV1 绪论1 绪论测量频率是电子测量技术中最常见的测量之一。

高精度频率稳定测量仪的设计和实现的开题报告一、研究背景频率稳定性是衡量信号质量的重要指标之一,尤其是对于高精度测量和精密控制应用来说,频率稳定性要求更高。

目前市面上存在着一些高精度频率稳定测量仪,但是它们的制造成本较高,不便于大规模推广应用。

因此,如何设计实现一种低成本、高精度的频率稳定测量仪,成为当前研究的热点之一。

二、研究目的及意义设计实现一种低成本、高精度的频率稳定测量仪,有助于提高信号质量、精确测量和控制,可广泛应用于自动控制系统、无线通信领域、精密仪器等。

三、研究内容及方法1. 系统设计方案的研究根据频率稳定测量仪的基本原理和需求,设计出合理、可行且成本较低的系统设计方案。

2. 系统硬件设计按照设计方案,进行系统硬件电路的设计,包括信号源、频率计、信号处理模块等。

3. 系统软件设计编写适用于频率稳定测量仪的软件程序,对数据进行采集、处理和显示等操作。

4. 调试、优化和测试对所设计的频率稳定测量仪进行全面的调试,找出存在的问题,进行优化改进,最终进行测试验证,确保其满足研究目标和性能指标。

研究方法主要是基于现有技术和理论的探索和改进,采用了不同工具和软件开发环境来实现系统设计和软件编写等。

四、预期成果1. 完成一套低成本、高精度的频率稳定测量仪的设计与实现。

2. 实现对信号稳定性的高精度测量,提高信号质量。

3. 提供了一种低成本的频率稳定测量仪方案,并对其进行了系统性能测试。

五、论文结构安排本文预计分为以下几个部分:绪论、相关技术介绍、系统设计方案、系统实现与测试、结论与展望等部分。

具体内容如下:1. 绪论介绍研究背景、意义、研究目标和方法等。

2. 相关技术介绍对部分与该研究相关的技术进行介绍。

3. 系统设计方案提出一套低成本、高精度的频率稳定测量仪的设计方案,并进行详细的阐述。

4. 系统实现与测试对所设计方案进行实现和测试,并详细阐述整个过程。

5. 结论与展望对研究结果进行总结,对未来该领域的研究提出展望。

新型高精度频率测量仪的实现的开题报告一、选题背景和意义随着科技的发展,频率测量对于现代化生产和科研具有重要的意义,它涉及到许多行业及领域,比如通讯、电子、电力、医疗等。

为确保频率测量精度,传统的频率测量仪已不能满足需求,高精度的频率测量仪已成为目前的趋势与热点。

本文旨在研发一种新型高精度频率测量仪,以提高频率测量的精度和稳定性。

二、研究目标及内容本文将研究一种新型的高精度频率测量仪,主要涉及以下几个方面:1. 高精度的时钟源设计:时钟源性能是影响频率测量精度的重要因素之一,本文将研究一种高精度的时钟源设计方案。

2. 数字信号的处理与算法设计:设计一种对输入信号进行数字化处理,并通过合适的算法进行频率测量的方法。

3. 稳定度测试与实验验证:实验验证所设计的频率测量仪的稳定度和精度,并通过实验分析探讨其优缺点及应用前景。

三、研究难点及解决方法1. 时钟源的设计难点:时钟源是高精度频率测量仪的核心,设计高精度的时钟源需要克服传输延迟、供电干扰、温度浮动等问题。

为此,可以采用一定的抑制方法,比如锁相环技术、时钟提高技术等。

2. 频率测量算法的设计难点:如何提高测量精度是该算法需要解决的主要难点。

本文将采用FFT算法或插值算法对输入信号进行计算,以提高测量精度。

3. 实验验证难点:实验验证过程中,需要保证试验环境的稳定性,以避免干扰造成的误差。

为此,可采用实验室环境的干扰抑制方法,如隔离、屏蔽等。

四、预期结果与应用前景预期本文将能够研制出一款高精度频率测量仪,其测量精度可达到1ppm,稳定性高,具有良好的抗干扰性和广泛的应用前景。

可以在无线通讯、医疗、计量和科研等领域得到广泛的应用。

频率标准及频率信号测量的开题报告一、选题背景随着现代科技的快速发展,精度要求越来越高的时间测量和时间同步成为了许多领域的重要需求,如通信、导航、测控等。

而这些领域又具有高可靠性、高稳定性、高精度的要求。

频率标准及频率信号测量是这些领域中的重要技术基石,因此对其进行深入研究,可以大大提高这些领域的技术水平,为人类社会的发展做出贡献。

二、研究意义频率标准及频率信号测量涉及到多领域、多学科的知识,甚至包括纯粹物理学和现代量子力学的知识,因此在与其相关的学术和技术领域中具有十分广泛的应用。

首先,在通信、导航、测控等领域,需要对时间信号进行精确控制和传递,而频率标准是实现时间同步的关键,频率信号测量是实现时间测量的重要手段。

如全球卫星导航系统(GPS)、数码处理系统(DSP)等都需要使用高稳定性的频率标准和准确可靠的频率信号测量方法。

其次,在天文学、大地测量等领域中,需要对地球自转、恒星运动等进行测量,而频率标准和频率信号测量技术则是实现这些测量的基础。

此外,在光学、光子学、原子物理等领域中,精确的时钟及其应用也越来越受到关注和研究。

三、研究内容及方法频率标准及频率信号测量的核心内容包括:1. 频率标准的理论原理及类型。

常用的频率标准包括石英晶体振荡器、氢钟、铷钟、光学钟等。

2. 频率信号测量方法及其分辨率。

包括直接测量法、锁相放大法、数字信号处理法等。

研究方法上,我们将主要使用文献综述和理论分析的方法,对国内外相关研究进行梳理和总结,探讨频率标准及频率信号测量技术的基本原理和最新发展动态。

另外,我们还将通过实验、模拟等手段验证分析结果,并分析其实用性和可行性。

四、预期成果及创新点通过对频率标准及频率信号测量技术的研究,我们预期可以达到以下成果:1. 深入了解频率标准及频率信号测量技术的理论基础和最新研究进展,为更深入的研究提供基础。

2. 排序总结目前国内外各种频率标准及频率信号测量方法的优缺点,为工程应用提供指导。

电气与信息学院毕业设计(论文)开题报告题目名称:报告人:专业班级:指导教师:《基于VHDL的等精度频率计设计与实现》开题报告一、课题的目的和意义1.研究目的基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测试精度。

2.研究意义随着电子技术的高速发展,CPLD的出现以其高速、高可靠性、串并行工作方式等突出优点在电子设计中广泛应用,并代表着未来EDA设计的方向。

CPLD的设计采用了高级语言(如VHDL语言),进一步打破了软硬件之间的界限,加速了产品的开发过程。

采用先进的CPLD(复杂可编程逻辑器件)取代传统的标准集成电路、接口电路也是电子技术发展的必然趋势。

CPLD由于采用连续连接结构,易于预测延时,从而使电路仿真更加准确,可用于各种数字化是电子设计的必由之路也是必然的发展趋势。

随着科技的不断发展,单片机的也暴露出了两大突出缺点:串行工作特点决定了它的低速性和程序跑飞、不可靠复位决定了它的低可靠性。

EDA(电子设计自动化) 代表了当今电子设计技术的最新发展方向,它的基本特征是:设计人员按照“自顶向下”的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC) 实现,然后采用硬件描述语言(HDL) 完成系统行为级设计,最后通过综合器和适配器生成最终目标器件。

当今小型电子功用设备设计中,结合FPGA 和单片机技术是开发常用仪器仪表的主流。

应用这种技术可使设计过程大大简化,也有利于减小产品体积功耗。

在电子工程,资源勘探,仪器仪表的等相关应用上,频率计是工程技术人员必不可少的测量工具。

数字逻辑系统的设计。

灵活运用CPLD高速、高可靠性以及可编程性强等特点,可有效地突破传统的电子系统中由来已久的设计瓶颈,使这些系统的性能大幅度的提高。

此外,利用CPLD进行数字系统设计可大大缩短设计周期,大幅度的减少设计费用,降低设计风险。

等精度频率计设计报告创新2班(电气0515班)李柱炎一、频率计的原理测量频率的方法有三种:一是测频法,原理是在给定的时间内(比如1s)的时间内,统计被测信号脉冲的个数,即可得出频率。

此方法适用于测量高频信号。

二是测周法,原理是测量信号一个周期的时间,周期的倒数即为信号的频率。

此方法适用于测量低频信号。

三是多周期同步法,等精度频率计即基于此原理。

此方法适用于各种频率。

二、等精度频率计的原理图1多周期同步法中,实际的信号闸门时间不是固定的值,而是被测信号的整周期倍,即与被测信号同步,因此消除了对被测信号计数时产生的±1个字误差,测量精度大大提高,而且达到了在整个测量频段的等精度测量,其原理框图和波形图如图1所示。

设na、nb分别为计数器a和b记得的数值,τ'为闸门时间,则na=τ'·fx(1)nb=τ'·f0(2)f X/f0=na/nb计数器a的计数脉冲与闸门的开闭是完全同步的,因而不存在±1个字的计数误差,由式(3)微分可得:dnb=±1,τ'=nb/f0(5)得到测量分辨率:dfx/fx=±1/(τ'×f0)(6)由式(6)可以看出,测量分辨率与被测频率的大小无关,仅与取样时间及时基频率有关,可以实现被测频带内的等精度测量。

取样时间越长,时基频率越高,分辨率越高。

多周期同步法与传统的计数法测频比较,测量精度明显提高。

三、等精度频率计的架构等精度频率计架构如图2所示。

频率计由一个D触发器,两个24位的计数器,控制部件,运算部件,输出转换与显示部件构成。

计数器Stcount(Counter)(上面的那个)对标准信号进行计数,计数器UKcount(Counter)(下面的那个)对被测信号进行计数。

运算部件由MoveBD、Div32、DivideIF 三个模块构成。

BinToBCD模块为输出转换与显示部件。

实验三等精度频率计实验报告一.实验任务及要求(1)实验任务设计一个简易等精度频率计。

(2)实验要求:a.测量范围信号:方波幅度TTL电平;频率:1Hz~1MHzb.测试误差≤0.1%(全量程)c.闸门时间:~1s,响应时间:~2s乘除运算: FPGA显示:十进制分量程(MHZ,KHZ,HZ)二实验设计方案(1)用QuartusII的原理图输入来完成系统的顶层设计。

(2)用VHDL编写各功能模块。

(3)分量程显示输出频率。

(4)通过除法运算实现十六进制到十进制的转换输出。

其具体实现方案如下原理图三、系统硬件设计1、测试参数计算考虑Nb最大误差为:1,则由实验要求测试误差≤0.1%(全量程)则可知N B≥1000因为阈值闸门时间为1s,所以时钟发生器频率fc≥1000.由实验要求测量频率范围为:1Hz~1MHz在实验中取时钟发生器频率为1MHz2.阈值闸门脉冲发生器频率由时钟发生器频率分频得到,具体实现由VHDL创建功能模块。

原理:由时钟发生器频率控制cout(中间变量)累加,从而控制阈值闸门脉冲发生器的闸门时间和响应时间。

3.输出频率显示设置,采用乘、除法模块(LPM)设计以及用VHDL语言编写。

其中通过编写VHDL,设置其输出单位,创建功能模块lc和chang。

其中z1和z2分别控制LED1和LED2.当LED1灯亮时则输出单位为KHZ,当LED2灯亮时则输出单位为MHZ,否则为HZ。

并且通过乘除法的转换输出使数码管最后三位显示的为小数位。

通过除法模块将原十六进制输出转化为十进制输出在数码管上。

4.具体电路原理图见附录1四.系统软件设计1.分频器2.输出频率转换具体流程见附录二五.系统测试通过脉冲clk2为被测频率输入,测试实验结果。

当clk2为1HZ时,数码管显示输出频率为0.999,并且LED1和LED22盏灯都是暗的,即此时单位为HZ.当clk2为128HZ时,数码管显示输出频率为0.127,并且LED1和LED22盏灯都是暗的,即此时单位为HZ.当clk2为1024HZ时,数码管显示输出频率为1.023,并且此时灯LED1变亮,即此时单位为KHZ。

目录摘要 (1)1、设计原理 (2)1.1设计目的 (2)1.2设计原理 (2)2、设计任务 (3)2.1设计任务要求 (3)2.2预置门控信息设计要求 (3)3、等精度频率计测频实现 (3)3.1预置门控信息CL的实现 (3)3.2主系统组成测频实现 (4)4、仿真波形及结果分析 (6)4.1仿真波形及分析 (6)4.1.1预置门控信息CL的仿真波形 (6)4.1.2主系统组成测频的仿真波形 (6)4.1.3门控高电平期间预测信号个数显示 (7)4.1.4门控高电平期间标准信号个数显示 (7)5、小结与体会 (7)6、参考文献 (8)等精度频率计摘要基于传统测频原理的频率计的测量精度随被测信号的频率的变化而变化,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,且在整个频率区域能保持恒定的测量精度。

在一段高电平使能端期间(时间为pr T )同时启动和关闭标准频率计数器和预测频率计数器。

预测信号的计数值为x N ,标准频率信号的计数值为s N ,则可得到测试频率为x s s x N N F F ⨯=)/(。

关键字:等精度频率计 计数器1、设计原理1.1设计目的基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,即测量精度随被测信号的频率的变化而变化,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,且在整个频率区域能保持恒定的测量精度。

设计项目可达到指标:频率测试功能:测频范围0.1Hz~100MHz。

测频精度0.01us。

1.2设计原理等精度测评原理可以简单的用图1来说明,图1中的“预置门控信息”CL由编程控制,可以证明,在1s至0.1s间的选择范围内,CL的时间宽度,对测评精度几乎没有影响,在此,设其宽度为T。

BZH和TF模块是两个可控的32位高pr速计数器,ENA是它们的计数允许信号端,高电平有效。

标准频率信号,从BZHF:经整形后的被测信号从与BZH相似的时钟输入端BCLK输入,设其频率为s的32位计数器TF 的时钟输入端TCLK 输入,设其真实频率值为xe F ,被测频率为x F ,等精度测评原理说明如下:图1 等精度频率计原理图测频开始前,首先发出一个清零信号CLR ,使两个计数器和D 触发器置零,同时D 触发器通过信号ENA ,禁止两个计数器计数。