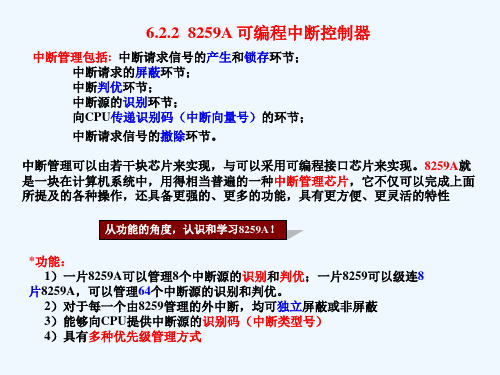

第9章(2) 中断系统和中断控制器8259A

- 格式:ppt

- 大小:852.50 KB

- 文档页数:64

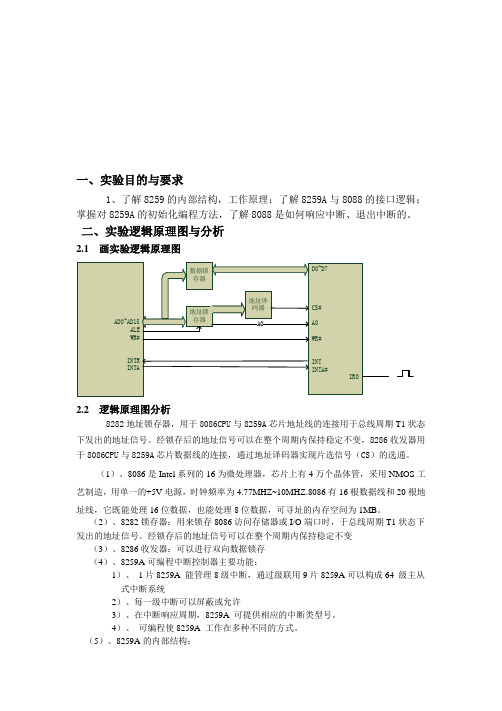

一、实验目的与要求1、了解8259的内部结构,工作原理;了解8259A 与8088的接口逻辑;掌握对8259A 的初始化编程方法,了解8088是如何响应中断、退出中断的。

二、实验逻辑原理图与分析 2.1 画实验逻辑原理图AD0~AD15ALEWR#INTR INTA数据锁存器地址锁存器地址译码器D0~D7CS#A0WR#INT INTA#IR0A02.2 逻辑原理图分析8282地址锁存器,用于8086CPU 与8259A 芯片地址线的连接用于总线周期T1状态下发出的地址信号。

经锁存后的地址信号可以在整个周期内保持稳定不变,8286收发器用于8086CPU 与8259A 芯片数据线的连接,通过地址译码器实现片选信号(CS )的选通。

(1)、8086是Intel 系列的16为微处理器,芯片上有4万个晶体管,采用NMOS 工艺制造,用单一的+5V 电源,时钟频率为4.77MHZ~10MHZ.8086有16根数据线和20根地址线,它既能处理16位数据,也能处理8位数据,可寻址的内存空间为1MB 。

(2)、8282锁存器:用来锁存8086访问存储器或I/O 端口时,于总线周期T1状态下发出的地址信号。

经锁存后的地址信号可以在整个周期内保持稳定不变 (3)、8286收发器:可以进行双向数据锁存 (4)、8259A 可编程中断控制器主要功能:1)、 1片8259A 能管理8级中断,通过级联用9片8259A 可以构成64 级主从 式中断系统2)、每一级中断可以屏蔽或允许3)、在中断响应周期,8259A 可提供相应的中断类型号。

4)、 可编程使8259A 工作在多种不同的方式。

(5)、8259A 的内部结构:1)、IRR:当IR0-IR7某一个引脚上出现有效中断请求时,IRR对应位被置12)、IMR:当IR0-IR7中需要屏蔽的,IMR对应位置13)、ISR:是一个8位寄存器,通过8位二进制数的值纪录当前正在处理的中断请求。

8259中断控制器Overview前言8259A芯片是一个中断管理芯片,中断的来源除了来自于硬件自身的NMI中和来自于软件的INT n指令造成的软件中断之外,还有来自于外部硬件设备的中断,这些中断的可屏蔽的。

这些中断也都通过PIC(Programmable Interrupt Controller)进行控制,并传递给CPU。

一个8259A芯片最多可接收8个中断源,但由于可以将2个或多个8259A芯片进行级连(cascade),并且最多可以级链到9个,所以最多可以接64个中断源。

如今绝大多数的PC 都拥有2个8259A,这样最多可以接收15个中断源。

通过8259A可以对单个中断源进行屏蔽。

在一个8259A芯片上有如下几个内部的寄存器:1.Interrupt Mask Register(IMR)。

2.Interrupt Request Register(IRR)。

3.In Service Register(ISR)。

IMR被用作过滤被屏蔽的中断,IRR被用作暂时放置未被进一步处理的Interrupt,当一个Interrupt正在被CPU处理时,此中断被放置在ISR中。

除了这几个寄存器之外,8259A还有一个单元叫做Priority Resolver,当多个中断同时发生时,Priority Resolver根据它们的优先级,将最高优先级的优先传递给CPU。

工作原理当一个中断请求从IR0到IR7中的某根线到达IMR时,IMR首先判断IR是否被屏蔽,如果被屏蔽,则此中断请求被丢弃;否则,则将放入IRR中。

在此中断请求不能进行下一步处理之前,它一直被放置在IRR中。

一旦发现处理中断的时机已到,Priority Resolver将从所有被放置于IRR中的中断中挑选出一个优先级最高的中断,将其传递给CPU去处理。

IR号越低的中断优先级级别越高,比如IR0的优先级是最高的。

8259A通过发送一个INTR(Interrupt Request)信号给CPU,通知CPU有一个中断到达。

说明8259a中断控制器中的irr、isr和imr三个寄存器的功能8259A中断控制器是一种常用的外部设备,用于管理和分发系统中的中断请求。

它有三个重要的寄存器:IRR(中断请求寄存器)、ISR (中断服务寄存器)和IMR(中断屏蔽寄存器),这些寄存器在控制和处理中断时起到关键作用。

IRR寄存器(Interrupt Request Register)用于存储当前发生的中断请求。

每个位都对应一个中断源,当某个外部设备发出中断请求时,对应位会被置为1。

CPU可以通过读取IRR寄存器来检测当前的中断请求状态,以确定哪个中断源需要被处理。

ISR寄存器(Interrupt Service Register)用于记录正在被CPU处理的中断源。

当中断请求被CPU接受后,对应的中断源的位会被置为1,表示该中断正在被处理。

ISR寄存器的内容可以帮助CPU追踪当前正在处理的中断,以避免同时处理多个中断源。

IMR寄存器(Interrupt Mask Register)用于屏蔽中断请求。

每个位对应一个中断源,当对应位被置为1时,表示该中断源被屏蔽,即中断请求不会被接受。

通过设置IMR寄存器,CPU可以选择性地屏蔽或允许特定的中断源。

通过IRR、ISR和IMR这三个寄存器的配合使用,8259A中断控制器可以有效地管理和分发系统中的中断请求。

CPU可以通过读取IRR寄存器来检测中断请求,并根据IMR寄存器的设置来确定是否屏蔽某个中断源。

当CPU接受一个中断请求后,会将对应的中断源的位设置为1,并在ISR寄存器中记录下来,以便追踪和处理当前的中断。

当中断处理完成后,CPU会清除ISR寄存器中的相应位,表示中断已经处理完毕。

通过使用这些寄存器,8259A中断控制器可以实现多个中断源的优先级管理、中断请求的屏蔽和中断处理的跟踪。

这些功能对于保证系统可靠性和提高系统的响应能力非常重要。

实验四中断控制器8259A一、实验目的1、掌握中断控制器8259A与微机接口的原理和方法。

2、掌握中断控制器8259A的应用编程。

二、实验设备DVCC系列微机仿真实验系统三、实验内容1.实验原理本系统中已设计有一片8259A中断控制芯片,工作于主片方式,8个中断请求输入端IR0~IR7对应的中断型号为8~F,其和中断矢量关系如下表3-3所示。

根据实验原理图,8259A和8088系统总线直接相连,8259A 上连有一系统地址线A0,故8259A 有2 个端口地址,本系统中为60H、61H。

60H 用来写ICW1,61H 用来写ICW2、ICW3、ICW4,初始化命令字写好后,再写操作命令字。

OCW2、OCW3 用口地址60H,OCW1用口地址61H。

图3-12中,使用了3号中断源,IR3插孔和SP 插孔相连,中断方式为边沿触发方式,每按一次AN按钮产生一次中断信号,向8259A 发出中断请求信号。

如果中断源电平信号不符规定要求则自动转到7号中断,显示“Err”。

CPU响应中断后,在中断服务中,对中断次数进行计数并显示,计满5次结束,显示器显示“Good”。

2、实验线路连接(1)8259模块上的INT连8088的INTR(在主板键盘矩阵下面)。

(2)8259模块上的INTA连8088的INTA(在主板键盘矩阵下面)。

(3)MP区SP插孔和8259的3号中断IR3插孔相连,SP端初始为低电平。

(4)8259模块上的D0~D7连到BUS 2区的XD0~XD7。

(5)8259模块上的CS端接Y6。

(6)8259模块上的A0连到BUS 区的XA0上。

(7)8259模块上的RD、WR信号线分别连到BUS 3区的XRD、XWR上。

四、实验步骤1、按图连好实验线路2、运行实验程序(1)联机时,实验程序文件名为\DVCC\H8EXE\H86S.EXE。

(2)单机时,实验程序起始地址为F000:91A0。

在系统显示监控提示符“P.”时:输入F000 按F1键输入91A0 按EXEC键在系统上显示“8259-1”。