EDA技术实用教程

- 格式:ppt

- 大小:1004.50 KB

- 文档页数:71

eda技术实用教程Part 1 EDA技术实用教程数据预处理一直是数据科学家中重要的任务之一。

因此,掌握数据预处理技能是必要的,而EDA(探索性数据分析)要比其他技术更为必要。

在这篇文章中,我们将介绍EDA的概念以及如何运用它来处理数据集。

我们还将介绍一些流行的EDA工具,以及如何在Python中使用这些工具。

探索性数据分析EDA是指探索性数据分析,是指分析数据以了解其特性的过程。

它有助于数据科学家洞察数据的基本特征,并为进一步的预测或分类建模做好准备。

EDA可以发现数据集中的异常值、缺失值或异常分布。

EDA工具大部分是可视化工具,能够帮助数据科学家更好地理解数据集。

EDA的主要目标如下:1.理解数据集的基本特征2.识别异常值和缺失值3.确定不同特征之间的关系4.绘制可视化图表,揭示数据分布模式EDA的实践在本节中,我们将介绍如何使用Python实施EDA技术。

安装Python和Jupyter Notebook首先,您应该安装Python和Jupyter Notebook。

这些是数据科学家日常工作所需的。

安装pandas和matplotlib在开始EDA之前,您需要确保安装了pandas和matplotlib这两个库。

它们是Python中的重要数据科学库,可以帮助您方便地读取和可视化数据。

pip install pandaspip install matplotlib读取数据集下面是一个读取数据集的例子。

import pandas as pddata=pd.read_csv("data.csv")数据集可视化在这里,我们将介绍如何使用Python中的matplotlib 库来可视化数据集。

散点图散点图是一个可视化数据关系的好方法。

在Python中,可以使用以下代码为两个变量(x和y)绘制散点图。

import matplotlib.pyplot as pltx=data['x']y=data['y']plt.scatter(x,y)plt.show()我们可以看到,在数据集中,x和y有一个很强的正相关关系。

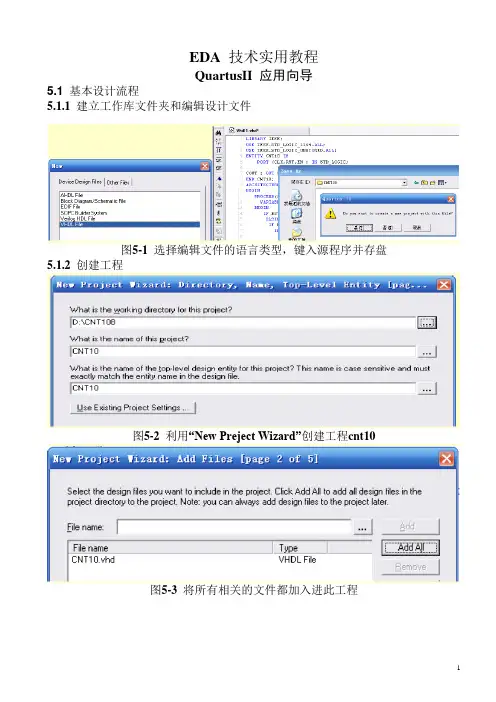

EDA 技术实用教程QuartusII 应用向导5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件图5-1 选择编辑文件的语言类型,键入源程序并存盘5.1.2 创建工程图5-2 利用“New Preject Wizard”创建工程cnt10图5-3 将所有相关的文件都加入进此工程图5-4 选择目标器件EP2C5T144C8图5-5 将Max+plusII工程转换为QuartusII工程5.1.3 编译前设置图5-6 选择目标器件EP2C5T144C8图5-7选择配置器件的工作方式图5-8 选择配置器件和编程方式5.1.4 全程编译图5-9 全程编译后出现报错信息5.1.5 时序仿真图5-10 选择编辑矢量波形文件图5-11 波形编辑器图5-12 设置仿真时间长度图5-13 vwf激励波形文件存盘图5-14 向波形编辑器拖入信号节点图5-15 设置时钟CLK的周期图5-16 选择总线数据格式图5-17设置好的激励波形图图5-18 选择仿真控制图5-19 仿真波形输出图5-20 选择全时域显示5.1.6 应用RTL电路图观察器图5-21 cnt10工程的RTL电路图5.2 引脚设置和下载5.2.1 引脚锁定图5-22 GW48实验系统模式5实验电路图图5-23 Assignment Editor编辑器图5-24 两种引脚锁定对话框5.2.2 配置文件下载图5-25 选择编程下载文图5-26加入编程下载方式图5-27 双击选中的编程方式名图5-28 ByteBlasterII编程下载窗5.2.3 AS模式编程配置器件图5-29 ByteBlaster II接口AS模式编程窗口5.2.4 JTAG间接模式编程配置器件图5-30 选择目标器件EP2C5T144图5-31 选定SOF文件后,选择文件压缩图5-32 用JTAG模式对配置器件EPCS1进行间接编程5.2.5 USB Blaster编程配置器件使用方法图5-33 安装USB驱动程序图5-34 设置JTAG硬件功能图5-35 在In-System Memory Content Editor中使用USB Blaster 5.3 嵌入式逻辑分析仪使用方法1.打开SignalTap II编辑窗图5-36 SignalTap II编辑窗2.调入待测信号3.SignalTap II参数设置图5-37 SignalTap II编辑窗4.文件存盘图5-38 设定SignalTap II与工程一同综合适配5.编译下载6.启动SignalTap II进行采样与分析图5-39 下载cnt10.sof并准备启动SignalTap II图5-40 SignalTap II采样已被启动7.SignalTap II的其他设置和控制方法图5-41 SignalTap II数据窗设置后的信号波形5.4 原理图输入设计方法5.4.1 设计流程1. 为本项工程设计建立文件夹假设本项设计的文件夹取名为adder,路径为:d:\adder。

EDA技术实用教程第二版课程设计EDA(Electronic Design Automation)是一种电子设计自动化技术,旨在提高电路设计的效率和准确性。

EDA 类软件工具覆盖了从原理图到布局的整个电路设计过程,并支持从模拟到数字电路设计和 FPGA 开发。

本文旨在介绍 EDA 技术的相关实用教程,帮助初学者更好地掌握该技术。

在第二版中,我们将会以课程设计的形式展示这些实用教程。

第一章电路设计基础电路设计是一个非常复杂的过程,需要掌握一定的电路设计基础知识。

课程设计的第一章节会介绍一些基础知识。

1.1 电子元器件与电路在学习电路设计之前,我们需要了解一些电子元器件的基本知识。

在 EDA 软件中,我们可以选择需要的元器件并进行设计。

1.2 原理图设计原理图是电路设计的基础。

在 EDA 软件中,我们可以通过画原理图的方式来完成电路设计。

该部分将会详细介绍原理图设计的流程与注意事项。

第二章 PCB 设计PCB(Printed Circuit Board)也是电路设计的重要组成部分。

在 EDA 软件中,我们可以使用 PCB 设计工具完成 PCB 设计。

本章节将会介绍关于 PCB 设计的相关技巧与实用教程。

2.1 PCB 布局设计在 PCB 设计中,布局设计是非常重要的一步。

良好的布局设计可以减小电路杂散耦合、减小交叉干扰、增大分布容量等。

该部分将会详细介绍布局设计的注意事项。

2.2 PCB 元件布局元件布局是 PCB 设计的重要部分,需要根据电路的要求进行选取和布局。

该部分将会介绍 PCB 元件布局的技巧与实用教程。

第三章 FPGA 开发FPGA(Field Programmable Gate Array)是一种可编程逻辑芯片,广泛应用于数字电路设计领域。

在 EDA 软件中,我们可以使用 FPGA 开发工具进行 FPGA 设计。

本章节将会介绍关于 FPGA 开发的相关技巧与实用教程。

3.1 Verilog 语言入门Verilog 语言是 FPGA 开发中常用的一种硬件描述语言,也是我们必须掌握的一部分。

《EDA技术实用教程(第五版)》课后习题及答案1 习题1-1EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~4EDA技术与ASIC设计和FPGA开发有什么关系?答:利用EDA 技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

FPGA在ASIC设计中有什么用途?答:FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA实现ASIC设计的现场可编程器件。

1-2 与软件描述语言相比,VHDL有什么特点? P4~6 答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P6什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

《EDA技术实用教程(第四版)》习题1 习题1-1EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~41-2 与软件描述语言相比,VHDL有什么特点? P6l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P51-4 在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~101-5 IP在EDA技术的应用和发展中的意义是什么? P22~141-6叙述EDA的FPGA/CPLD设计流程,以及涉及的EDA工具及其在整个流程中的作用。

(P11~13)2 习题2-1OLMC(输出逻辑宏单元)有何功能?说明GAL是怎样实现可编程组合电路与时序电路的。

P34~362-2什么是基于乘积项的可编程逻辑结构?P33~34,40什么是基于查找表的可编程逻辑结构?P40~412-3FPGA系列器件中的LAB有何作用? P43~452-5 解释编程与配置这两个概念。

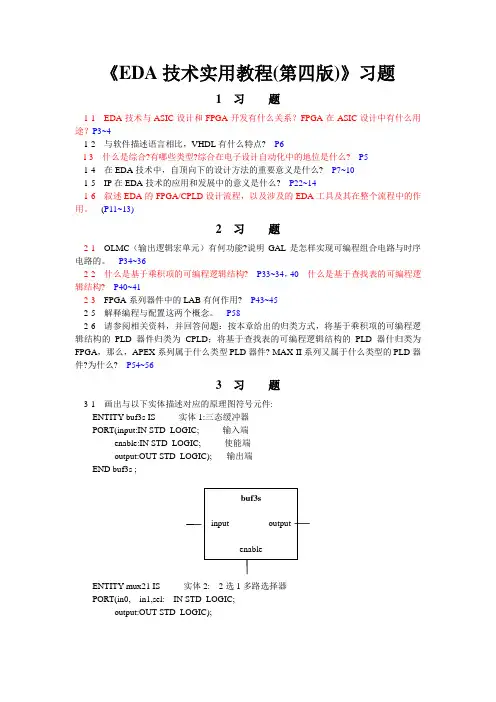

P582-6 请参阅相关资料,并回答问题:按本章给出的归类方式,将基于乘积项的可编程逻辑结构的PLD器件归类为CPLD;将基于查找表的可编程逻辑结构的PLD器什归类为FPGA,那么,APEX系列属于什么类型PLD器件? MAX II系列又属于什么类型的PLD器件?为什么? P54~563 习题3-1 画出与以下实体描述对应的原理图符号元件:ENTITY buf3s IS --实体1:三态缓冲器PORT(input:IN STD_LOGIC; --输入端enable:IN STD_LOGIC; --使能端output:OUT STD_LOGIC); --输出端END buf3s ;ENTITY mux21 IS --实体2: 2选1多路选择器PORT(in0, in1,sel: IN STD_LOGIC;output:OUT STD_LOGIC);mux21in0outputin1sel3-2 图3-16所示的是4选1多路选择器,试分别用IF_THEN语句和CASE语句的表达方式写出此电路的VHDL程序,选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=’0’,s0=’0’;s1=’0’,s0=’1’;s1=’1’,s0=’0’和s1=’1’,s0=’1’时,分别执行y<=a、y<=b、y<=c、y<=d。

《EDA技术实用教程(第五版)》课后习题及答案1 习题1-1EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~4EDA技术与ASIC设计和FPGA开发有什么关系?答:利用EDA 技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

FPGA在ASIC设计中有什么用途?答:FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA实现ASIC设计的现场可编程器件。

1-2 与软件描述语言相比,VHDL有什么特点? P4~6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P6什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。