eda技术实用教程(第四版)课件8

- 格式:pdf

- 大小:1.25 MB

- 文档页数:51

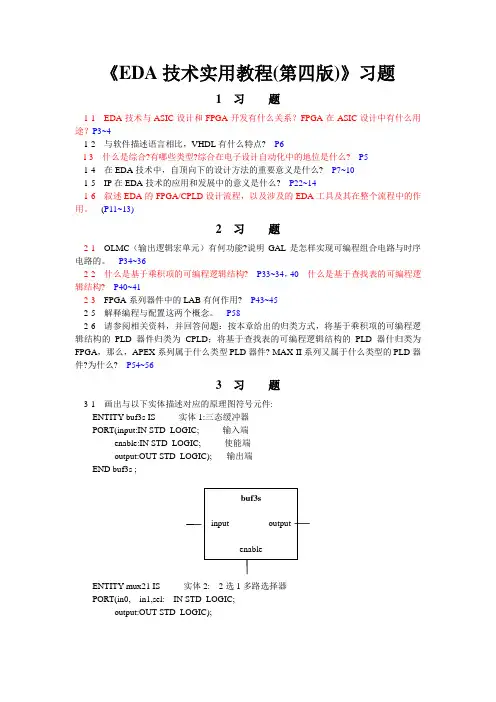

《EDA技术实用教程(第四版)》习题1 习题1-1EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~41-2 与软件描述语言相比,VHDL有什么特点? P6l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P51-4 在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~101-5 IP在EDA技术的应用和发展中的意义是什么? P22~141-6叙述EDA的FPGA/CPLD设计流程,以及涉及的EDA工具及其在整个流程中的作用。

(P11~13)2 习题2-1OLMC(输出逻辑宏单元)有何功能?说明GAL是怎样实现可编程组合电路与时序电路的。

P34~362-2什么是基于乘积项的可编程逻辑结构?P33~34,40什么是基于查找表的可编程逻辑结构?P40~412-3FPGA系列器件中的LAB有何作用? P43~452-5 解释编程与配置这两个概念。

P582-6 请参阅相关资料,并回答问题:按本章给出的归类方式,将基于乘积项的可编程逻辑结构的PLD器件归类为CPLD;将基于查找表的可编程逻辑结构的PLD器什归类为FPGA,那么,APEX系列属于什么类型PLD器件? MAX II系列又属于什么类型的PLD器件?为什么? P54~563 习题3-1 画出与以下实体描述对应的原理图符号元件:ENTITY buf3s IS --实体1:三态缓冲器PORT(input:IN STD_LOGIC; --输入端enable:IN STD_LOGIC; --使能端output:OUT STD_LOGIC); --输出端END buf3s ;ENTITY mux21 IS --实体2: 2选1多路选择器PORT(in0, in1,sel: IN STD_LOGIC;output:OUT STD_LOGIC);mux21in0outputin1sel3-2 图3-16所示的是4选1多路选择器,试分别用IF_THEN语句和CASE语句的表达方式写出此电路的VHDL程序,选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=’0’,s0=’0’;s1=’0’,s0=’1’;s1=’1’,s0=’0’和s1=’1’,s0=’1’时,分别执行y<=a、y<=b、y<=c、y<=d。

第8章有限状态机设计技术有限状态机及其设计技术是实用数字系统设计中的重要组成部分,也是实现高效率、高可靠和高速控制逻辑系统的重要途径。

广义而论,只要是涉及触发器的电路,无论电路大小,都能归结为状态机。

因此,对于数字系统设计工程师,面对的只要是时序电路设计,状态机的概念则是必须贯穿于整个设计始终的最基本的设计思想和设计方法论;只有从电路状态的角度去考虑,才能从根本上把握可靠,高效的时序逻辑的设计关键。

在现代数字系统设计中,状态机的设计对系统的高速性能、高可靠性、稳定性都具有决定性的作用。

读者对于此章的学习必须给于高度的关注。

有限状态机应用广泛,特别是对那些操作和控制流程非常明确的系统设计,在数字通信领域、自动化控制领域、CPU设计领域以及家电设计领域都拥有重要的和不可或缺的地位。

尽管到目前为止,有限状态机的设计理论并没有增加多少新的内容,然而面对先进的EDA工具、日益发展的大规模集成电路技术和强大的硬件描述语言,有限状态机在其具体的设计和优化技术以及实现方法上却有了许多新的内容和新的实现方法。

本章重点介绍用Verilog设计不同类型有限状态机的方法,同时考虑EDA工具和设计实现中许多必须重点关注的问题,如优化、毛刺的处理及编码方式等方面的问题。

8.1 Verilog状态机的一般形式就理论而言,任何时序模型都可以归结为一个状态机。

如只含一个D触发器的二分频电路或一个普通的4位二进制计数器都可算作一个状态机;前者是两状态型状态机,后者是16状态型状态机,都属于一般状态机的特殊形式。

但这些并非出自明确的自觉的设计目的和合理的状态机设计方案而导致的时序模块,未必能成为一高速、高效、稳定、控制流畅、修改便捷和功能目标明确的真正意义上的状态机。

基于现代数字系统设计技术自觉意义上的状态机的HDL表述形态和表述风格具有一定的典型性和格律化。

正是据此,现代EDA的综合器能从不同表述形态的HDL程序中轻易地萃取出(Extract)状态机设计,并加以多侧面多目标和多种形式的优化;甚至还能能动地改变、脱离甚至不遵从设计程序文字上的表述,而按照综合器自己的方式去优化状态机的设计。

第1章硬件描述语言VHDL数字系统设计分为硬件设计和软件设计, 但是随着计算机技术、超大规模集成电路(CPLD、FPGA)的发展和硬件描述语言(HDL, Hardware Description Language)的出现,软、硬件设计之间的界限被打破,数字系统的硬件设计可以完全用软件来实现,只要掌握了HDL语言就可以设计出各种各样的数字逻辑电路。

1.1老的硬件设计方法老的硬件设计方法有如下几个特征:(1)采用自下而上的设计方法使用该方法进行硬件设计是从选择具体元器件开始,并用这些元器件进行逻辑电路设计,从而完成系统的硬件设计,然后再将各功能模块连接起来,完成整个系统的硬件设计,(2)采用通用逻辑元器件通常采用74系列和CMOS4000系列的产品进行设计(3)在系统硬件设计的后期进行调试和仿真只有在部分或全部硬件电路连接完毕,才可以进行电路调试,一旦考虑不周到,系统设计存在较大缺陷,则要重新设计,使设计周期延长。

(4)设计结果是一张电路图当设计调试完毕后,形成电原理图,该图包括元器件型号和信号之间的互连关系等等。

老的硬件设计方法已经使用了几十年,是广大电子工程师熟悉和掌握的一种方法,但是现在这种方法老了,不仅方法老了,就连使用的元器件也老了。

1.2使用HTL的硬件设计方法所谓硬件描述语言,就是利用一种人和计算机都能识别的语言来描述硬件电路的功能,信号连接关系及定时关系,它可以比电原理图更能表示硬件电路的特性。

该方法有如下特征:(1)支持自顶向下的设计方法所谓自顶向下的设计方法就是从系统的总体要求出发,自顶向下分三个层次对系统硬件进行设计。

第一个层次是行为描述,所谓行为描述,实际就是对整个系统的数学模型的描述,在行为描述阶段,并不真正考虑其实际操作和算法怎么实现,而是考虑系统的结构和工作过程是否能达到系统设计规格书的要求。

第二个层次是数据流描述,又称为寄存器描述或RTL方式描述,该描述比行为描述更注重硬件的具体实现,通过该描述可以导出系统的逻辑表达式,为逻辑综合作准备,当然进行逻辑综合和逻辑综合工具的能力有关,当然设计人员还必须了解逻辑综合工具的说明和规定,第三个层次为逻辑综合。