EDA技术实用教程第4版VHDL课件第2章

- 格式:pdf

- 大小:1.20 MB

- 文档页数:56

EDA技术实用教程-VerilogHDL版第四版课程设计一、背景介绍EDA技术(Electronic Design Automation)是指电子设计自动化技术,它是电子设计工程师在工作中必不可少的技术。

EDA技术让电子设计工程师能够更快、更准确和更高效地创建电子原型和系统级设计。

EDA技术的应用包括了芯片设计、数字信号处理、嵌入式系统和PCB设计等。

在EDA技术的发展历程中,Verilog HDL成为了实际应用中最为普及、最为有效的HDL语言。

二、课程设计目标本次课程设计的目标是通过实际案例,帮助学生掌握Verilog HDL设计方法、EDA设计流程以及EDA工具的应用,最终形成独立设计能力和技术素养。

同时,通过课程设计,提高学生综合能力,包括解决问题的能力、分析问题的能力等。

三、课程设计内容和步骤1.课程设计第一阶段:确定设计目标及功能需求在这一阶段,学生需要做的是梳理出设计要求及功能需求,包括指定设计的模块、所完成的功能、输入输出的端口要求,以及需要达到的功能性能等。

2.课程设计第二阶段:Verilog HDL设计在这一阶段,学生需要学习Verilog HDL语言,包括基础语法、模块框架、变量、运算符、组合逻辑和时序逻辑、宏定义以及模块连接等。

学生需要根据课程设计要求,选择合适的Verilog HDL代码实现方式,进行模块组件的设计。

3.课程设计第三阶段:仿真验证在这一阶段,学生需要学习EDA工具,包括ModelSim等较为流行的仿真工具的使用,运用所学工具对设计的模块组件进行仿真和测试,以验证和调试设计的正确性。

4.课程设计第四阶段:芯片布局设计、综合与验证在这一阶段,学生需要学习EDA工具,如Synopsys等较为流行的工具的应用,进行芯片综合、硬件描述语言优化、延时优化以及布局等操作,以完成设计的验证。

四、设计案例以下为一个简单的数字电路设计案例,学生可以根据这个案例进行课程设计实践。

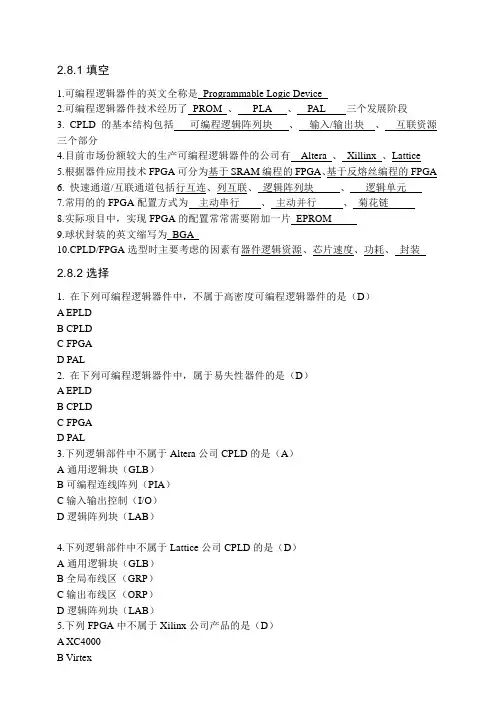

2.8.1填空1.可编程逻辑器件的英文全称是Programmable Logic Device2.可编程逻辑器件技术经历了PROM 、PLA、PAL 三个发展阶段3. CPLD的基本结构包括可编程逻辑阵列块、输入/输出块、互联资源三个部分4.目前市场份额较大的生产可编程逻辑器件的公司有Altera 、Xillinx 、Lattice5.根据器件应用技术FPGA可分为基于SRAM编程的FPGA、基于反熔丝编程的FPGA6. 快速通道/互联通道包括行互连、列互联、逻辑阵列块、逻辑单元7.常用的的FPGA配置方式为主动串行、主动并行、菊花链8.实际项目中,实现FPGA的配置常常需要附加一片EPROM9.球状封装的英文缩写为BGA10.CPLD/FPGA选型时主要考虑的因素有器件逻辑资源、芯片速度、功耗、封装2.8.2选择1. 在下列可编程逻辑器件中,不属于高密度可编程逻辑器件的是(D)A EPLDB CPLDC FPGAD PAL2. 在下列可编程逻辑器件中,属于易失性器件的是(D)A EPLDB CPLDC FPGAD PAL3.下列逻辑部件中不属于Altera公司CPLD的是(A)A通用逻辑块(GLB)B可编程连线阵列(PIA)C输入输出控制(I/O)D逻辑阵列块(LAB)4.下列逻辑部件中不属于Lattice公司CPLD的是(D)A通用逻辑块(GLB)B全局布线区(GRP)C输出布线区(ORP)D逻辑阵列块(LAB)5.下列FPGA中不属于Xilinx公司产品的是(D)A XC4000B Virtex• 2 •第1章概述C SpartanD Cyclong6. 下列FPGA中不属于Alter公司产品的是(B)A FLEX 10KB VirtexC StratixD Cyclone7.下列配置方式不属于FPGA配置模式的是(D)A主动串行配置模式B被动串行配置模式C主动并行配置模式D被动从属配置模式8.下列因素中通常不属于CPLD/FPGA选型条件的是(D)A逻辑资源B 功耗和封装C 价格和速度D 产地2.8.3问答1.结合本章学习的知识,简述CPLD的基本结构?答:虽然CPLD种类繁多、特点各异,共同之处总结起来可以概括为三个部分:●可编程逻辑阵列块;●输入/输出块;●互联资源;其中,可编程逻辑阵列块类似于一个低密度的PAL/GAL,包括乘积项的与阵列、乘积项分配和逻辑宏单元等。

第一章 EDA 基础知识1.EDA 技术概念答:利用EDA技术可以实现专用集成电路ASIC的设计和实现(FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD 的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

)2. EDA 技术发展的 3 个阶段(CAD , CAE ,EDA)答:(1)20世纪70年代:CAD阶段-CAD概念已见雏形,人们开始利用计算机及取代手工劳动,辅助进行集成电路板图编辑、PCB(印制电路板)布局布线等工作。

(2)20世纪80年代:CAE阶段。

(3)20世纪90年代:EDA阶段。

3. EDA 技术实现目标答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC或印制电路板(PCB)的设计和实现(图1-1)。

4.EDA 技术实现目标的途径答:(1)可编程逻辑器件:;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

(2)半定制或全定制ASICa:门阵列ASICb:标准单元ASIC(3)混合ASIC5.硬件描述语言答: VHDL、Verilog HDL、SystemVerilog、System C6. VERILOG HDL的发展过程(1)含义(2)创建时间答:1983年、创建公司:Gateway Design Automation(GDA)(3)特点:答:a:参照C语言的语法设立的(但与C有本质的区别)b:代码简明扼要,使用灵活,且语法规定不是很严谨,很容易上手。

c:具有很强的电路描述和建模能力。

7. VERILOG HDL 的设计方法,分为哪几个阶段答:8.自顶向下,自底向上方法比较答:自底向上:低效、低可靠性、费时费力、成本高昂。