微机原理与接口技术 第三章 课后作业答案

- 格式:ppt

- 大小:99.50 KB

- 文档页数:12

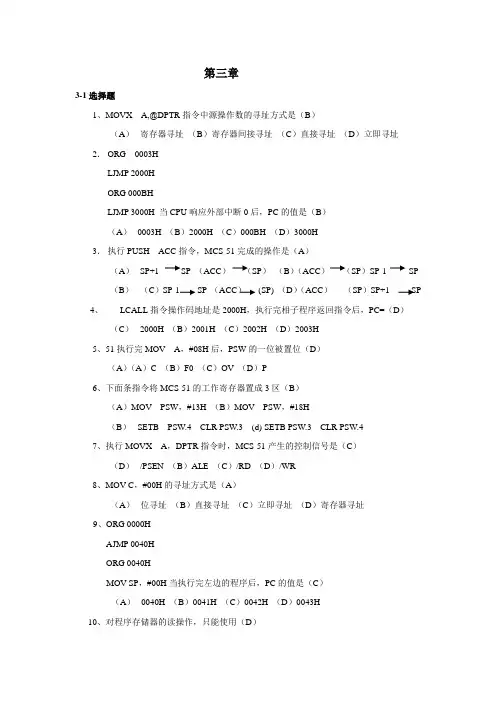

第三章3-1选择题1、MOVX A,@DPTR指令中源操作数的寻址方式是(B)(A)寄存器寻址(B)寄存器间接寻址(C)直接寻址(D)立即寻址2.ORG 0003HLJMP 2000HORG 000BHLJMP 3000H 当CPU响应外部中断0后,PC的值是(B)(A)0003H (B)2000H (C)000BH (D)3000H3.执行PUSH ACC指令,MCS-51完成的操作是(A)(A)SP+1 SP (ACC)(SP)(B)(ACC)(SP)SP-1 SP(B)(C)SP-1 SP (ACC)(SP) (D)(ACC)(SP)SP+1 SP4、LCALL指令操作码地址是2000H,执行完相子程序返回指令后,PC=(D)(C)2000H (B)2001H (C)2002H (D)2003H5、51执行完MOV A,#08H后,PSW的一位被置位(D)(A)(A)C (B)F0 (C)OV (D)P6、下面条指令将MCS-51的工作寄存器置成3区(B)(A)MOV PSW,#13H (B)MOV PSW,#18H(B)SETB PSW.4 CLR PSW.3 (d) SETB PSW.3 CLR PSW.47、执行MOVX A,DPTR指令时,MCS-51产生的控制信号是(C)(D)/PSEN (B)ALE (C)/RD (D)/WR8、MOV C,#00H的寻址方式是(A)(A)位寻址(B)直接寻址(C)立即寻址(D)寄存器寻址9、ORG 0000HAJMP 0040HORG 0040HMOV SP,#00H当执行完左边的程序后,PC的值是(C)(A)0040H (B)0041H (C)0042H (D)0043H10、对程序存储器的读操作,只能使用(D)(A)MOV指令(B)PUSH指令(C)MOVX指令(D)MOVC指令3-2判断题。

4.MCS-51的相对转移指令最大负跳距是127B。

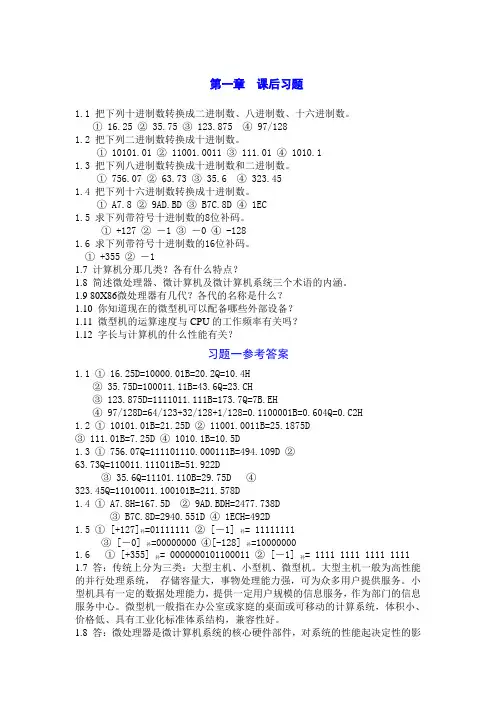

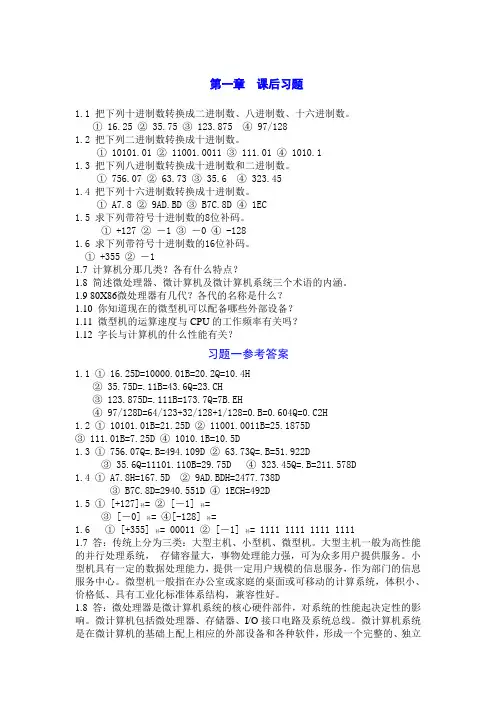

第一章课后习题1.1 把下列十进制数转换成二进制数、八进制数、十六进制数。

① 16.25 ② 35.75 ③ 123.875 ④ 97/1281.2 把下列二进制数转换成十进制数。

① 10101.01 ② 11001.0011 ③ 111.01 ④ 1010.11.3 把下列八进制数转换成十进制数和二进制数。

① 756.07 ② 63.73 ③ 35.6 ④ 323.451.4 把下列十六进制数转换成十进制数。

① A7.8 ② 9AD.BD ③ B7C.8D ④ 1EC1.5 求下列带符号十进制数的8位补码。

① +127 ② -1 ③ -0 ④ -1281.6 求下列带符号十进制数的16位补码。

① +355 ② -11.7 计算机分那几类?各有什么特点?1.8 简述微处理器、微计算机及微计算机系统三个术语的内涵。

1.9 80X86微处理器有几代?各代的名称是什么?1.10 你知道现在的微型机可以配备哪些外部设备?1.11 微型机的运算速度与CPU的工作频率有关吗?1.12 字长与计算机的什么性能有关?习题一参考答案1.1 ① 16.25D=10000.01B=20.2Q=10.4H② 35.75D=100011.11B=43.6Q=23.CH③ 123.875D=1111011.111B=173.7Q=7B.EH④ 97/128D=64/123+32/128+1/128=0.1100001B=0.604Q=0.C2H1.2 ① 10101.01B=21.25D ② 11001.0011B=25.1875D③ 111.01B=7.25D ④ 1010.1B=10.5D1.3 ① 756.07Q=111101110.000111B=494.109D ②63.73Q=110011.111011B=51.922D③ 35.6Q=11101.110B=29.75D ④323.45Q=11010011.100101B=211.578D1.4 ① A7.8H=167.5D ② 9AD.BDH=2477.738D③ B7C.8D=2940.551D ④ 1ECH=492D1.5 ① [+127]补=01111111 ② [-1]补= 11111111③ [-0]补=00000000 ④[-128]补=100000001.6 ① [+355]补= 0000000101100011 ② [-1]补= 1111 1111 1111 11111.7 答:传统上分为三类:大型主机、小型机、微型机。

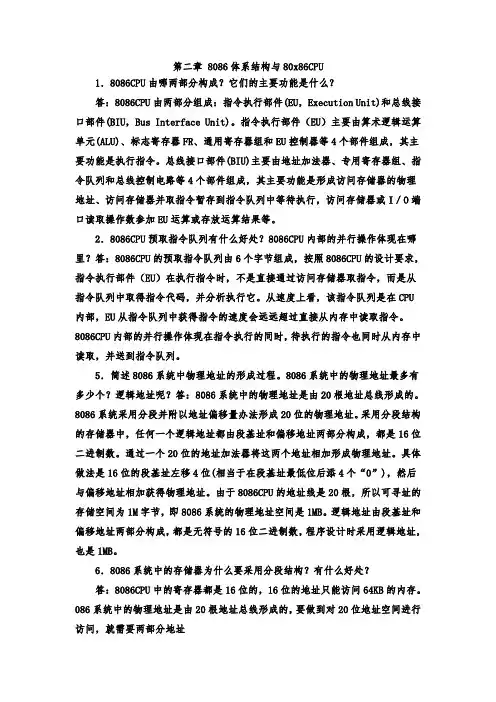

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

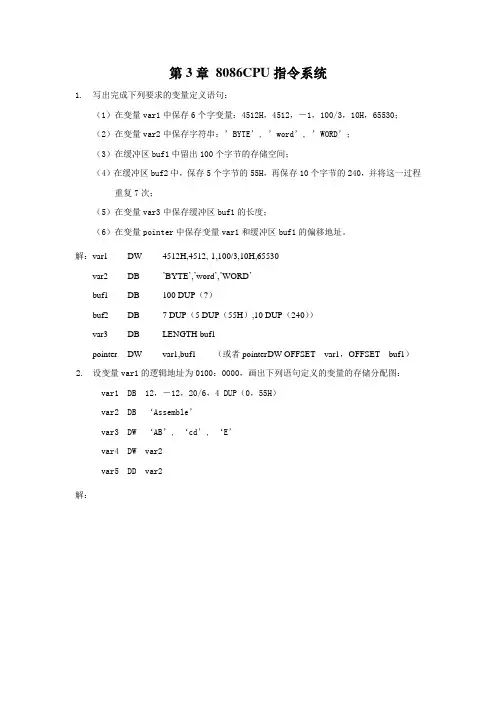

第3章8086CPU指令系统1.写出完成下列要求的变量定义语句:(1)在变量var1中保存6个字变量:4512H,4512,-1,100/3,10H,65530;(2)在变量var2中保存字符串:’BYTE’, ’word’, ’WORD’;(3)在缓冲区buf1中留出100个字节的存储空间;(4)在缓冲区buf2中,保存5个字节的55H,再保存10个字节的240,并将这一过程重复7次;(5)在变量var3中保存缓冲区buf1的长度;(6)在变量pointer中保存变量var1和缓冲区buf1的偏移地址。

解:var1 DW 4512H,4512,-1,100/3,10H,65530var2 DB ’BYTE’,’word’,’WORD’buf1 DB 100 DUP(?)buf2 DB 7 DUP(5 DUP(55H),10 DUP(240))var3 DB LENGTH buf1pointer DW var1,buf1 (或者pointer D W OFFSET var1,OFFSET buf1)2.设变量var1的逻辑地址为0100:0000,画出下列语句定义的变量的存储分配图:var1 DB 12,-12,20/6,4 DUP(0,55H)var2 DB ‘Assemble’var3 DW ‘AB’, ‘cd’, ‘E’var4 DW var2var5 DD var2解:3.指令正误判断,对正确指令写出源和目的操作数的寻址方式,对错误指令指出原因(设VAR1, VAR2为字变量, L1为标号):(1)MOV SI,100 (2)MOV BX,VAR1[SI](3)MOV AX, [BX] (4)MOV AL, [DX](5)MOV BP, AL (6)MOV VAR1, VAR2(7)MOV CS, AX (8)MOV DS, 0100H(9)MOV [BX][SI], 1 (10)MOV AX, VAR1+VAR2(11)ADD AX, LENGTH VAR1 (12)OR BL, TYPE VAR2(13)SUB [DI], 78H (14)MOVS VAR1, VAR2(15)PUSH 100H (16)POP CS(17)XCHG AX, ES (18)MOV DS, CS(19)JMP L1+5 (20)DIV AX, 10(21)SHL BL, 2 (22)MOV AL, 15+23(23)MUL CX (24)XCHG CL, [SI](25)ADC CS:[0100], AH (26)SBB VAR1-5,154解:(1)MOV SI,100 正确。

第1章绪论作业1. 将下列二进制数转换成十进制数。

(1)11001010B=202 (2)00111101B=61(3)01001101B=77 (4)10100100B=1643. 将下列十进制数分别转换为二进制数和十六进制数。

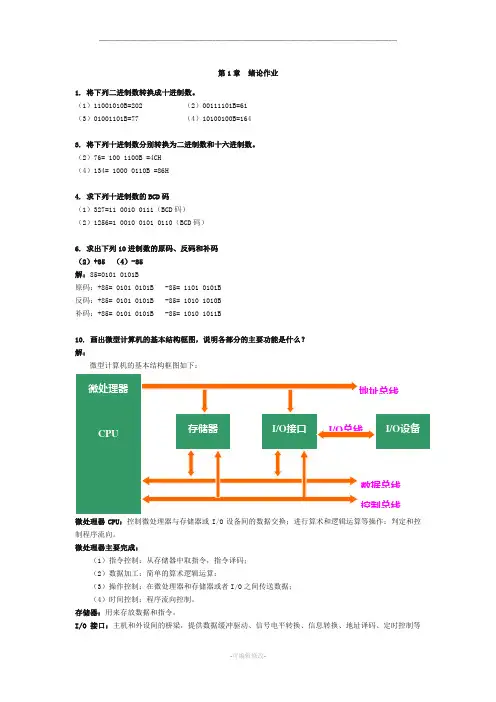

(2)76= 100 1100B =4CH(4)134= 1000 0110B =86H4. 求下列十进制数的BCD码(1)327=11 0010 0111(BCD码)(2)1256=1 0010 0101 0110(BCD码)6. 求出下列10进制数的原码、反码和补码(2)+85 (4)-85解:85=0101 0101B原码:+85= 0101 0101B -85= 1101 0101B反码:+85= 0101 0101B -85= 1010 1010B补码:+85= 0101 0101B -85= 1010 1011B10. 画出微型计算机的基本结构框图,说明各部分的主要功能是什么?解:微型计算机的基本结构框图如下:微处理器CPU:控制微处理器与存储器或I/O设备间的数据交换;进行算术和逻辑运算等操作;判定和控制程序流向。

微处理器主要完成:(1)指令控制:从存储器中取指令,指令译码;(2)数据加工:简单的算术逻辑运算;(3)操作控制:在微处理器和存储器或者I/O之间传送数据;(4)时间控制:程序流向控制。

存储器:用来存放数据和指令。

I/O接口:主机和外设间的桥梁,提供数据缓冲驱动、信号电平转换、信息转换、地址译码、定时控制等各种功能。

I/O设备:输入原始数据和程序,转换成计算机能识别的信息,送入存储器去等待处理。

输出运算结果。

总线:连接计算机系统中各功能部件的信息通道。

第2章 8086CPU作业2. 8086CPU内部由哪两部分组成?它们的大致是如何工作的?答:(1)8086CPU由指令执行部件EU和总线接口部件BIU两部分组成。

(2)① BIU先执行读存储器操作,从给定地址单元中取出指令,送到先进先出的指令队列中等待执行。

微机原理与接口技术习题解答第1章微型计算机系统〔习题〕简答题(1)计算机字长(Word)指的是什么(2)总线信号分成哪三组信号(3)PC机主存采用DRAM组成还是SRAM组成(4)Cache是什么意思(5)ROM-BIOS是什么(6)中断是什么(7)32位PC机主板的芯片组是什么(8)教材中MASM是指什么(9)处理器的“取指-译码-执行周期”是指什么(10)本课程的主要内容属于计算机系统层次结构中哪个层次〔解答〕①处理器每个单位时间可以处理的二进制数据位数称计算机字长。

②总线信号分成三组,分别是数据总线、地址总线和控制总线。

③ PC机主存采用DRAM组成。

④高速缓冲存储器Cache是处理器与主存之间速度很快但容量较小的存储器。

⑤ ROM-BIOS是“基本输入输出系统”,操作系统通过对BIOS的调用驱动各硬件设备,用户也可以在应用程序中调用BIOS中的许多功能。

⑥中断是CPU正常执行程序的流程被某种原因打断、并暂时停止,转向执行事先安排好的一段处理程序,待该处理程序结束后仍返回被中断的指令继续执行的过程。

⑦主板芯片组是主板的核心部件,它提供主板上的关键逻辑电路。

⑧ MASM是微软开发的宏汇编程序。

⑨指令的处理过程。

处理器的“取指—译码—执行周期”是指处理器从主存储器读取指令(简称取指),翻译指令代码的功能(简称译码),然后执行指令所规定的操作(简称执行)的过程。

⑩机器语言层,即指令集结构。

(学生很多认为是:汇编语言层。

前4章主要涉及汇编语言,但本书还有很多处理器原理等内容)〔习题〕判断题(1)软件与硬件的等价性原理说明软硬件在功能、性能和成本等方面是等价的。

(2)IA-64结构是IA-32结构的64位扩展,也就是Intel 64结构。

(3)8086的数据总线为16位,也就是说8086的数据总线的个数、或说条数、位数是16。

(4)微机主存只要使用RAM芯片就可以了。

(5)处理器并不直接连接外设,而是通过I/O接口电路与外设连接。

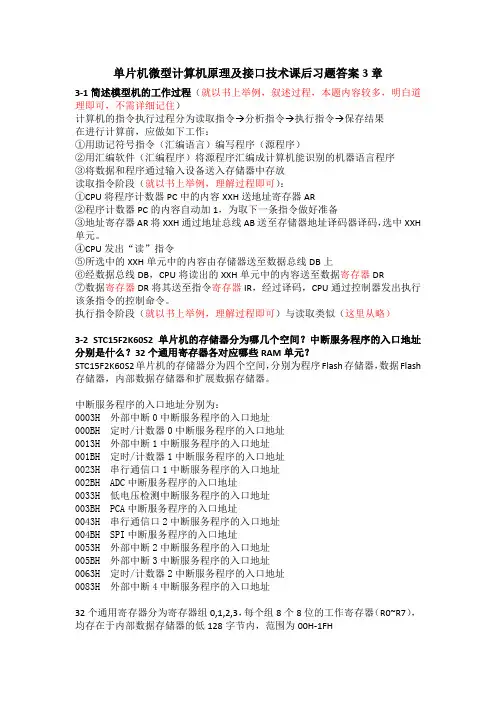

单片机微型计算机原理及接口技术课后习题答案3章3-1简述模型机的工作过程(就以书上举例,叙述过程,本题内容较多,明白道理即可,不需详细记住)计算机的指令执行过程分为读取指令→分析指令→执行指令→保存结果在进行计算前,应做如下工作:①用助记符号指令(汇编语言)编写程序(源程序)②用汇编软件(汇编程序)将源程序汇编成计算机能识别的机器语言程序③将数据和程序通过输入设备送入存储器中存放读取指令阶段(就以书上举例,理解过程即可):①CPU将程序计数器PC中的内容XXH送地址寄存器AR②程序计数器PC的内容自动加1,为取下一条指令做好准备③地址寄存器AR将XXH通过地址总线AB送至存储器地址译码器译码,选中XXH 单元。

④CPU发出“读”指令⑤所选中的XXH单元中的内容由存储器送至数据总线DB上⑥经数据总线DB,CPU将读出的XXH单元中的内容送至数据寄存器DR⑦数据寄存器DR将其送至指令寄存器IR,经过译码,CPU通过控制器发出执行该条指令的控制命令。

执行指令阶段(就以书上举例,理解过程即可)与读取类似(这里从略)3-2 STC15F2K60S2单片机的存储器分为哪几个空间?中断服务程序的入口地址分别是什么?32个通用寄存器各对应哪些RAM单元?STC15F2K60S2单片机的存储器分为四个空间,分别为程序Flash存储器,数据Flash 存储器,内部数据存储器和扩展数据存储器。

中断服务程序的入口地址分别为:0003H 外部中断0中断服务程序的入口地址000BH 定时/计数器0中断服务程序的入口地址0013H 外部中断1中断服务程序的入口地址001BH 定时/计数器1中断服务程序的入口地址0023H 串行通信口1中断服务程序的入口地址002BH ADC中断服务程序的入口地址0033H 低电压检测中断服务程序的入口地址003BH PCA中断服务程序的入口地址0043H 串行通信口2中断服务程序的入口地址004BH SPI中断服务程序的入口地址0053H 外部中断2中断服务程序的入口地址005BH 外部中断3中断服务程序的入口地址0063H 定时/计数器2中断服务程序的入口地址0083H 外部中断4中断服务程序的入口地址32个通用寄存器分为寄存器组0,1,2,3,每个组8个8位的工作寄存器(R0~R7),均存在于内部数据存储器的低128字节内,范围为00H-1FH寄存器组0 R0~R7对应00H-07H寄存器组1 R0~R7对应08H-0FH寄存器组2 R0~R7对应10H-17H寄存器组3 R0~R7对应18H-1FH3-3 位地址29H,61H,7FH,E0H,F1H,各对应哪些单元的哪些位?29H——RAM位寻址区字节地址25H,对应D1位61H——RAM位寻址区字节地址2CH,对应D1位7FH——RAM位寻址区字节地址2FH,对应D7位E0H——高128字节/特殊功能寄存器SFR区,寄存器ACC(字节地址E0H)的D0位;F1H——高128字节/SFR,寄存器B(字节地址F0H)的D1位。

.第1章绪论作业1.将下列二进制数转换成十进制数。

(1)11001010B=202(2)00111101B=61(3)01001101B=77(4)10100100B=1643.将下列十进制数分别转换为二进制数和十六进制数。

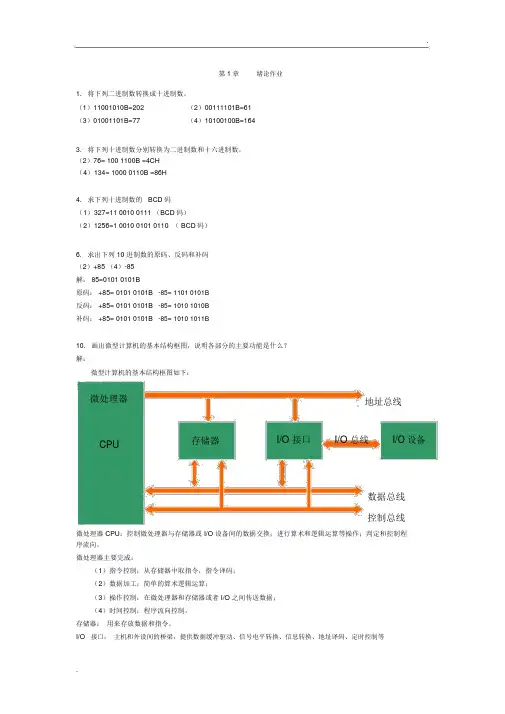

(2)76= 100 1100B =4CH(4)134= 1000 0110B =86H4.求下列十进制数的 BCD码(1)327=11 0010 0111 (BCD码)(2)1256=1 0010 0101 0110 ( BCD码)6.求出下列 10 进制数的原码、反码和补码(2)+85 (4)-85解: 85=0101 0101B原码: +85= 0101 0101B-85= 1101 0101B反码: +85= 0101 0101B-85= 1010 1010B补码: +85= 0101 0101B-85= 1010 1011B10.画出微型计算机的基本结构框图,说明各部分的主要功能是什么?解:微型计算机的基本结构框图如下:微处理器地址总线CPU存储器I/O 接口I/O 总线I/O 设备数据总线控制总线微处理器 CPU:控制微处理器与存储器或 I/O 设备间的数据交换;进行算术和逻辑运算等操作;判定和控制程序流向。

微处理器主要完成:(1)指令控制:从存储器中取指令,指令译码;(2)数据加工:简单的算术逻辑运算;(3)操作控制:在微处理器和存储器或者I/O 之间传送数据;(4)时间控制:程序流向控制。

存储器:用来存放数据和指令。

I/O接口:主机和外设间的桥梁,提供数据缓冲驱动、信号电平转换、信息转换、地址译码、定时控制等各种功能。

I/O 设备:输入原始数据和程序,转换成计算机能识别的信息,送入存储器去等待处理。

输出运算结果。

总线:连接计算机系统中各功能部件的信息通道。

第 2 章 8086CPU 作业2. 8086CPU 内部由哪两部分组成?它们的大致是如何工作的?答:(1)8086CPU 由指令执行部件 EU 和总线接口部件 BIU 两部分组成。

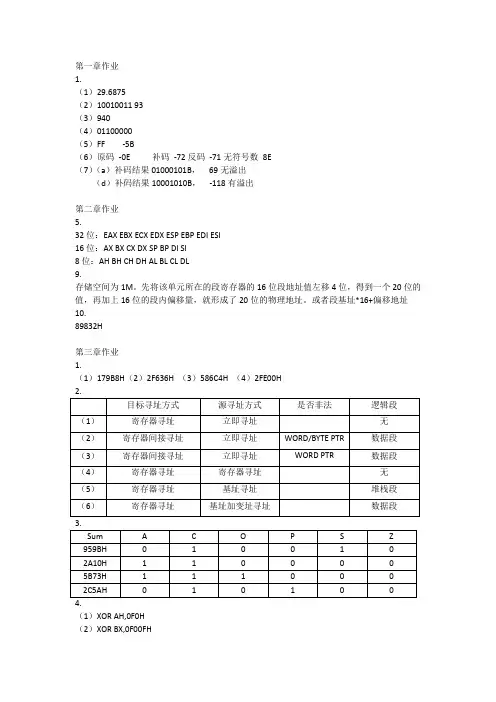

第一章作业1.(1)29.6875(2)10010011 93(3)940(4)01100000(5)FF -5B(6)原码-0E 补码-72反码-71无符号数8E(7)(a)补码结果01000101B,69无溢出(d)补码结果10001010B,-118有溢出第二章作业5.32位:EAX EBX ECX EDX ESP EBP EDI ESI16位:AX BX CX DX SP BP DI SI8位:AH BH CH DH AL BL CL DL9.存储空间为1M。

先将该单元所在的段寄存器的16位段地址值左移4位,得到一个20位的值,再加上16位的段内偏移量,就形成了20位的物理地址。

或者段基址*16+偏移地址10.89832H第三章作业1.(1)179B8H(2)2F636H (3)586C4H (4)2FE00H(1)XOR AH,0F0H(2)XOR BX,0F00FH(3)AND CX,0FFF0H5.(1)方法一:MOV AL, FIRSTXCHG SECOND, ALMOV FIRST, ALMOV AL, FIRST+1XCHG SECOND+1, ALMOV FIRST+1, AL方法二:MOV AX, WORD PTR FIRST XCHG AX, WORD PTR SECOND MOV WORD PTR FIRST, AX (2)PUSH WORD PTR FIRST PUSH WORD PTR SECOND POP WORD PTR FIRSTPOP WORD PTR SECOND堆栈操作示意图如下:6. 6601H。

第一章课后习题1.1 把下列十进制数转换成二进制数、八进制数、十六进制数。

① 16.25 ② 35.75 ③ 123.875 ④ 97/1281.2 把下列二进制数转换成十进制数。

① 10101.01 ② 11001.0011 ③ 111.01 ④ 1010.11.3 把下列八进制数转换成十进制数和二进制数。

① 756.07 ② 63.73 ③ 35.6 ④ 323.451.4 把下列十六进制数转换成十进制数。

① A7.8 ② 9AD.BD ③ B7C.8D ④ 1EC1.5 求下列带符号十进制数的8位补码。

① +127 ② -1 ③ -0 ④ -1281.6 求下列带符号十进制数的16位补码。

① +355 ② -11.7 计算机分那几类?各有什么特点?1.8 简述微处理器、微计算机及微计算机系统三个术语的内涵。

1.9 80X86微处理器有几代?各代的名称是什么?1.10 你知道现在的微型机可以配备哪些外部设备?1.11 微型机的运算速度与CPU的工作频率有关吗?1.12 字长与计算机的什么性能有关?习题一参考答案1.1 ① 16.25D=10000.01B=20.2Q=10.4H② 35.75D=.11B=43.6Q=23.CH③ 123.875D=.111B=173.7Q=7B.EH④ 97/128D=64/123+32/128+1/128=0.B=0.604Q=0.C2H1.2 ① 10101.01B=21.25D ② 11001.0011B=25.1875D③ 111.01B=7.25D ④ 1010.1B=10.5D1.3 ① 756.07Q=.B=494.109D ② 63.73Q=.B=51.922D③ 35.6Q=11101.110B=29.75D ④ 323.45Q=.B=211.578D1.4 ① A7.8H=167.5D ② 9AD.BDH=2477.738D③ B7C.8D=2940.551D ④ 1ECH=492D1.5 ① [+127]补= ② [-1]补=③ [-0]补= ④[-128]补=1.6 ① [+355]补= 00011 ② [-1]补= 1111 1111 1111 11111.7 答:传统上分为三类:大型主机、小型机、微型机。

第 3 章【单片机的指令系统】思考与练习题解析【3—1】什么是指令及指令系统?【答】控制单片机进行某种操作的命令称为“指令” 。

单片机就是根据指令来指挥和控制单片机各部分协调工作。

指令由二进制代码表示,指令通常包括操作码和操作数两部分:操作码规定操作的类型,操作数给出参加操作的数或存放数的地址。

所有指令的集合称为“指令系统”。

80C51单片机的指令系统专用于80C51系列单片机,是一个具有255种操作码(00H〜FFH,除A5H外)的集合。

【3—2】80C51 单片机的指令系统具有哪些特点?【答】80C51单片机的指令系统容易理解和阅读。

只要熟记代表33种功能的42种助记即可。

有的功能如数据传送,可以有几种助记符,如M0V 、M0Vc 、M0VX 。

而指令功能助记符与操作数各种寻址方式的结合,共构造出111 种指令,而同一种指令所对应的操作码可以多至8 种(如指令中Rn对应寄存器R0〜R7)。

80C51 单片机的指令系统具有较强的控制操作类指令,容易实现“面向控制”的功能;具有位操作类指令,有较强的布尔变量处理能力。

【3—3】简述80C51 指令的分类和格式。

【答】80C51 的指令系统共有111条指令,按其功能可分为5大类:数据传送类指令(28条)、算术运算类指令(24条)、逻辑运算类指令(25条)、控制转移类指令(17条)和布尔操作(位)类指令(17条)。

指令的表示方法称之为“指令格式” ,其内容包括指令的长度和指令内部信息的安排等。

在80C51 系列的指令系统中,有单字节、双字节和三字节等不同长度的指令。

•单字节指令:指令只有一个字节,操作码和操作数同在一个字节中。

•双字节指令:包括两个字节。

其中一个字节为操作码,另一个字节是操作数。

•三字节指令:操作码占一个字节,操作数占两个字节。

其中操作数既可能是数据,也可能是地址。

【3—4】简述80C51 的指令寻址方式,并举例说明。

【答】执行任何一条指令都需要使用操作数,寻址方式就是在指令中给出的寻找操作数或操作数所在地址的方法。

第3章8086CPU指令系统1.写出完成下列要求的变量定义语句:(1)在变量var1中保存6个字变量:4512H,4512,-1,100/3,10H,65530;(2)在变量var2中保存字符串:’BYTE’, ’word’, ’WORD’;(3)在缓冲区buf1中留出100个字节的存储空间;(4)在缓冲区buf2中,保存5个字节的55H,再保存10个字节的240,并将这一过程重复7次;(5)在变量var3中保存缓冲区buf1的长度;(6)在变量pointer中保存变量var1和缓冲区buf1的偏移地址。

解:var1 DW 4512H,4512,-1,100/3,10H,65530var2 DB ’BYTE’,’word’,’WORD’buf1 DB 100 DUP(?)buf2 DB 7 DUP(5 DUP(55H),10 DUP(240))var3 DB LENGTH buf1pointer DW var1,buf1 (或者pointer DW OFFSET var1,OFFSET buf1)2.设变量var1的逻辑地址为0100:0000,画出下列语句定义的变量的存储分配图:var1 DB 12,-12,20/6,4 DUP(0,55H)var2 DB ‘Assemble’var3 DW ‘AB’, ‘cd’, ‘E’var4 DW var2var5 DD var2解:3.指令正误判断,对正确指令写出源和目的操作数的寻址方式,对错误指令指出原因(设VAR1, VAR2为字变量, L1为标号):(1)MOV SI,100 (2)MOV BX,VAR1[SI](3)MOV AX, [BX] (4)MOV AL, [DX](5)MOV BP, AL (6)MOV VAR1, VAR2(7)MOV CS, AX (8)MOV DS, 0100H(9)MOV [BX][SI], 1 (10)MOV AX, VAR1+VAR2(11)ADD AX, LENGTH VAR1 (12)OR BL, TYPE VAR2(13)SUB [DI], 78H (14)MOVS VAR1, VAR2(15)PUSH 100H (16)POP CS(17)XCHG AX, ES (18)MOV DS, CS(19)JMP L1+5 (20)DIV AX, 10(21)SHL BL, 2 (22)MOV AL, 15+23(23)MUL CX (24)XCHG CL, [SI](25)ADC CS:[0100], AH (26)SBB VAR1-5,154解:(1)MOV SI,100 正确。

第3章8086/8088指令系统与寻址方式习题3.3 8086系统中,设DS=1000H,ES=2000H,SS=1200H,BX=0300H,SI=0200H,BP=0100H,VAR的偏移量为0600H,请指出下列指令的目标操作数的寻址方式,若目标操作数为存储器操作数,计算它们的物理地址。

(1)MOV BX,12 ;目标操作数为寄存器寻址(2)MOV [BX],12 ;目标操作数为寄存器间址PA=10300H(3)MOV ES:[SI],AX ;目标操作数为寄存器间址PA=20200H(4)MOV VAR,8 ;目标操作数为存储器直接寻址PA=10600H(5)MOV [BX][SI],AX ;目标操作数为基址加变址寻址PA=10500H(6)MOV 6[BP][SI],AL ;目标操作数为相对的基址加变址寻址PA=12306H (7)MOV [1000H],DX ;目标操作数为存储器直接寻址PA=11000H(8)MOV 6[BX],CX ;目标操作数为寄存器相对寻址PA=10306H(9)MOV VAR+5,AX ;目标操作数为存储器直接寻址PA=10605H3.4 下面这些指令中哪些是正确的那些是错误的如果是错误的,请说明原因。

(1)XCHG CS,AX ;错,CS不能参与交换(2)MOV [BX],[1000] ;错,存储器之不能交换(3)XCHG BX,IP ;错,IP不能参与交换(4)PUSH CS(5)POP CS ;错,不能将数据弹到CS中(6)IN BX,DX ;输入/输出只能通过AL/AX(7)MOV BYTE[BX],1000 ;1000大于255,不能装入字节单元(8)MOV CS,[1000] ;CS不能作为目标寄存器(9)MOV BX,OFFSET VAR[SI] ;OFFSET只能取变量的偏移地址(10)MOV AX,[SI][DI] ;SI、DI不能成为基址加变址(11)MOV COUNT[BX][SI],ES:AX ;AX是寄存器,不能加段前缀3.7 设当前SS=2010H,SP=FE00H,BX=3457H,计算当前栈顶的地址为多少当执行PUSH BX 指令后,栈顶地址和栈顶2个字节的内容分别是什么当前栈顶的地址=2FF00H当执行PUSH BX 指令后,栈顶地址=2FEFEH(2FEFEH)=57H(2FEFFH)=34H3.8 设DX=78C5H,CL=5,CF=1,确定下列各条指令执行后,DX和CF中的值。

微机原理与接口技术(第二版)课后习题答案第1章作业答案1.1 微处理器、微型计算机和微型计算机系统三者之间有什么不同?解:把CPU(运算器和控制器)用大规模集成电路技术做在一个芯片上,即为微处理器。

微处理器加上一定数量的存储器和外部设备(或外部设备的接口)构成了微型计算机。

微型计算机与管理、维护计算机硬件以及支持应用的软件相结合就形成了微型计算机系统。

1.2 CPU在内部结构上由哪几部分组成?CPU应该具备哪些主要功能? 解:CPU主要由起运算器作用的算术逻辑单元、起控制器作用的指令寄存器、指令译码器、可编程逻辑阵列和标志寄存器等一些寄存器组成。

其主要功能是进行算术和逻辑运算以及控制计算机按照程序的规定自动运行。

1.3 微型计算机采用总线结构有什么优点?解:采用总线结构,扩大了数据传送的灵活性、减少了连线。

而且总线可以标准化,易于兼容和工业化生产。

1.4 数据总线和地址总线在结构上有什么不同之处?如果一个系统的数据和地址合用一套总线或者合用部分总线,那么要靠什么来区分地址和数据?解:数据总线是双向的(数据既可以读也可以写),而地址总线是单向的。

8086CPU为了减少芯片的引脚数量,采用数据与地址线复用,既作数据总线也作为地址总线。

它们主要靠信号的时序来区分。

通常在读写数据时,总是先输出地址(指定要读或写数据的单元),过一段时间再读或写数据。

1.8在给定的模型中,写出用累加器的办法实现15×15的程序。

解: LD A, 0LD H, 15LOOP:ADD A, 15DEC HJP NZ, LOOPHALT第 2 章作业答案2.1 IA-32结构微处理器直至Pentillm4,有哪几种?解:80386、30486、Pentium、Pentium Pro、Peruium II 、PentiumIII、Pentium4。

2.6 IA-32结构微处理器有哪几种操作模式?解:IA一32结构支持3种操作模式:保护模式、实地址模式和系统管理模式。