集成电路制造工艺课件【芯片制造】

- 格式:ppt

- 大小:11.49 MB

- 文档页数:99

从电路设计到芯片完成离不开集成电路的制备工艺, 本章主要介绍硅衬底上的CMOS 集成电路制造的工艺过程。

有些CMOS 集成电路涉及到高压MOS 器件(例如平板显示驱动芯片、智能功率CMOS 集成电路等), 因此高低压电路的兼容性就显得十分重要, 在本章最后将重点说明高低压兼容的CMOS 工艺流程。

1.1 基本的制备工艺过程CMOS 集成电路的制备工艺是一个非常复杂而又精密的过程, 它由若干单项制备工艺组合而成。

下面将分别简要介绍这些单项制备工艺。

1.1.1 衬底材料的制备任何集成电路的制造都离不开衬底材料——单晶硅。

制备单晶硅有两种方法: 悬浮区熔法和直拉法, 这两种方法制成的单晶硅具有不同的性质和不同的集成电路用途。

1 悬浮区熔法悬浮区熔法是在20世纪50年代提出并很快被应用到晶体制备技术中。

在悬浮区熔法中, 使圆柱形硅棒固定于垂直方向, 用高频感应线圈在氩气气氛中加热, 使棒的底部和在其下部靠近的同轴固定的单晶籽晶间形成熔滴, 这两个棒朝相反方向旋转。

然后将在多晶棒与籽晶间只靠表面张力形成的熔区沿棒长逐步向上移动, 将其转换成单晶。

悬浮区熔法制备的单晶硅氧含量和杂质含量很低, 经过多次区熔提炼, 可得到低氧高阻的单晶硅。

如果把这种单晶硅放入核反应堆, 由中子嬗变掺杂法对这种单晶硅进行掺杂, 那么杂质将分布得非常均匀。

这种方法制备的单晶硅的电阻率非常高, 特别适合制作电力电子器件。

目前悬浮区熔法制备的单晶硅仅占有很小市场份额。

2 直拉法随着超大规模集成电路的不断发展, 不但要求单晶硅的尺寸不断增加, 而且要求所有的杂质浓度能得到精密控制, 而悬浮区熔法无法满足这些要求, 因此直拉法制备的单晶越来越多地被人们所采用, 目前市场上的单晶硅绝大部分采用直拉法制备得到的。

拉晶过程:首先将预处理好的多晶硅装入炉内石英坩埚中, 抽真空或通入惰性气体后进行熔硅处理。

熔硅阶段坩埚位置的调节很重要。

开始阶段, 坩埚位置很高, 待下部多晶硅熔化后, 坩埚逐渐下降至正常拉晶位置。

集成电路制造工艺第1章绪论1.1 课题背景在过去的的几十年里,一个以计算机、互联网、无线通信和全球定位系统为组成部分的信息社会逐渐形成。

这个信息社会的核心部分是由众多内建于系统中的细小集成电路(IC)芯片支持和构成的。

集成电路广泛应用于生活中的各个领域—诸如消费类产品、家庭用品、汽车、信息技术、电信、媒体、军事和空间应用。

结合纳米技术,持续不断的研究和开发即将使得集成电路更小和更强有力。

在可见的未来,计算机的尺寸将缩小到指甲盖大小,达到集成电路在尺寸、速度、价格及功耗方面实际可能的极限。

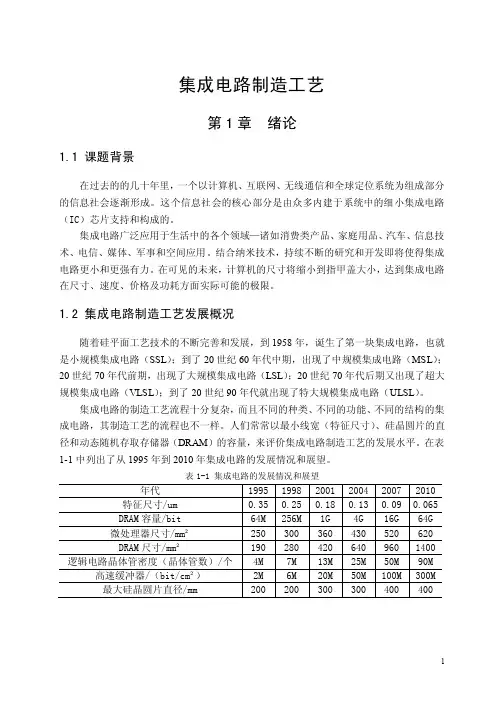

1.2 集成电路制造工艺发展概况随着硅平面工艺技术的不断完善和发展,到1958年,诞生了第一块集成电路,也就是小规模集成电路(SSL);到了20世纪60年代中期,出现了中规模集成电路(MSL);20世纪70年代前期,出现了大规模集成电路(LSL);20世纪70年代后期又出现了超大规模集成电路(VLSL);到了20世纪90年代就出现了特大规模集成电路(ULSL)。

集成电路的制造工艺流程十分复杂,而且不同的种类、不同的功能、不同的结构的集成电路,其制造工艺的流程也不一样。

人们常常以最小线宽(特征尺寸)、硅晶圆片的直径和动态随机存取存储器(DRAM)的容量,来评价集成电路制造工艺的发展水平。

在表1-1中列出了从1995年到2010年集成电路的发展情况和展望。

表1-1 集成电路的发展情况和展望年代1995 1998 2001 2004 2007 2010 特征尺寸/um 0.35 0.25 0.18 0.13 0.09 0.065DRAM容量/bit 64M 256M 1G 4G 16G 64G微处理器尺寸/mm²250 300 360 430 520 620DRAM尺寸/mm²190 280 420 640 960 1400 逻辑电路晶体管密度(晶体管数)/个4M 7M 13M 25M 50M 90M 高速缓冲器/(bit/cm²)2M 6M 20M 50M 100M 300M最大硅晶圆片直径/mm 200 200 300 300 400 400第2章半导体集成电路制造工艺流程2.1 概括本章以大量精美的图片、图表及具体详实的数据详细描述了集成电路制造的全过程。