实验三 触发器特性测试

- 格式:doc

- 大小:556.50 KB

- 文档页数:11

触发器实验报告引言:触发器是数字电路中常见的基本组件之一,它能够存储和转换电信号,广泛应用于各种电子设备和系统中。

本实验旨在通过实际操作,深入理解触发器的工作原理和应用。

实验原理:触发器是一种双稳态电路,能够固定保存输入信号的状态。

常见的触发器包括RS触发器、D触发器、JK触发器等。

本实验将以D触发器为例进行演示。

实验步骤:1. 准备实验器材:D触发器芯片、电源、示波器以及适配器等。

2. 连接电路:将D触发器芯片插入适配器,并按照实验电路图连接相关引脚。

3. 提供输入信号:通过开关或信号源向D触发器提供输入信号。

4. 观察输出信号:使用示波器监测D触发器的输出信号,并记录相关数据。

5. 测量实验数据:改变输入信号的频率和幅值,测量触发器的输出变化,并记录数据。

6. 分析实验结果:根据观察到的数据,分析D触发器的工作原理和特性。

实验结果与分析:通过实验观察和实际数据记录,我们可以得出以下结论:1. D触发器具有边沿触发和电平触发两种模式。

在边沿触发模式下,触发器仅在输入信号上升沿(或下降沿)时才进行状态转换;而在电平触发模式下,输入信号处于高电平(或低电平)时触发器状态保持不变。

2. D触发器的输出状态受到输入信号和时钟信号的控制。

输入信号为逻辑高电平时,若时钟信号为上升沿触发,则输出信号将与上一时钟周期的输入信号一致;若时钟信号为下降沿触发,则输出信号将与上一时钟周期的输入信号相反。

3. 改变输入信号的频率和幅值,我们发现触发器的输出信号频率和幅值也发生了相应的变化。

当输入信号频率较低时,触发器能够稳定存储和输出输入信号;而当输入信号频率较高时,触发器可能无法及时反应输入信号的状态变化,导致输出信号不准确。

实验应用:触发器作为数字电路中的重要组件,在现代电子技术中有着广泛的应用:1. 存储器芯片中广泛使用的触发器技术,使得计算机能够对数据进行有效地存储和读取。

2. 触发器在时序电路中的应用,能够实现时钟同步、状态变化检测等功能。

河南工学院实验报告实验项目触发器逻辑功能测试

实验日期

班级姓名

指导教师综合成绩

一、预习内容

二、实验数据(现象)记录及结果处理

三、实验结果分析与讨论

教师评阅意见

(1)实验预习 (30分)成绩:

□预习认真、熟练掌握方法与步骤(30~28) □有预习、基本掌握方法与步骤(27~22)

□有预习、但未能掌握方法与步骤(21~18) □没有预习,不能完成实验(17~0)

(2)操作过程 (40分)成绩:

□遵规守纪、操作熟练、团结协作 (40~37) □遵规守纪、操作正确、有协作 (36~29) □遵规守纪、操作基本正确、无协作 (28~24) □不能遵规守纪、操作不正确、无协作(17~0) (3)结果分析 (30分)成绩:

□结果详实、结论清晰、讨论合理(30~28) □结果正确、讨论适当(27~22)

□结果正确、没有分析讨论(21~18) □结果不正确、没有分析讨论(17~0)

其它意见:

教师签名:年月日。

数电触发器实验报告数电触发器实验报告引言:在数电领域中,触发器是一种重要的电子元件,用于存储和处理数字信号。

触发器可以用于时钟信号的同步、存储数据以及实现各种逻辑功能。

本实验旨在通过实际操作,深入理解触发器的工作原理和应用。

实验目的:1. 了解触发器的基本概念和分类;2. 学会使用触发器构建简单的逻辑电路;3. 掌握触发器的触发条件和时序特性。

实验器材:1. 数字电路实验箱;2. 74LS74触发器芯片;3. 电源线、连接线等。

实验步骤:1. 连接电路:将74LS74芯片插入实验箱中,并根据实验电路图连接芯片的引脚和外部元件。

2. 上电测试:接通电源,检查电路连接是否正确,并观察芯片上的LED指示灯是否亮起。

3. 输入信号测试:通过拨动开关或按下按钮,改变输入信号的状态,观察触发器输出的变化。

4. 触发条件测试:根据触发器的特性表,改变输入信号的时序,观察触发器的触发条件和输出结果。

5. 扩展实验:尝试使用多个触发器芯片构建更复杂的逻辑电路,如计数器、时序电路等。

实验结果与分析:在实验过程中,我们观察到了以下现象和结果:1. 当输入信号满足触发器的触发条件时,触发器的输出状态会发生变化。

例如,在D触发器中,当时钟信号上升沿到来时,若D输入为高电平,则Q输出会跟随D输入的状态变化;若D输入为低电平,则Q输出保持不变。

2. 当输入信号不满足触发器的触发条件时,触发器的输出状态保持不变。

例如,在JK触发器中,当时钟信号上升沿到来时,若J和K输入同时为高电平,则Q输出会取反;若J和K输入同时为低电平,则Q输出保持不变。

3. 不同类型的触发器具有不同的触发条件和时序特性,需要根据实际应用的需求选择合适的触发器。

4. 在构建复杂逻辑电路时,需要注意触发器之间的时序关系和输入信号的稳定性,以确保电路的正确运行。

实验总结:通过本次实验,我们深入了解了数电触发器的工作原理和应用。

触发器作为数字电路中的重要组成部分,广泛应用于计算机、通信、控制等领域。

触发器实验报告一、实验目的本次触发器实验的主要目的是深入了解触发器的工作原理、功能特性以及在数字电路中的应用。

通过实际操作和观察,掌握触发器的基本概念,熟悉其逻辑功能和时序特性,为后续更复杂的数字电路设计和分析打下坚实的基础。

二、实验设备与器材1、数字电路实验箱2、示波器3、逻辑分析仪4、若干集成电路芯片,包括 D 触发器、JK 触发器等三、实验原理(一)D 触发器D 触发器是一种在时钟脉冲上升沿或下降沿触发的触发器。

当 D 输入端的数据在时钟脉冲作用下被传输到输出端 Q。

其逻辑表达式为:Q(n+1) = D 。

(二)JK 触发器JK 触发器具有置 0、置 1、保持和翻转四种功能。

当 J = 1,K = 0 时,触发器置 1;当 J = 0,K = 1 时,触发器置 0;当 J = K = 0 时,触发器保持原态;当 J = K = 1 时,触发器翻转。

其逻辑表达式为:Q(n+1) = JQ' + K'Q 。

四、实验内容与步骤(一)D 触发器功能测试1、按照实验电路图在数字电路实验箱上连接好 D 触发器芯片。

2、将 D 输入端分别接高电平和低电平,通过示波器观察时钟脉冲和输出端 Q 的波形,记录实验结果。

(二)JK 触发器功能测试1、依照实验电路图搭建 JK 触发器的实验电路。

2、分别设置 J、K 输入端的不同组合,观察并记录输出端 Q 的状态变化。

(三)触发器的级联1、将多个 D 触发器或 JK 触发器级联,形成移位寄存器。

2、输入串行数据,观察移位寄存器的输出结果。

五、实验数据与结果分析(一)D 触发器实验结果当 D 输入端接高电平时,在时钟脉冲上升沿,输出端 Q 变为高电平;当 D 输入端接低电平时,在时钟脉冲上升沿,输出端 Q 变为低电平。

这与 D 触发器的逻辑功能相符,验证了其正确性。

(二)JK 触发器实验结果在不同的 J、K 输入组合下,JK 触发器的输出端 Q 呈现出置 1、置0、保持和翻转的状态,与理论预期完全一致。

三态输出触发器和锁存器实验报告有数据1. 理解三态输出触发器和锁存器的工作原理;2. 掌握三态输出触发器和锁存器的实验方法;3. 熟悉使用示波器进行实验测量和数据分析。

实验器材:- 简易逻辑实验箱- 三态输出触发器芯片(例如74LS373)- 锁存器芯片(例如74LS175)- 计时器芯片(例如555)- 示波器- 电源和电线等其他辅助器材实验原理:1. 三态输出触发器(Tri-state Output Flip-Flop):三态输出触发器是一种特殊的双稳态触发器,其输出可以处于三种状态之一: 高电平、低电平和高阻态(High-Z)。

利用一个使能端(Enable)来控制输出状态,当使能端为低电平时,输出处于高阻态,此时输出不受触发器的状态控制;当使能端为高电平时,输出由触发器的状态决定。

74LS373是一种广泛使用的三态输出触发器芯片,其引脚功能如下(以16位为例):- D0 ~ D15: 数据输入端,用于输入要存储的数据;- OE:输出使能端,用于控制输出状态;- LE:锁存使能端,用于控制存储操作;- Q0 ~ Q15: 输出端,输出存储的数据。

实验中,我们将通过控制OE和LE端的电平来实现三态输出触发器的控制和数据存储。

2. 锁存器(Latch):锁存器是一种具有存储功能的触发器,可以通过控制使能端来实现数据的锁存和释放。

常见的锁存器有SR锁存器和D锁存器等。

74LS175是一种广泛使用的锁存器芯片,其引脚功能如下(以四位为例):- D0 ~ D3: 数据输入端,用于输入要存储的数据;- EN: 使能端,用于控制存储操作;- Q0 ~ Q3: 输出端,输出存储的数据。

实验中,我们将通过控制EN端的电平来实现锁存器的控制和数据存储。

实验步骤:实验一: 三态输出触发器实验1. 连接电路: 将74LS373芯片插入实验箱中,并按照引脚功能连接电路,包括数据输入端、输出端、输出使能端和锁存使能端等。

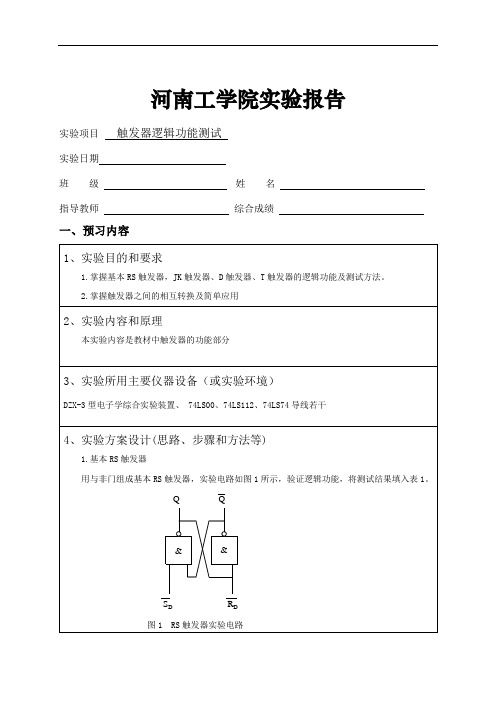

电子通信与软件工程 系2013-2014学年第2学期《数字电路与逻辑设计实验》实验报告--------------------------------------------------------------------------------------------------------------------- 班级: 姓名: 学号: 成绩:同组成员: 姓名: 学号:---------------------------------------------------------------------------------------------------------------------一、 实验名称:触发器工作原理与功能测试二、实验目的:1、熟悉并掌握R —S 、D 、J —K 触发器的构成,工作原理和功能测试方法.2、学会正确使用触发器集成芯片.三、实验内容:1.基本R —SFF 功能测试:两个TTL 与非门首尾相接构成的基本R —SFF 的电路如图7.1所示.(1)试按下面的顺序在d S ,d R 端加信号: d S =0 d R =1 d S =1 d R =1d S =1 d R =0 图7.1 基本 R —S FF 电路d S =1 d R =1观来并记录FF 的Q 、Q 端的状态,将结果填入下表7。

1中,并说明在上述各种输入状态下FF 执行的是什么功能?(2)d S 端接低电平.d R 端加脉冲。

(3)d S 端接高电子.d R 端加脉冲。

(4)连接Rd 、Sd ,并加脉冲记录并观察(2)、(3)、(4)三种情况下,Q ,Q 端的状态.从中你能否总结出基本R 一SFF 的Q 或Q 端的状态改变和输人端d S ,d R 的关系。

(5)当d S 、d R 都接低电平时,观察Q 、Q 端的状态。

当d S 、d R 同时由低电平跳为高电平时,注意观察Q 、Q 端的状态,重复 3~5次看 Q、Q 端的状态是否相同,以正确理解“不定”状态的含义。

数电实验触发器实验报告引言触发器是数字电路中常用的元件,它可以储存和控制输入信号的状态。

在数电实验中,我们进行了触发器的实验,旨在探究触发器的工作原理和应用。

实验目的本实验的目的是: 1. 了解触发器的基本概念和分类; 2. 掌握触发器的工作原理;3. 学会使用触发器设计和实现基本的时序电路。

实验材料和设备1.数字电路实验箱;2.7400四路二输入与非门芯片;3.7402四路二输入与非门芯片;4.7408四路二输入与门芯片;5.7432四路二输入或门芯片;6.74165八位平行装载输入八位并行输出移位存储器芯片;7.电路连接导线;8.示波器。

实验步骤实验一:SR触发器的应用1.将SR触发器芯片连接到实验箱中,根据连接图进行连接;2.调试硬件连接,确保电路连接无误;3.给予输入信号,观察触发器的输出变化;4.记录观察结果。

实验二:JK触发器的应用1.将JK触发器芯片连接到实验箱中,根据连接图进行连接;2.调试硬件连接,确保电路连接无误;3.给予输入信号,观察触发器的输出变化;4.记录观察结果。

实验三:D触发器的应用1.将D触发器芯片连接到实验箱中,根据连接图进行连接;2.调试硬件连接,确保电路连接无误;3.给予输入信号,观察触发器的输出变化;4.记录观察结果。

实验四:T触发器的应用1.将T触发器芯片连接到实验箱中,根据连接图进行连接;2.调试硬件连接,确保电路连接无误;3.给予输入信号,观察触发器的输出变化;4.记录观察结果。

实验五:时序电路的设计1.使用74LS165芯片进行时序电路的设计;2.根据设计要求,连接芯片及其他元件;3.调试硬件连接,确保电路连接无误;4.给予输入信号,观察时序电路的输出变化;5.记录观察结果。

实验结果与分析实验一:SR触发器的应用观察实验一中的SR触发器,当S=0,R=0时,输出保持不变。

当S=1,R=0时,输出为1。

当S=0,R=1时,输出为0。

当S=1,R=1时,输出无法确定,可能产生非正常状态。

v .. . .. . . . 资 料. .

数字逻辑实验指导书 葛长赟编写 大连东软信息学院 电子工程系 2016年 8月 . Word 资料 引 言 《数字逻辑》是软件工程专业的必修课,为后续课程的实施,为进一步学习各专业后续课程打下基础,是一门理论与实践相结合的课程。 通过这门课程的学习,使学生掌握数字电路与系统的基本工作原理和分析设计方法;理解标准的集成电路器件使用方法为后续学习奠定基础。 本门课程理论内容包括:数制与码制、逻辑代数基础、组合逻辑电路的分析和设计、各种触发器及时序逻辑电路的分析和设计等,除数制与码制外,每部分内容都配备有相应的实验室实验,帮助学生理解和掌握相关知识内容。 本实验指导书旨在对《数字逻辑》课程的实验进行规范,内容包括:实验目的和要求、设备或环境、实验原理(项目分析和设计)、实验内容(项目实施)等。学生可遵照本实验指导书内容完成相应实验并提交实验报告。 .

Word 资料 设备与工具 这章主要介绍本实验指导书中会用到的硬件设备。 信号发生器 信号发生器是一台具有高度稳定性、多功能等特点的函数信号发生器。能直接产生正弦波、三角波、方波、斜波、脉冲波,波形对称可调并具有反向输出,直流电平可连续调节。TTL可与主信号做同步输出。还具有VCF输入控制功能。频率计可做内部频率显示,也可外测1Hz~10.0MHz的信号频率,电压用LED显示。

万用表 万用表是一种多功能、多量程的便携式电子电工仪表,一般的万用表可以测量直流电流、直流电压、交流电压、电阻等。有些万用表还可测量电容、电感、功率、晶体管共射极直流放大系数等。

数字电路实验箱 数字电路实验箱可以为学生提供内容丰富的实验平台,结构设计灵活,可在此平台上搭建电路,完成数字电路课程要求的基本实验。 . Word 资料 实验三:触发器特性测试 1. 能力培养目标 理解RS触发器、D触发器、JK触发器的工作原理 能正确使用RS触发器、D触发器、JK触发器

2. 项目任务要求 (1) 利用与非门构成RS触发器 (2) 测试D触发器的逻辑功能 (3) 测试JK触发器的逻辑功能

3. 项目分析 (1)RS触发器 把两个与非门的输入、输出端交叉连接,即可构成基本RS触发器。RS触发器的__Q 和Q应该呈互补关系,但在__R= 0、__S= 0 时Q和__Q都为1,

所以此时为非法状态。 . Word 资料 表2-5-1 RS触发器真值表 输 入 输 出 __R __

S Q __Q

0 0 1 1

0 1 0 1 1 0 1 0 1 1 Q __Q

74LS00是最常见的二输入四与非门芯片之一,因此可选用74LS00芯

片。 (2)D触发器 D触发器的应用很广,可用作数字信号的寄存、移位寄存、分频和波形发生等。下表中的“X”表示该引脚的电平无论高低,对输出结果不发生任何作用;“↑”表示该引脚要接到单次脉冲开关,且应为上升沿,按下单次脉冲按钮时输出结果会发生变化。 表2-5-2 D触发器真值表 输 入 输 出

PR CLR CK D Q __Q

0 1 X X 1 0 1 0 X X 0 1 0 0 X X 1 1 1 1 ↑ 1 1 0 1 1 ↑ 0 0 1

1 1 0 X Q __Q

双D触发器74LS74芯片的引脚结构图如下所示,其中引脚14(VCC)接5V电源,引脚7(GND)接地。CLR表示复位信号(清零),D表示触发信号,CK表示时钟信号,PR表示预置,Q表示同相位输出,__Q表示反

相位输出。 .

Word 资料 141312111098

1234567

双 D 触发器 74LS74

Vcc2CLR2D2CK2PR2Q2QGND1CLR1D1CK1PR1Q1Q 图2-5-1 74LS74引脚结构图

(3)JK触发器

JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。下面分四种情况来分析主从型JK触发器的逻辑功能。 JK触发器在J=1,K=1的情况下,来一个时钟脉冲就翻转一次,即具有计数功能。 J=0,K=0时,触发器的状态保持不变。 J=1,K=0时,触发器的状态翻转成1态。 J=0,K=1时,触发器的状态翻转成0态。 表2-5-3 JK触发器真值表 输 入 输 出

CLR CK J K Q __Q

0 X X X 0 1

1 ↓ 0 0 Q __Q

1 ↓ 1 0 1 0 1 ↓ 0 1 0 1 1 ↓ 1 1 反 转 . Word 资料 1 1 X X Q __Q

【注】上表中的 “↓”表示该引脚要接到单次脉冲开关,且应为下降沿,按下单次脉冲按钮时输出结果会发生变化。

141312111098

1234567

双 JK 触发器 74LS73

1J1Q1QGND2K2Q2Q2J1CK1CLR1KVcc2CK2CLR 图2-5-2 74LS73引脚结构图

(4)实验设备及材料

数电实验箱(含连接线) 1台 面包板(含连接线) 1台 二输入四与非门74LS00 1片 双D触发器74LS74 1片 双JK触发器74LS73 1片 示波器 1台

4. 项目设计 (1)利用与非门构成RS触发器 利用74LS00的两个与非门搭建RS触发器,输入端__R、__S接实验箱上

的逻辑开关输出,输出端__Q、Q接逻辑电平指示灯,电路接线图如下: . Word 资料 &A

BY

&A

BY

LED0LED1K2

K1R

_

S_Q_

Q 图2-5-3 RS触发器逻辑电路接线图 (2)测试D触发器的逻辑功能

74LS74芯片包含两个D触发器,测试时可任选其中一组触发器。将引脚CLR(复位端)、PR(置位端)、D接实验箱上的逻辑开关输出,引脚Q、__Q接逻辑状态显示灯,测试电路接线图如下:

QQLED2LED1

DCKCLRK2K1PRAKK3_

图2-5-4 D触发器逻辑电路接线图 如果将输入引脚D接到连续脉冲信号时,可通过示波器观察D触发器

的输入输出的波形之间的关系,这时需要将引脚D接到固定脉冲信号源1KHz,引脚CK接10KHz,那么输出引脚Q也呈现连续波形。 (3)测试JK触发器的逻辑功能 74LS73芯片包含两个JK触发器,测试时可任选其中一组触发器。将引脚J、K、CLR接到逻辑开关输出,引脚Q、__Q接逻辑电平指示灯,测试电

路接线图如下: .

Word 资料 QQLED2LED1

CLRCKJK2K1KAKK3_

图2-5-5 JK触发器逻辑电路接线图 如果将输入接到连续脉冲信号时,可通过示波器观察D触发器的输入

输出的波形之间的关系,这时需要将引脚CK接到固定脉冲信号源1KHz,那么输出引脚Q也呈现连续波形。

5. 项目实施 (1)利用与非门构成RS触发器 按设计的电路接线图连线,按下表中的顺序一步步进行测试,并填写表格。 表2-5-4 RS触发器测试结果表

步骤 输 入 输 出 __R __

S Q __Q

① 0 1

② 1 1

③ 1 0

④ 1 1

⑤ 0 0

【填空】 时序电路的值与 有关。 根据触发器的定义,__Q和Q应互补,因此 时为非法状态。

(2)测试D触发器的逻辑功能

按设计的电路接线图进行连接,将CLR(复位)、PR(置位)引脚接实验板上逻辑电平输出开关,引脚CK接单次脉冲开关,引脚Q、__Q接逻辑

电平指示灯,按下表中的步骤依次改变CLR、PR的电平,观察现象并记录Q、__Q的值,填写表格。

表2-5-5 D触发器测试结果表

步骤

输 入 输 出

CLR PR D CK Q __Q