1、数字逻辑概论

- 格式:ppt

- 大小:501.00 KB

- 文档页数:38

第1章 数字逻辑概论1.1 复习笔记一、模拟信号与数字信号 1.模拟信号和数字信号 (1)模拟信号在时间上连续变化,幅值上也连续取值的物理量称为模拟量,表示模拟量的信号称为模拟信号,处理模拟信号的电子电路称为模拟电路。

(2)数字信号 与模拟量相对应,在一系列离散的时刻取值,取值的大小和每次的增减都是量化单位的整数倍,即时间离散、数值也离散的信号。

表示数字量的信号称为数字信号,工作于数字信号下的电子电路称为数字电路。

(3)模拟量的数字表示①对模拟信号取样,通过取样电路后变成时间离散、幅值连续的取样信号; ②对取样信号进行量化即数字化;③对得到的数字量进行编码,生成用0和1表示的数字信号。

2.数字信号的描述方法(1)二值数字逻辑和逻辑电平在数字电路中,可以用0和1组成的二进制数表示数量的大小,也可以用0和1表示两种不同的逻辑状态。

在电路中,当信号电压在3.5~5 V 范围内表示高电平;在0~1.5 V 范围内表示低电平。

以高、低电平分别表示逻辑1和0两种状态。

(2)数字波形①数字波形的两种类型非归零码:在一个时间拍内用高电平代表1,低电平代表0。

归零码:在一个时间拍内有脉冲代表1,无脉冲代表0。

②周期性和非周期性周期性数字波形常用周期T 和频率f 来描述。

脉冲波形的脉冲宽度用W t 表示,所以占空比100%t q T=⨯W③实际数字信号波形在实际的数字系统中,数字信号并不理想。

当从低电平跳变到高电平,或从高电平跳到低电平时,边沿没有那么陡峭,而要经历一个过渡过程。

图1-1为非理想脉冲波形。

图1-1 非理想脉冲波形④时序图:表示各信号之间时序关系的波形图称为时序图。

二、数制 1.十进制以10为基数的计数体制称为十进制,其计数规律为“逢十进一”。

任意十进制可表示为:()10iDii N K ∞=-∞=⨯∑式中,i K 可以是0~9中任何一个数字。

如果将上式中的10用字母R 代替,则可以得到任意进制数的表达式:()iR ii N K R ∞=-∞=⨯∑2.二进制(1)二进制的表示方法以2为基数的计数体制称为二进制,其只有0和1两个数码,计数规律为“逢二进一”。

数字电路知识点总结(精华版)数字电路知识点总结(精华版)第一章数字逻辑概论一、进位计数制1.十进制与二进制数的转换2.二进制数与十进制数的转换3.二进制数与十六进制数的转换二、基本逻辑门电路第二章逻辑代数逻辑函数的表示方法有:真值表、函数表达式、卡诺图、逻辑图和波形图等。

一、逻辑代数的基本公式和常用公式1.常量与变量的关系A + 0 = A,A × 1 = AA + 1 = 1,A × 0 = 02.与普通代数相运算规律a。

交换律:A + B = B + A,A × B = B × Ab。

结合律:(A + B) + C = A + (B + C),(A × B) × C = A ×(B × C)c。

分配律:A × (B + C) = A × B + A × C,A + B × C = (A + B) × (A + C)3.逻辑函数的特殊规律a。

同一律:A + A = Ab。

摩根定律:A + B = A × B,A × B = A + Bc。

关于否定的性质:A = A'二、逻辑函数的基本规则代入规则在任何一个逻辑等式中,如果将等式两边同时出现某一变量 A 的地方,都用一个函数 L 表示,则等式仍然成立,这个规则称为代入规则。

例如:A × B ⊕ C + A × B ⊕ C,可令 L = B ⊕ C,则上式变成 A × L + A × L = A ⊕ L = A ⊕ B ⊕ C。

三、逻辑函数的化简——公式化简法公式化简法就是利用逻辑函数的基本公式和常用公式化简逻辑函数,通常,我们将逻辑函数化简为最简的与或表达式。

1.合并项法利用 A + A' = 1 或 A × A' = 0,将二项合并为一项,合并时可消去一个变量。

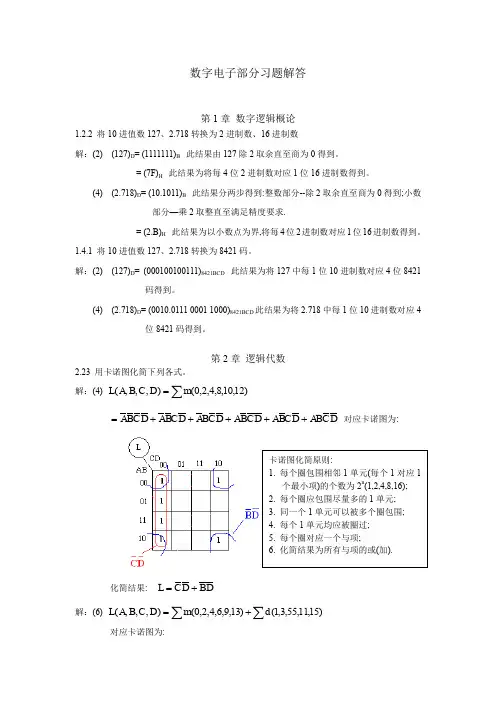

数字电子部分习题解答第1章 数字逻辑概论1.2.2 将10进值数127、2.718转换为2进制数、16进制数解:(2) (127)D = (1111111)B 此结果由127除2取余直至商为0得到。

= (7F)H 此结果为将每4位2进制数对应1位16进制数得到。

(4) (2.718)D = (10.1011)B 此结果分两步得到:整数部分--除2取余直至商为0得到;小数部分—乘2取整直至满足精度要求.= (2.B)H 此结果为以小数点为界,将每4位2进制数对应1位16进制数得到。

1.4.1 将10进值数127、2.718转换为8421码。

解:(2) (127)D = (000100100111)8421BCD 此结果为将127中每1位10进制数对应4位8421码得到。

(4) (2.718)D = (0010.0111 0001 1000)8421BCD 此结果为将2.718中每1位10进制数对应4位8421码得到。

第2章 逻辑代数2.23 用卡诺图化简下列各式。

解:(4) )12,10,8,4,2,0(),,,(∑=m D C B A LD C AB D C B A D C B A D C B A D C B A D C B A +++++= 对应卡诺图为:化简结果: D B D C L +=解:(6) ∑∑+=)15,11,55,3,1()13,9,6,4,2,0(),,,(d m D C B A L对应卡诺图为:化简结果: D A L +=第4章 组合逻辑电路4.4.7 试用一片74HC138实现函数ACD C AB D C B A L +=),,,(4.4.7 试用一片74HC138实现函数ACD C AB D C B A L +=),,,(。

解:将输入变量低3位B 、C 、D 接至74HC138的地址码输入端A 2、A 1、A 0 ,将输入变量高位A 接至使能端E 3,令012==E E ,则有:i i i Am m E E E Y ==123。

1.Introduction to digital logic1.1Digital circuit and digital signal1.2Numerical systems1.3Binary arithmetic operation in1.4Binary Code1.5Binary logic variables and basic logical operation1.6 Logical function and its expression2. Logical algebra and foundation for hardware description language(HDL)2.1 Logic algebra2.2 Karnaugh Map simplification of logical function2.3 Fundamental of Verilog hardware description language3. Logic gates3.1 MOS Logic gate3.2 TTL Logic gate3.3 Emitter coupled logic gate3.4 Gallium arsenide logic gate3.5 Problems concerning logic description3.6 Problems in logic gate application3.7 Description of logic gate by Verilog hardware description language4. Combinational logic circuit4.1 Analysis of combinational logic circuit4.2 Design of combinational logic circuit4.3 Competition risks in combinational logic circuits4.4 Typical integrated combinational logic circuit4.5 Programmable combinational logic devices4.6 Description of combinational logic circuit by Verilog hardware description language 5.Latch and trigger5.1 Bistable memory unit circuit5.2 Latch5.3 Trigger circuit and working principle5.4 Trigger logic function5.5 Description of latch and trigger by Verilog hardware description language6. Sequential logic circuit6.1 Concept of sequential logic circuit6.2 Analysis of synchronous sequential logic circuit6.3 Design of synchronous sequential logic circuit6.4 Analysis of asynchronous sequential logic circuit6.5 Typical integrated sequential logic circuits6.6 Description of sequential logic circuit by Verilog hardware description language6.7 Sequential programmable logic devices7. Memory, complex programmable logic devices and field programmable gate array7.1 ROM7.2 RAM7.3 Complex programmable logic device7.4 Field programmable gate array7.5 Examples for designing programmable device by EDA technique8. Conversion and creation of pulse wave8.1 Monostable trigger8.2 Schmidt trigger8.3 Multi vibrator8.4 555 Timer and its applications9. D/A and A/D Convertors9.1 D/A Convertor9.2 A/D Convertor10. Fundamental for digital system design10.1 Introduction to digital system10.2 Arithmetic state machine10.3 Register transmission language10.4 Realization of digital system by programmable logic devices。

《数字电路》课程教案

教员姓名:专业技术职务:助教

教学进程安排

要形式

(三)真值表:这种把所有可能的条件组合及其对应结果一一列出来的表格叫做真值表。

(四)逻辑符号:实现与逻辑的电路称为与门。

与门的逻辑符号:

二、或逻辑(或运算)

(一)或逻辑的定义:当决定事件(Y )发生的各种条件(A ,B ,C ,…)中,只要有一个或多个条件具备,事件(Y )就发生。

表达式为:

Y=A+B+C+…

开关A ,B 并联控制灯泡Y

对上图所示电路的功能,作如下描述:

“开关A 断开,开关B 也断开,则电灯Y 熄灭,但是,只要有一个开

Y

A B

&

电路图

L=AB

E

A

B

Y

开关A 开关B 灯Y 0 0 0 1 1 0 1 1

0 0 0 1

- 14 -

- 15 -

- 16 -

课堂教学过程设计方案

- 17 -

- 18 -

课堂教学总结。

电子技术基础

第一章数字逻辑概论

1.2 数制

15 二值逻辑变量

1.6 逻辑行数及其表示方法

第二章逻辑代数与硬件描述语言基础

2.1逻辑代数

2.11

2.12

2.13

2.2逻辑函数的卡若图化简发

第三章逻辑门

3.16CMOS漏极开路门和三态输出门电路

第四章

4.1组合逻辑电路的分析

4.2组合电路的设计

4.4若干典型的组合逻辑集成电路

第五章

5.1双稳态存储单元电路

第六章

6.1时许逻辑电路的基本概念

6.2同步时许逻辑电路的分析

6.5.2计数器

第八章

8.1单稳态触发器

8.3多谐振荡器

微机原理与接口技术第一章

1.3.1计算机的基本组成工作

1.3.3危机结构

1.4.1 Intel8088微处理器

第二章

2.1 8088/的寻址方式

第四章

4.1概述

第五章

5.1接口技术的基本概念

5.2输入/输出传送方式

5.3

5.4可编程定时器/技术器芯片8253

5.41 5.4.2 5.4.3

5.5可编程并行输入/输出接口芯片。

数字电子部分习题解答第1章数字逻辑概论1.2.2 将10进值数127、2.718转换为2进制数、16进制数解:(2) (127)D = (1111111)B 此结果由127除2取余直至商为0得到。

= (7F)H 此结果为将每4位2进制数对应1位16进制数得到。

(4) (2.718)D = (10.1011)B 此结果分两步得到:整数部分--除2取余直至商为0得到;小数部分—乘2取整直至满足精度要求.= (2.B)H 此结果为以小数点为界,将每4位2进制数对应1位16进制数得到。

1.4.1 将10进值数127、2.718转换为8421码。

解:(2) (127)D = = (000100100111)(000100100111)8421BCD 此结果为将127中每1位10进制数对应4位8421码得到。

(4) (2.718)D = (0010.0111 0001 1000)8421BCD 此结果为将2.718中每1位10进制数对应4位8421码得到。

第2章逻辑代数2.23 用卡诺图化简下列各式。

解:(4) )12,10,8,4,2,0(),,,(å=m D C B A L D C AB D C B A D C B A D C B A D C B A D C B A +++++=对应卡诺图为: 化简结果: DB DC L +=解:(6) åå+=)15,11,55,3,1()13,9,6,4,2,0(),,,(d m D C B A L 对应卡诺图为: 卡诺图化简原则: 1. 每个圈包围相邻1单元(每个1对应1个最小项)的个数为2n (1,2,4,8,16); 2. 每个圈应包围尽量多的1单元; 3. 同一个1单元可以被多个圈包围; 4. 每个1单元均应被圈过; 5. 每个圈对应一个与项; 6. 化简结果为所有与项的或(加). 化简结果: D A L +=第4章 组合逻辑电路组合逻辑电路4.4.7 试用一片74HC138实现函数ACD C AB D C B A L +=),,,( 4.4.7 试用一片74HC138实现函数ACD C AB D C B A L +=),,,(。