存储器接口

- 格式:ppt

- 大小:4.19 MB

- 文档页数:25

TMS320DM6437 DMP介绍TMS320DM6437 Digital Media Processor—一种高性能数字媒体处理器:VelociTI.2结构DSP内核,先进超长指令字(VLIW)C64x+指令集特性C64x+ L1/L2存储器结构口仅支持小端模式视频处理子系统(VPSS)外部存储器接口(EMIF)增强型直接存储器访问控制器(EDMA):64个独立通道1个64位看门狗定时器2个UART(带RTS和CTS流控信号)主/从I2C总线控制器两个多通道缓冲串行接口(McBSP)多通道音频串行接口(McASP0)高端CAN控制器(HECC)16位主机接口(HPI)32位、33MHz、3.3V PCI主从接口10/100Mb/s以太网MAC(EMAC)VL YNQ接口(FPGA 接口)VL YNQTM接口(FPGA 接口)片上ROM Bootloader独特的节电模式灵活的PLL时钟产生器IEEE-1149.1(JTAG)多达111个GPIO(与其他功能复用)引脚及封装3.3V/1.8V I/O;1.2V/1.05V内部一、DaVinci DM6437 概述TMS320C64x DSP内核:TMS320DM6437是专门为高性能、低成本视频应用开发的、32位定点DSP达芬奇(DaVinci(TM)) 技术的处理器。

该器件采用TI第2代超长指令字(VLIW)结构(VelociTI.2)的TMS320C64x+ DSP内核,主频可达700MHz,支持8个8位或4个16位并行MAC (multiply-accumulates)运算,峰值处理能力高达5600MIPS。

> C64x片内有2个数据通道、8个功能单元和2个通用寄存器文件(A和B)。

8个功能单元(2个乘法器和6个算术逻辑单元)用于提高影像和图像应用的性能。

每个通用寄存器文件包含32个32-bit寄存器。

这些通用寄存器可以用做数据指针或者数据地址指针。

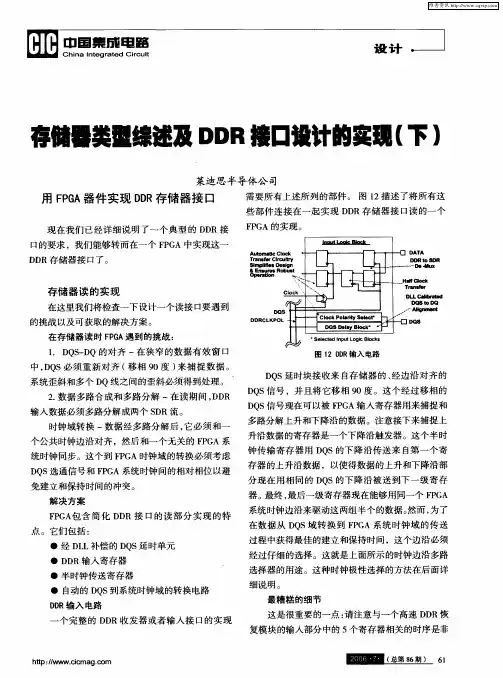

基于FPGA 的DDR2SDRAM 存储器用户接口设计杨斌,段哲民,高峰(西北工业大学电子信息学院,陕西西安710129)摘要:使用功能强大的FPGA 来实现一种DDR2SDRAM 存储器的用户接口。

该用户接口是基于XILINX 公司出产的DDR2SDRAM 的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,可知本设计具有很大的使用前景。

本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速率很高,基本可以满足所有设计需要。

关键词:DDR2SDRAM ;FPGA ;用户接口;DDR2SDRAM 存储控制器中图分类号:TN919.8文献标识码:A文章编号:1674-6236(2012)23-0147-03Design of DDR2SDRAM memory user interface based on FPGAYANG Bin ,DUAN Zhe -min ,GAO Feng(School of Electronic Information ,Northwestern Polytechnical University ,Xi ’an 710129,China )Abstract:The user interface of a DDR2SDRAM memory is implemented by using the powerful FPGA .The user interface is based on DDR2SDRAM memory controller produced by the XILINX company .The company produced such memory controllers with high efficiency and used widely .So that this design has great prospects .Through the simulation of multi -channel high -speed data read and write operations we can know that it can fully meet the timing requirements .Through the synthesis results we can know that the use of logic resources is very little ,run rate is high .It can basically meet all design needs.Key words:DDR2SDRAM ;FPGA ;user interface ;DDR2SDRAM memory controller收稿日期:2012-08-06稿件编号:201208014作者简介:杨斌(1981—),男,陕西佳县人,硕士研究生。

soc中的sram

SRAM(静态随机存储器)是一种常用于计算机系统中的存储器类型,也被广泛应用于系统芯片(SoC)中。

SRAM 是一种易失性存储器,它能够在没有电源的情况下保持数据。

相对于动态随机存储器(DRAM),SRAM 的读写速度更快,因为它使用了一种不需要刷新操作的存储单元设计。

在SoC 中,SRAM 通常用于多个目的,包括:

1. 缓存:SRAM 可以作为高速缓存存储器,用于存储处理器的指令和数据,以提高系统性能。

由于SRAM 的高速读写特性,它可以快速响应处理器的读取请求,减少了对主存储器的访问延迟。

2. 寄存器文件:SRAM 经常被用作寄存器文件,用于存储处理器的寄存器状态。

寄存器文件是计算机体系结构中的一个关键组件,用于存储临时数据、运算结果和控制信号。

3. 存储器接口:SRAM 可以作为与其他外部存储器(如闪存或硬盘驱动器)进行交互的接口。

它可以用作缓冲区或数据传输的中间存储器,以提高数据传输速度。

总之,SRAM 在SoC 中具有重要的作用,可以提供快速的数据存储和访问功能,对于提高系统性能和响应能力非常关键。

1。

51单片机存储器结构介绍单片机是一种微型电脑芯片,他能够实现数字信号的处理和控制。

而存储器是单片机的核心组成部分之一,用于存储程序指令和数据。

本文将介绍51单片机的存储器结构。

一、内部存储器1. 代码存储器(ROM)代码存储器是用来存放程序指令的地方,它通常具有只读的特点,因此称之为只读存储器(Read-Only Memory)。

在51单片机中,常见的ROM有EPROM、EEPROM和Flash。

其中,EPROM需要使用紫外线擦除后才能进行写入操作,而EEPROM和Flash则支持电子擦除和写入操作。

2. 数据存储器(RAM)数据存储器用于存储程序中的数据,可以进行读取和写入操作。

51单片机中的RAM分为内部RAM和外部RAM两种类型。

内部RAM 是静态随机存储器(SRAM),容量通常较小,但读取速度快。

而外部RAM则可以通过外部接口来扩展存储容量。

二、外部存储器除了内部存储器之外,51单片机还支持外部存储器的连接,以扩展存储容量。

1. 并行存储器并行存储器是指通过并行接口与单片机进行数据交换的存储器,常见的有静态随机存储器(SRAM)、动态随机存储器(DRAM)和闪存等。

并行存储器的访问速度较快,但通信线路和引脚较多,连接复杂。

2. 串行存储器串行存储器是通过串行接口与单片机进行数据交换的存储器,常见的有串行EEPROM和串行闪存等。

串行存储器相对于并行存储器来说,引脚和通信线路较少,连接较为简单,但访问速度相对较慢。

三、存储器扩展技术1. 存储器芯片选择在实际应用中,我们需要根据需求选择合适的存储器芯片。

不同的存储器芯片具有不同的特性,比如容量大小、访问速度、耗能情况等,需要根据具体需求进行选择。

2. 存储器接口设计单片机与存储器之间的通信需要通过特定的接口进行连接。

在设计存储器接口时,需要考虑接口的引脚数目、速度要求、稳定性等因素,并且保证接口与存储器芯片的电气特性匹配。

3. 存储器管理技术存储器管理是针对大容量存储器的一种管理方法,用于提高存储效率和数据存取速度。

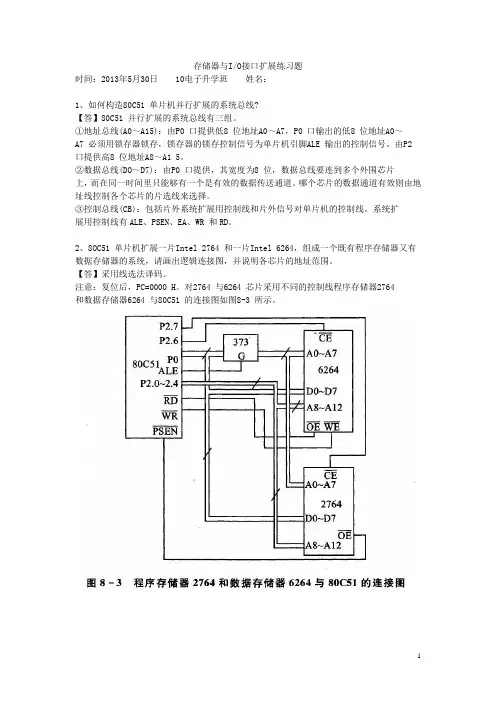

存储器与I/O接口扩展练习题时间:2013年5月30日 10电子升学班姓名:1、如何构造80C51 单片机并行扩展的系统总线?【答】80C51 并行扩展的系统总线有三组。

①地址总线(A0~A15):由P0 口提供低8 位地址A0~A7,P0 口输出的低8 位地址A0~A7 必须用锁存器锁存,锁存器的锁存控制信号为单片机引脚ALE 输出的控制信号。

由P2 口提供高8 位地址A8~A1 5。

②数据总线(DO~D7):由P0 口提供,其宽度为8 位,数据总线要连到多个外围芯片上,而在同一时间里只能够有一个是有效的数据传送通道。

哪个芯片的数据通道有效则由地址线控制各个芯片的片选线来选择。

③控制总线(CB):包括片外系统扩展用控制线和片外信号对单片机的控制线。

系统扩展用控制线有ALE、PSEN、EA、WR 和RD。

2、8OC51 单片机扩展一片Intel 2764 和一片Intel 6264,组成一个既有程序存储器又有数据存储器的系统,请画出逻辑连接图,并说明各芯片的地址范围。

【答】采用线选法译码。

注意:复位后,PC=0000 H。

对2764 与6264 芯片采用不同的控制线程序存储器2764和数据存储器6264 与80C51 的连接图如图8-3 所示。

当P2.7=0,P2.6=0,PSEN=0 时,选中2764,因此,程序存储器2764 地址为0000 H~1FFF H(因为系统中只扩展了一片程序存储器,所以2764 的CE 端也可以直接接地)。

要注意80C51 内部自带程序存储器,当外扩程序存储器2764 地址为0000 H~1FFFH 时,必须将80C51 的EA 引脚接地。

若80C51 的EA 引脚接高电平,则2764 地址为1000 H~2FFF H。

当P2.7=1,P2.6=0,P2.5=1,RD=0 或WR=0 时,选中6264,因此,数据存储器6264地址为A000H~BFFFH。

3、在80C51 单片机系统中,外接程序存储器和外接数据存储器共用16 位地址线A0~A15 和8 位数据线D0~D7,为什么不会发生冲突?【答】因为对外接程序存储器和外接数据存储器采用不同的指令,从而产生不同的控制信号来加以区别。

第10章存储器及其接口典型试题一.填空题1.只读存储器ROM有如下几种类型:____。

答案:掩膜ROM、PROM、EPROM、E2PROM2.半导体存储器的主要技术指标是____。

答案:存储容量、存储速度、可靠性、功耗、性能/价格比3.在16位微机系统中,一个存储字占用两个连续的8位字节单元,字的低8位存放在____、高8位存放在____。

答案:低地址单元、高地址单元4.SRAM芯片6116(2K×8B)有____位地址引脚线、____位数据引脚线。

答案:11 85.在存储器系统中,实现片选控制有三种方法,它们是____。

答案:全译码法、部分译码法、线选法6.74LS138译码器有三个“选择输入端”C、B、A及8个输出端,当输入地址码为101时,输出端____有效。

答案:7.半导体静态存储器是靠____存储信息,半导体动态存储器是靠____存储信息。

答案:触发器电荷存储器件8.对存储器进行读/写时,地址线被分为____和____两部分,它们分别用以产生____和____信号。

答案:片选地址片内地址芯片选择片内存储单元选择二.单项选择题1.DRAM2164(64K×1)外部引脚有()。

A.16条地址线、2条数据线B.8条地址线、1条数据线C.16条地址线、1条数据线D.8条地址线、2条数据线分析:从芯片容量(64K×1B)来看,有64K个编址单元,应有16条地址线(216=64K)。

但DRAM芯片集成度高、容量大、引脚数量不够,一般输入地址线采用分时复用锁存方式,即将地址信号分成二组、共用一组线,分两次送入片内。

而2164却有二条数据线,一条作为输入,一条作为输出。

答案:D 2.8086能寻址内存贮器的最大地址范围为()。

A.64KBB.512KBC.1MBD.16KB分析:8086有20条地址总线A0~A19,它可以表示220=1M个不同的状态。

答案:C3.若用1K×4的芯片组成2K×8的RAM,需要()片。

bitslip用法-回复关于“bitslip用法”的文章引言:在数字通信中,位错是一个常见的问题,它可能会导致数据传输的不完整或错误。

为了解决位错误问题,许多技术和算法被提出,其中一个重要的概念就是bitslip(位滑移)。

本文将详细介绍bitslip的用法,以及它在数字通信中的影响和应用。

一、bitslip的定义和原理bitslip是一种用于数据同步和校正的技术。

当数据在传输过程中发生位错时,bitslip可以通过滑动数据位来重新调整数据的位置,从而恢复原始数据的正确顺序。

它主要通过控制数据的缓冲区和时钟信号来实现。

具体而言,当位错发生时,bitslip可以通过适当的操作来调整数据位,使其与时钟信号同步。

比如,对于串行数据传输,bitslip可以通过向左或向右滑动一个位来校正数据位的位置。

这样一来,位错导致的数据错位问题可以得到修复,数据传输的正确性可以得到保障。

二、bitslip的应用领域bitslip技术在数字通信领域有着广泛的应用,尤其在高速通信和数据接口设计中占据重要地位。

以下是bitslip的一些常见应用领域:1. 存储器接口:bitslip可以应用于存储器接口中,用于处理存储器传输中可能出现的位错问题。

当数据在存储器读取或写入过程中发生位错时,bitslip可以通过调整数据位的位置来恢复数据的正确顺序,从而提高存储器接口的可靠性和性能。

2. 高速串行接口:bitslip在高速串行接口中也有重要的应用。

在高速串行通信中,由于噪声和其他干扰的存在,位错问题经常发生。

bitslip可以通过滑动数据位来恢复正确的数据顺序,从而提高高速串行通信的可靠性和稳定性。

3. 数据同步和时钟恢复:bitslip在数据同步和时钟恢复中也起着关键的作用。

当数据传输中发生位错时,bitslip可以通过调整数据位和时钟信号的位置来恢复数据的同步性和时序准确性,从而确保数据传输的正确性和可靠性。

三、bitslip的使用方法bitslip的具体使用方法因应用场景和具体设备的不同而有所差异。

单片微型计算机原理与接口技术单片微型计算机(Single-Chip Microcomputer,简称SCM)是一种将中央处理器(CPU)、存储器、输入输出(I/O)接口和定时器等功能模块集成在一块芯片上的计算机系统。

它在体积小、功耗低、成本低的同时,具备强大的计算和控制能力,被广泛应用于各行各业。

本文将介绍单片微型计算机的原理和接口技术。

一、单片微型计算机的原理单片微型计算机由CPU、存储器和I/O接口等主要组成部分构成。

在单片微型计算机的原理中,CPU负责执行指令和数据处理,存储器用于存储程序和数据,I/O接口则实现计算机与外部设备之间的数据交互。

1. CPUCPU是单片微型计算机的核心部分,它包含运算器、控制器和寄存器等组件。

运算器负责进行算术和逻辑运算,控制器则协调和控制各个组件的工作,寄存器用于临时存储数据和指令。

2. 存储器存储器是单片微型计算机用来存储程序和数据的地方,主要包括随机存储器(RAM)和只读存储器(ROM)。

RAM具有读写功能,用于存储程序和运行时数据;ROM则用于存储只读数据和程序。

3. I/O接口I/O接口是单片微型计算机与外部设备进行数据交互的通道,常见的接口有串行口、并行口、键盘接口和显示接口等。

通过I/O接口,单片微型计算机能够与各类外设进行数据的输入和输出操作。

二、接口技术单片微型计算机的接口技术是实现计算机与外部设备之间数据交换的重要手段,合理选择和设计接口技术可以提高数据传输效率和系统稳定性。

1. 串行口串行口是一种将数据以比特流的形式进行传输的接口技术。

它适用于数据传输速率较低、线路成本较高、距离较远的场景。

串行口的特点是简单、稳定,适用于与单片微型计算机之间的数据通信。

2. 并行口并行口是一种将数据同时以多位的形式进行传输的接口技术。

它适用于高速数据传输,但在线路布局和噪声干扰等方面有一定的要求。

并行口常用于打印机、显示器等外设与单片微型计算机之间的数据传输。