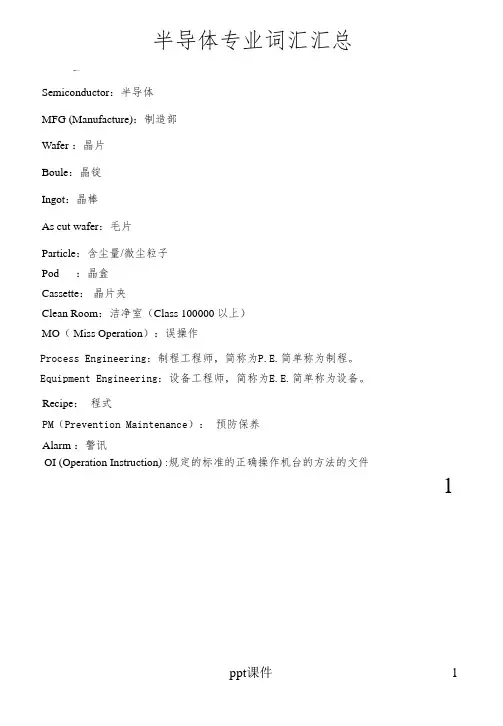

硅片行业术语大全

- 格式:doc

- 大小:51.50 KB

- 文档页数:5

半导体行业内相关名词

1. 微处理器(Microprocessor): 是一种集成电路,用于执行计算机的指令和操作。

2. 芯片(Chip): 是半导体材料上制造的集成电路,可以执行特定的功能。

3. 功率半导体(Power semiconductor): 用于控制和调节电流和电压的半导体器件,常用于电力电子系统和功率放大器等应用。

4. 二极管(Diode): 是一个具有两个电极的电子器件,主要用于限制电流的方向。

5. 晶体管(Transistor): 是一种用于放大和开关电路的半导体器件,常用于电子设备中。

6. MOSFET(金属氧化物半导体场效应晶体管): 是一种常用的功率半导体器件,被广泛应用于电子电路中。

7. LED(Light-emitting diode): 是一种能将电能转化为光能的半导体器件,常用于照明、显示和指示等应用。

8. MEMS(Microelectromechanical systems): 是一种微型机械器件,由微芯片上的微电子器件和微机械系统组成。

9. IC(Integrated circuit): 是一种通过集成电路制造技术将多个电子器件集成在一起制成的器件。

10. Wafer(晶圆):也称为半导体晶圆,是用来制造集成电路和微电子器件的基础材料之一。

以上只是半导体行业内的一些常见名词,还有许多其他名词和专业术语与该行业相关。

3.1 受主acceptor半导体中的一种杂质,她接受从价带激发的电子,形成空穴导电。

3.2 电阻率允许偏差allowable resistivity tolerance晶片中心点或晶锭断面中心点的电阻率与标称电阻率的最大允许差值,它可以用标称值的百分数来表示。

3.3 厚度允许偏差allowable thickness tolerance晶片的中心点厚度与标称值的最大允许差值。

3.4 各向异性anisotropic在不同的结晶学方向有不同物理特性。

又称非各向同性,非均质性。

3.5 各向异性腐蚀anisotropic etch沿着特定的结晶学方向,呈现腐蚀速率增强的一种选择性腐蚀。

3.6 退火annealing改变硅片特性的热过程。

3.7 退火片annealing wafer在惰性气氛或减压气氛下由于高温的作用在近表面形成一个无缺陷(COP)区得硅片。

3.8 脊形崩边apex chip从晶片边缘脱落的任何小块材料的区域。

该区域至少含有2个清晰的内界面,而形成一条或多条清晰交叉线。

3.9 区域沾污area contamination在半导体晶片上,非有意地附加到晶片表面上的物质,它的线度远大于局部光散射体。

区域沾污可以是由吸盘印,手指或手套印迹、污迹、腊或溶剂残留物等形成的晶片表面外来物质。

3.10 区域缺陷area defect无标准定义,参看延伸的光散射体(3.28.6)3.11 氩气退火的硅片argon annealed wafer在氩气气氛下进行高温退火的硅片。

3.12 自掺杂autodoping源自衬底的掺杂剂掺入到外延层中。

自掺杂源可来自衬底的背面、正面以及边缘、反应器中的其它衬片,基座或沉积系统的其它部分。

3.13 背封backseal在硅片背面覆盖一层二氧化硅或其它绝缘体得薄膜,以抑制硅片中主要掺杂剂向外扩散。

3.14 背面backside不推荐使用的术语。

3.15 背表面back surface半导体晶片的背表面,相对于在上面已经或将要制作半导体器件的暴露表面。

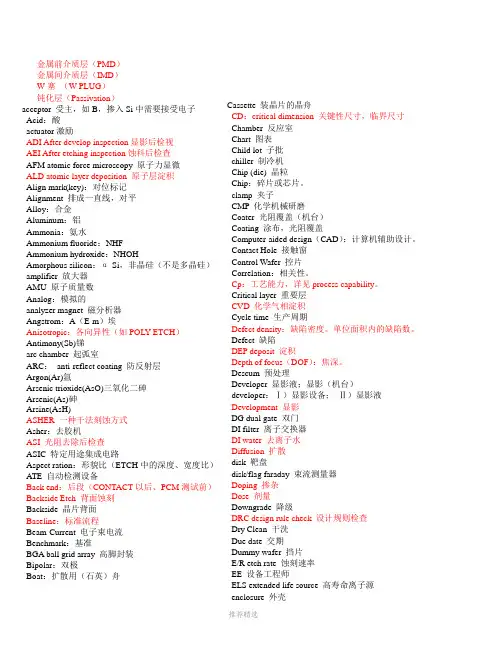

金属前介质层(PMD)金属间介质层(IMD)W 塞(WPLUG)钝化层(PaSSiVaIion)acceptor受主,如B,掺入Si中需要接受电子Acid:酸actuator 激励ADI After develop inspection 显影后检视AEI After etching inspection 蚀科后检查AFM atomic force microscopy 原子力显微ALD atomic layer deposition 原子层淀积Align mark(key):对位标记Alignment排成一直线,对平Alloy:合金Aluminum:铝Ammonia:氨水Ammonium fluoride: NHFAmmonium hydroxide: NHOHAmorphous silicon:α -Si,非晶硅(不是多晶硅) amplifier放大器AMU原子质量数Anak>g:模拟的analyzer magnet 磁分析器Angstrom: A (E-m)埃AniSOtrOPiC:各向异性(如PoLYETCH) Antimony(Sb)Warc chamber 起弧室ARC: anti-reflect coating 防反射层Argon(Ar)MArsenic Eoxide(AsO)三氧化二珅Arsenic(As)WArsine(AsH)Cassette装晶片的晶舟CD: critical dimension关键性尺寸,临界尺寸Chamber反应室Chart图表Child lot 子批chiller制冷机Chip (die)晶粒Chip:碎片或芯片。

clamp夹子CMP化学机械研磨Coater光阻覆盖(机台)Coating涂布,光阻覆盖Computer-aided design (CAD):计算机辅助设计。

Contact Hole 接触窗Control Wafer 控片Correlation:相关性。

半导体行业的英单词和术语1. Semiconductor(半导体):指一种导电性能介于导体和绝缘体之间的材料,广泛应用于电子器件中。

3. Integrated Circuit(集成电路):简称IC,将大量的微小电子元件(如晶体管、电阻、电容等)集成在一块半导体芯片上。

4. Transistor(晶体管):一种半导体器件,具有放大信号和开关功能,是现代电子设备的基础组件。

5. Diode(二极管):一种具有单向导通特性的半导体器件,常用于整流、稳压等电路。

6. MOSFET(金属氧化物半导体场效应晶体管):一种常见的晶体管类型,广泛应用于放大器和开关电路。

7. CMOS(互补金属氧化物半导体):一种集成电路技术,采用NMOS和PMOS晶体管组合,具有低功耗、高集成度等优点。

8. Wafer(晶圆):指经过切割、抛光等工艺处理的半导体材料,用于制造集成电路。

9. Photolithography(光刻):在半导体制造过程中,利用光刻技术将电路图案转移到晶圆上的过程。

10. Etching(刻蚀):在半导体制造过程中,通过化学反应或物理方法去除晶圆表面不需要的材料。

11.掺杂(Doping):在半导体材料中引入其他元素,以改变其导电性能。

12. Chip(芯片):指经过封装的集成电路,是电子设备的核心组成部分。

13. PCB(印刷电路板):一种用于支撑和连接电子元件的板材,上面布满了导电线路。

14. Moore's Law(摩尔定律):指集成电路上可容纳的晶体管数量大约每两年翻一番,预测了半导体行业的发展趋势。

15. EDA(电子设计自动化):指利用计算机软件辅助设计电子系统,包括电路设计、仿真、验证等环节。

16. Foundry(代工厂):专门为其他公司生产半导体芯片的企业。

17. Semiconductor Equipment Manufacturer(半导体设备制造商):为半导体行业提供生产设备的公司。

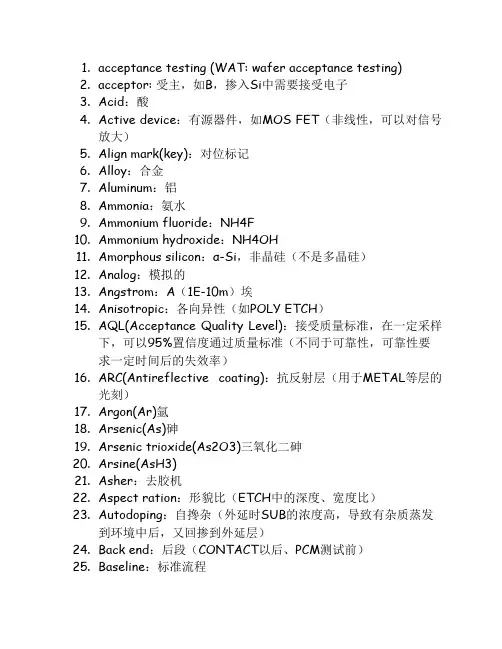

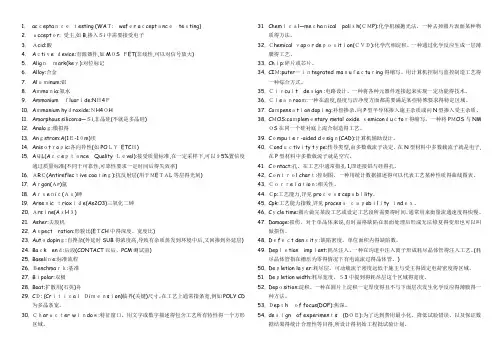

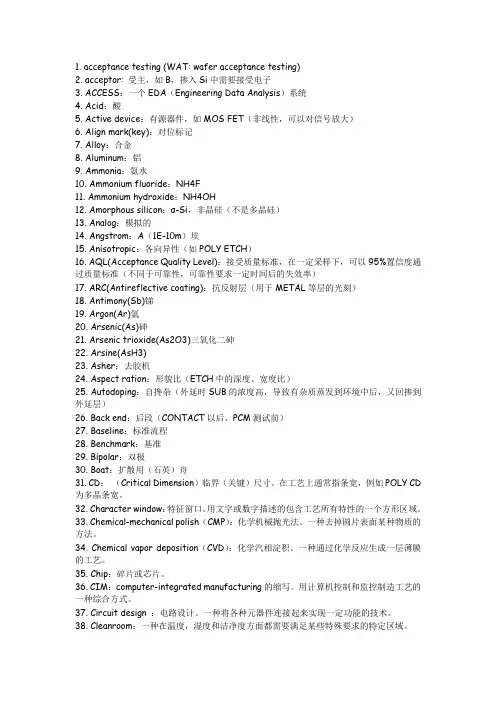

1. acceptance testing (WAT: wafer acceptance testing)2. acceptor: 受主,如B,掺入Si中需要接受电子3. Acid:酸4. Active device:有源器件,如MOS FET(非线性,可以对信号放大)5. Align mark(key):对位标记6. Alloy:合金7. Aluminum:铝8. Ammonia:氨水9. Ammonium fluoride:NH4F10. Ammonium hydroxide:NH4OH11. Amorphous silicon:α-Si,非晶硅(不是多晶硅)12. Analog:模拟的13. Angstrom:A(1E-10m)埃14. Anisotropic:各向异性(如POLY ETCH)15. AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)16. ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)17. Argon(Ar)氩18. Arsenic(As)砷19. Arsenic trioxide(As2O3)三氧化二砷20. Arsine(AsH3)21. Asher:去胶机22. Aspect ration:形貌比(ETCH中的深度、宽度比)23. Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)24. Back end:后段(CONTACT以后、PCM测试前)25. Baseline:标准流程26. Benchmark:基准27. Bipolar:双极28. Boat:扩散用(石英)舟29. CD:(Critical Dimension)临界(关键)尺寸。

在工艺上通常指条宽,例如POLY CD 为多晶条宽。

无锡上机数控股份有限公司硅片不良名称解释工艺培训资料董海杰2017/2/28(内部文件:禁止外泄!)一、硅片加工成片十大过程1.开方2.去头尾3.磨面4.倒角5.粘棒6.切片7.脱胶8.插片9.清洗10.捡片切片加工中硅片质量缺陷名词解释及允许量值一、什么叫外观外观就是要看上去美观无缺陷,具体要求是:表面光滑干净,无明显黑斑、污渍;洁净无残留硅胶、无污染、色斑颜色均匀一致;不允许有明显刀痕、裂纹、裂痕,无凹坑空洞,无边缘毛糙,无V型崩边,无异常晶粒,无亮线等。

二、什么叫崩边(俗称硅落)在一张硅片四周边缘上出现崩缺、缺失的现象叫作崩边。

可以按A、B、C 等级分类,区别严重程度。

允许范围:弧形缺口深度≤0.3mm,长度≤0.5mm,个数≤2个,不允许有“V”型贯穿性崩边缺口和不允许缺角。

贯穿崩边边缘崩边崩边深度长度倒角角崩胶层三、什么叫TTV(俗称厚度不规则)在一张硅片上尺寸厚度变化超过公差要求的叫TTV,检测有9点法和3线法。

允许范围:厚度尺寸195±20um(有的要求195±30um)TTV分类:1、进刀TTV图例(0~30mm)2、片面中间TTV图例(30~120mm)3、出刀TTV图例(120~156mm)1、进刀TTV原因:a进刀线速度太大比例线速太快,线网打滑;b喷嘴位置太远和高低差比较大,喷嘴水帘甩不均匀;c进刀线弓太大,进刀量太大,切割力产生;d粘棒后晶棒出现高低差太大。

解决分析:a调整进刀比例;b调整喷嘴左右、前后的距离,使水帘刚好落到晶棒边缘;c加大进刀新线量;d按照下列表格执行。

2、片面TTV原因:a金刚线切割力不足;b张力问题;c导轮槽磨损过多。

解决分析:a加大金刚线使用量,合理分配工艺步骤里的进回线量;b检查校正张力是否正常;c更换导轮。

3、出刀TTV原因:a喷嘴位置及流量;b金刚线切割力不足;解决分析:a调整喷嘴位置及流量按进刀水帘位置决定,流量6500~7500,避免工艺流量;b增加出刀工艺金刚线使用量。

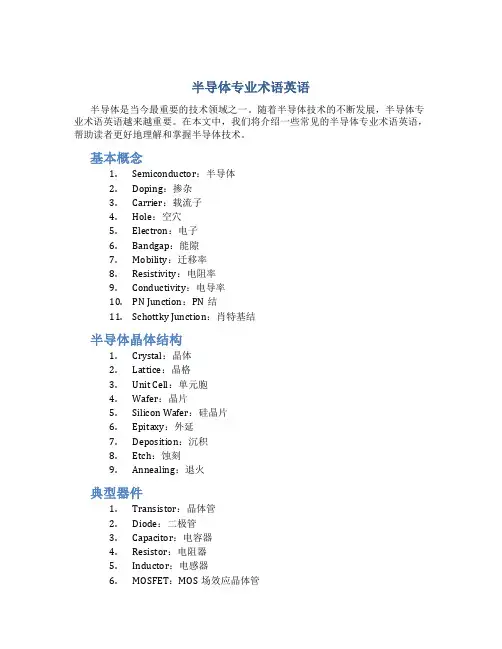

半导体专业术语英语半导体是当今最重要的技术领域之一。

随着半导体技术的不断发展,半导体专业术语英语越来越重要。

在本文中,我们将介绍一些常见的半导体专业术语英语,帮助读者更好地理解和掌握半导体技术。

基本概念1.Semiconductor:半导体2.Doping:掺杂3.Carrier:载流子4.Hole:空穴5.Electron:电子6.Bandgap:能隙7.Mobility:迁移率8.Resistivity:电阻率9.Conductivity:电导率10.PN Junction:PN结11.Schottky Junction:肖特基结半导体晶体结构1.Crystal:晶体ttice:晶格3.Unit Cell:单元胞4.Wafer:晶片5.Silicon Wafer:硅晶片6.Epitaxy:外延7.Deposition:沉积8.Etch:蚀刻9.Annealing:退火典型器件1.Transistor:晶体管2.Diode:二极管3.Capacitor:电容器4.Resistor:电阻器5.Inductor:电感器6.MOSFET:MOS场效应晶体管7.BJT:双极性晶体管8.LED:发光二极管9.IGBT:绝缘栅双极晶体管10.SCR:可控硅制程工艺1.Lithography:光刻2.Ion Implantation:离子注入3.Chemical Vapor Deposition (CVD):化学气相沉积4.Physical Vapor Deposition (PVD):物理气相沉积5.Wet Etch:湿法蚀刻6.Dry Etch:干法蚀刻7.Annealing:退火8.Configurations:构型9.Metrology:计量学10.Yield:良率11.Process Integration:制程集成半导体技术对现代社会的影响越来越大,而英语是半导体专业中的重要工具之一。

学习和掌握半导体专业术语英语,有助于提高在半导体行业的各种交流和合作能力。

1.acceptancetesting (WAT:wafer acceptancetesting)2.acceptor: 受主,如B,掺入Si中需要接受电子3.Acid:酸4.Active device:有源器件,如MOS FET(非线性,可以对信号放大)5.Alignmark(key):对位标记6.Alloy:合金7.Aluminum:铝8.Ammonia:氨水9.Ammoniumfluoride:NH4F10.Ammonium hydroxide:NH4OH11.Amorphous silicon:α—Si,非晶硅(不就是多晶硅)12.Analog:模拟得13.Angstrom:A(1E-10m)埃14.Anisotropic:各向异性(如POLYETCH)15.AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后得失效率)16.ARC(Antireflective coating):抗反射层(用于METAL等层得光刻)17.Argon(Ar)氩18.Arsenic(As)砷19.Arsenic trioxide(As2O3)三氧化二砷20.Arsine(AsH3)21.Asher:去胶机22.Aspect ration:形貌比(ETCH中得深度、宽度比)23.Autodoping:自搀杂(外延时SUB得浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)24.Back end:后段(CONTACT以后、PCM测试前)25.Baseline:标准流程26.Benchmark:基准27.Bipolar:双极28.Boat:扩散用(石英)舟29.CD: (CriticalDimension)临界(关键)尺寸。

在工艺上通常指条宽,例如POLY CD为多晶条宽。

30.Character window:特征窗口。

1. acceptance testing (WAT: wafer acceptance testing)2. acceptor: 受主,如B,掺入Si中需要接受电子3. ACCESS:一个EDA(Engineering Data Analysis)系统4. Acid:酸5. Active device:有源器件,如MOS FET(非线性,可以对信号放大)6. Align mark(key):对位标记7. Alloy:合金8. Aluminum:铝9. Ammonia:氨水10. Ammonium fluoride:NH4F11. Ammonium hydroxide:NH4OH12. Amorphous silicon:α-Si,非晶硅(不是多晶硅)13. Analog:模拟的14. Angstrom:A(1E-10m)埃15. Anisotropic:各向异性(如POLY ETCH)16. AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17. ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)18. Antimony(Sb)锑19. Argon(Ar)氩20. Arsenic(As)砷21. Arsenic trioxide(As2O3)三氧化二砷22. Arsine(AsH3)23. Asher:去胶机24. Aspect ration:形貌比(ETCH中的深度、宽度比)25. Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26. Back end:后段(CONTACT以后、PCM测试前)27. Baseline:标准流程28. Benchmark:基准29. Bipolar:双极30. Boat:扩散用(石英)舟31. CD:(Critical Dimension)临界(关键)尺寸。

金属前介质层(PMD)金属间介质层(IMD)W塞(W PLUG)钝化层(Passivation)acceptor 受主,如B,掺入Si中需要接受电子Acid:酸actuator激励ADI After develop inspection显影后检视AEI After etching inspection蚀科后检查AFM atomic force microscopy 原子力显微ALD atomic layer deposition 原子层淀积Align mark(key):对位标记Alignment 排成一直线,对平Alloy:合金Aluminum:铝Ammonia:氨水Ammonium fluoride:NHFAmmonium hydroxide:NHOHAmorphous silicon:α-Si,非晶硅(不是多晶硅)amplifier 放大器AMU 原子质量数Analog:模拟的analyzer magnet 磁分析器Angstrom:A(E-m)埃Anisotropic:各向异性(如POL Y ETCH)Antimony(Sb)锑arc chamber 起弧室ARC:anti-reflect coating 防反射层Argon(Ar)氩Arsenic trioxide(AsO)三氧化二砷Arsenic(As)砷Arsine(AsH)ASHER 一种干法刻蚀方式Asher:去胶机ASI 光阻去除后检查ASIC 特定用途集成电路Aspect ration:形貌比(ETCH中的深度、宽度比)ATE 自动检测设备Back end:后段(CONTACT以后、PCM测试前)Backside Etch 背面蚀刻Backside 晶片背面Baseline:标准流程Beam-Current 电子束电流Benchmark:基准BGA ball grid array 高脚封装Bipolar:双极Boat:扩散用(石英)舟Cassette 装晶片的晶舟CD:critical dimension 关键性尺寸,临界尺寸Chamber 反应室Chart 图表Child lot 子批chiller 制冷机Chip (die) 晶粒Chip:碎片或芯片。

1. acceptance testing (WAT: wafer acceptance testing)2. acceptor: 受主,如B,掺入Si中需要接受电子3. ACCESS:一个EDA(Engineering Data Analysis)系统4. Acid:酸5. Active device:有源器件,如MOS FET(非线性,可以对信号放大)6. Align mark(key):对位标记7. Alloy:合金8. Aluminum:铝9. Ammonia:氨水10. Ammonium fluoride:NH4F11. Ammonium hydroxide:NH4OH12. Amorphous silicon:α-Si,非晶硅(不是多晶硅)13. Analog:模拟的14. Angstrom:A(1E-10m)埃15. Anisotropic:各向异性(如POLY ETCH)16. AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17. ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)18. Antimony(Sb)锑19. Argon(Ar)氩20. Arsenic(As)砷21. Arsenic trioxide(As2O3)三氧化二砷22. Arsine(AsH3)23. Asher:去胶机24. Aspect ration:形貌比(ETCH中的深度、宽度比)25. Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26. Back end:后段(CONTACT以后、PCM测试前)27. Baseline:标准流程28. Benchmark:基准29. Bipolar:双极30. Boat:扩散用(石英)舟31. CD:(Critical Dimension)临界(关键)尺寸。

Fab厂常用术语some phrases and words in FAB cleanroom systemA.M.U 原子质量数ADI After develop inspection显影后检视AEI 蚀科后检查Alignment 排成一直线,对平Alloy 融合:电压与电流成线性关系,降低接触的阻值ARC:anti-reflect coating 防反射层ASHER: 一种干法刻蚀方式ASI 光阻去除后检查Backside 晶片背面Backside Etch 背面蚀刻Beam-Current 电子束电流BPSG: 含有硼磷的硅玻璃Break 中断,stepper机台内中途停止键Cassette 装晶片的晶舟CD:critical dimension 关键性尺寸Chamber 反应室Chart 图表Child lot 子批Chip (die) 晶粒CMP 化学机械研磨Coater 光阻覆盖(机台)Coating 涂布,光阻覆盖Contact Hole 接触窗Control Wafer 控片Critical layer 重要层CVD 化学气相淀积Cycle time 生产周期Defect 缺陷DEP: deposit 淀积Descum 预处理Developer 显影液;显影(机台)Development 显影DG: dual gate 双门DI water 去离子水Diffusion 扩散Doping 掺杂Dose 剂量Downgrade 降级DRC: design rule check 设计规则检查Dry Clean 干洗Due date 交期Dummy wafer 挡片E/R: etch rate 蚀刻速率EE 设备工程师End Point 蚀刻终点ESD: electrostatic discharge/electrostatic damage 静电离子损伤ET: etch 蚀刻Exhaust 排气(将管路中的空气排除)Exposure 曝光FAB 工厂FIB: focused ion beam 聚焦离子束Field Oxide 场氧化层Flatness 平坦度Focus 焦距Foundry 代工FSG: 含有氟的硅玻璃Furnace 炉管GOI: gate oxide integrity 门氧化层完整性Hexamethyldisilazane,经去水烘烤的晶片,将涂上一层增加光阻与晶片表面附着力的化合物,称HCI: hot carrier injection 热载流子注入HDP:high density plasma 高密度等离子体High-V oltage 高压Hot bake 烘烤ID 辨认,鉴定Implant 植入Layer 层次LDD: lightly doped drain 轻掺杂漏Local defocus 局部失焦因机台或晶片造成之脏污LOCOS: local oxidation of silicon 局部氧化Loop 巡路Lot 批Mask (reticle) 光罩Merge 合并Metal Via 金属接触窗MFG 制造部Mid-Current 中电流Module 部门NIT: Si3N4 氮化硅Non-critical 非重要NP: n-doped plus(N+) N型重掺杂NW: n-doped well N阱OD: oxide definition 定义氧化层OM: optic microscope 光学显微镜OOC 超出控制界线OOS 超出规格界线Over Etch 过蚀刻Over flow 溢出Overlay 测量前层与本层之间曝光的准确度OX: SiO2 二氧化硅P.R. Photo resisit 光阻P1: poly 多晶硅PA; passivation 钝化层Parent lot 母批Particle 含尘量/微尘粒子PE: 1. process engineer; 2. plasma enhance 1、工艺工程师2、等离子体增强PH: photo 黄光或微影Pilot 实验的Plasma 电浆Pod 装晶舟与晶片的盒子Polymer 聚合物POR Process of recordPP: p-doped plus(P+) P型重掺杂PR: photo resist 光阻PVD 物理气相淀积PW: p-doped well P阱Queue time 等待时间R/C: runcard 运作卡Recipe 程式Release 放行Resistance 电阻Reticle 光罩RF 射频RM: remove. 消除Rotation 旋转RTA: rapid thermal anneal 迅速热退火RTP: rapid thermal process 迅速热处理SA: salicide 硅化金属SAB: salicide block 硅化金属阻止区SAC: sacrifice layer 牺牲层Scratch 刮伤Selectivity 选择比SEM:scanning electron microscope 扫描式电子显微镜Slot 槽位Source-Head 离子源SPC 制程统计管制Spin 旋转Spin Dry 旋干Sputter 溅射SR Si rich oxide 富氧硅Stocker 仓储。

半导体专业术语

1. “晶圆”呀,就像半导体世界的大舞台,各种芯片都要在这上面表演呢!比如你手机里的芯片,就是在晶圆上诞生的哟。

2. “光刻”不就是给半导体画画嘛,精细得很嘞!你想想看,能把那么复杂的电路画得那么准确,是不是很厉害呀!就像一个超级厉害的画家。

3. “掺杂”,这就像是给半导体加点特别的调料,让它有不同的性能呢!好比做菜,加点盐味道就不一样了,掺杂能让半导体变得更独特哦。

4. “封装”,可以说是给半导体穿上保护衣啦!就像给宝贝手机套上手机壳一样,能保护里面的芯片好好工作呀。

5. “MOSFET”,这可是半导体里的大明星呢!很多电子设备都离不开它,它就像一个超级能干的小助手,默默地奉献着。

比如电脑里就有它在努力工作哦。

6. “PN 结”,就像是半导体里的一道神奇关卡,控制着电流的通过呢!就像小区门口的保安,决定谁能进出一样。

7. “蚀刻”,这简直就是给半导体做雕刻呀,把不需要的部分去掉,留下精华!就像雕刻大师精心雕琢作品一样。

8. “半导体器件”,那可是各种各样的宝贝呀!从小小的二极管到复杂的集成电路,它们就像一个神奇的宝库,给我们的生活带来便利。

你家里的电器里肯定有它们的身影呢!

9. “禁带宽度”,这就像是半导体的一个小秘密,决定了它的很多特性呢!是不是很神秘呀?

10. “外延生长”,可以想象成让半导体像小树苗一样长大,变得更强大更优秀!是不是很有意思呀?。

半导体封装不良术语半导体封装是指将硅片上的芯片封装在包裹材料中,以保护芯片并提供连接电路的技术。

在半导体封装过程中,可能会出现一些不良现象和术语。

下面是一些常见的半导体封装不良术语:1.基材开裂:在封装过程中,基材(如硅片或基板)会发生开裂现象。

这可能是由于温度变化、机械应力或材料瑕疵等原因引起的。

基材开裂会导致封装失效和电性能下降。

2.焊点开裂:焊点是连接芯片和封装材料的重要部分。

如果焊点出现开裂现象,则会导致芯片与封装材料之间的连接不良,从而影响电性能和可靠性。

3.内应力:封装材料在固化过程中会产生一定的内应力。

如果内应力过大,则可能导致封装材料的开裂、位移或变形,从而影响封装质量和芯片性能。

4.气泡:在封装材料中产生的气泡可能会导致封装结构不密封。

气泡通常由残留的挥发性物质或有机杂质引起,会使封装材料的绝缘性能下降,从而对芯片的电性能和可靠性产生负面影响。

5.异物:在封装过程中,可能会有杂质或异物进入封装材料中。

这些异物可能来自环境、生产设备或操作人员,如灰尘、化学物质残留或金属碎屑等。

异物会导致封装材料的绝缘性能下降,同时还可能引起短路、失效和降低芯片可靠性。

6.未覆盖敏感区域:在封装过程中,有些芯片可能具有敏感区域,需要特殊处理,如保护盖或金属屏蔽层。

如果这些敏感区域未得到适当的保护或覆盖,可能会引起电磁干扰、电气失效或硬件故障。

7.漏胶:封装材料在封装过程中可能会发生漏胶现象,即封装材料未充分填充到封装结构内部,导致封装不完整或存在孔隙。

漏胶会导致封装结构不牢固,可能引起失效、短路或电性能下降。

8.异常电气性能:封装过程中可能会出现异常的电气性能,如电阻值过大、电容值不稳定或电感值异常等。

这些异常可能是由封装材料的质量问题、设备故障或操作错误等原因引起的。

9.封装不良率:封装不良率是指封装过程中出现的不良产品数量与总产量之比。

封装不良率高可能是由于生产设备的问题、操作人员的技术水平不高或材料质量的问题等引起的。

半导体行业英语专业术语1.Angle of incidence:入射角。

2.Dielectric:介电质。

3.Epitaxial Growth:外延生长。

4.Junction:结。

5.MOS transistor:MOS晶体管。

6.Lithography:光刻。

7.Photoresist:光刻胶。

8.Picking:取片。

9.Reflow soldering:热风焊接。

10.Deposition:沉积。

11.Diffusion:扩散。

12.Doping:掺杂。

13.Epitaxy:外延。

14.Furnace:炉。

15.Gate oxide:栅极氧化层。

16.Grinding:研磨。

17.Ion Implantation:离子注入。

18.Polishing:抛光。

19.Substrate:基底。

20.Chip:芯片。

21.Wafer:晶圆。

22.Yield:良率。

23.Masking:掩模。

24.Electrical Characterization:电性测试。

25.Suitability Test:可靠性测试。

26.Failure Analysis:失效分析。

27.Annealing:退火。

28.Threshold Voltage:阈值电压。

29.Voltage Transfer Curve:电压传递曲线。

30.Contact Resistance:接触电阻。

31.Electromigration:电迁移。

32.Inspection:检验。

33.CMP:表面处理。

34.CVD:化学气相沉积。

35.Metallization:金属化。

36.Microscopy:显微镜。

37.Ohmic Contact:正性接触。

38.Oxidation:氧化。

39.PECVD:电演化学气相沉积。

40.Photolithography:光刻工艺。

41.Sputtering:溅射。

42.Thermal Oxidation:热氧化。

硅片行业术语大全(中英文对照 A-H) Acceptor - An element, such as boron, indium, and gallium used to create a free hole in a semiconductor. The acceptor atoms are required to have one less valence electron than the semiconductor. 受主 - 一种用来在半导体中形成空穴的元素,比如硼、铟和镓。受主原子必须比半导体元素少一价电子 Alignment Precision - Displacement of patterns that occurs during the photolithography process. 套准精度 - 在光刻工艺中转移图形的精度。 Anisotropic - A process of etching that has very little or no undercutting 各向异性 - 在蚀刻过程中,只做少量或不做侧向凹刻。 Area Contamination - Any foreign particles or material that are found on the surface of a wafer. This is viewed as discolored or smudged, and it is the result of stains, fingerprints, water spots, etc. 沾污区域 - 任何在晶圆片表面的外来粒子或物质。由沾污、手印和水滴产生的污染。 Azimuth, in Ellipsometry - The angle measured between the plane of incidence and the major axis of the ellipse. 椭圆方位角 - 测量入射面和主晶轴之间的角度。 Backside - The bottom surface of a silicon wafer. (Note: This term is not preferred; instead, use „back surface‟.) 背面 - 晶圆片的底部表面。(注:不推荐该术语,建议使用“背部表面”) Base Silicon Layer - The silicon wafer that is located underneath the insulator layer, which supports the silicon film on top of the wafer. 底部硅层 - 在绝缘层下部的晶圆片,是顶部硅层的基础。 Bipolar - Transistors that are able to use both holes and electrons as charge carriers. 双极晶体管 - 能够采用空穴和电子传导电荷的晶体管。 Bonded Wafers - Two silicon wafers that have been bonded together by silicon dioxide, which acts as an insulating layer. 绑定晶圆片 - 两个晶圆片通过二氧化硅层结合到一起,作为绝缘层。 Bonding Interface - The area where the bonding of two wafers occurs. 绑定面 - 两个晶圆片结合的接触区。 Buried Layer - A path of low resistance for a current moving in a device. Many of these dopants are antimony and arsenic. 埋层 - 为了电路电流流动而形成的低电阻路径,搀杂剂是锑和砷。 Buried Oxide Layer (BOX) - The layer that insulates between the two wafers. 氧化埋层(BOX) - 在两个晶圆片间的绝缘层。 Carrier - Valence holes and conduction electrons that are capable of carrying a charge through a solid surface in a silicon wafer. 载流子 - 晶圆片中用来传导电流的空穴或电子。 Chemical-Mechanical Polish (CMP) - A process of flattening and polishing wafers that utilizes both chemical removal and mechanical buffing. It is used during the fabrication process. 化学-机械抛光(CMP) - 平整和抛光晶圆片的工艺,采用化学移除和机械抛光两种方式。此工艺在前道工艺中使用。 Chuck Mark - A mark found on either surface of a wafer, caused by either a robotic end effector, a chuck, or a wand. 卡盘痕迹 - 在晶圆片任意表面发现的由机械手、卡盘或托盘造成的痕迹。 Cleavage Plane - A fracture plane that is preferred. 解理面 - 破裂面 Crack - A mark found on a wafer that is greater than 0.25 mm in length. 裂纹 - 长度大于0.25毫米的晶圆片表面微痕。 Crater - Visible under diffused illumination, a surface imperfection on a wafer that can be distinguished individually. 微坑 - 在扩散照明下可见的,晶圆片表面可区分的缺陷。 Conductivity (electrical) - A measurement of how easily charge carriers can flow throughout a material. 传导性(电学方面) - 一种关于载流子通过物质难易度的测量指标 。 Conductivity Type - The type of charge carriers in a wafer, such as “N-type” and “P-type”. 导电类型 - 晶圆片中载流子的类型,N型和P型。 Contaminant, Particulate (see light point defect) 污染微粒 (参见光点缺陷) Contamination Area - An area that contains particles that can negatively affect the characteristics of a silicon wafer. 沾污区域 - 部分晶圆片区域被颗粒沾污,造成不利特性影响。 Contamination Particulate - Particles found on the surface of a silicon wafer. 沾污颗粒 - 晶圆片表面上的颗粒。 Crystal Defect - Parts of the crystal that contain vacancies and dislocations that can have an impact on a circuit‟s electrical performance. 晶体缺陷 - 部分晶体包含的、会影响电路性能的空隙和层错。 Crystal Indices (see Miller indices) 晶体指数 (参见米勒指数) Depletion Layer - A region on a wafer that contains an electrical field that sweeps out charge carriers. 耗尽层 - 晶圆片上的电场区域,此区域排除载流子。 Dimple - A concave depression found on the surface of a wafer that is visible to the eye under the correct lighting conditions. 表面起伏 - 在合适的光线下通过肉眼可以发现的晶圆片表面凹陷。 Donor - A contaminate that has donated extra “free” electrons, thus making a wafer “N-Type”. 施主 - 可提供“自由”电子的搀杂物,使晶圆片呈现为N型。 Dopant - An element that contributes an electron or a hole to the conduction process, thus altering the conductivity. Dopants for silicon wafers are found in Groups III and V of the Periodic Table of the Elements. 搀杂剂 - 可以为传导过程提供电子或空穴的元素,此元素可以改变传导特性。晶圆片搀杂 剂可以在元素周期表的III 和 V族元素中发现。 Doping - The process of the donation of an electron or hole to the conduction process by a dopant. 掺杂 - 把搀杂剂掺入半导体,通常通过扩散或离子注入工艺实现。 Edge Chip and Indent - An edge imperfection that is greater than 0.25 mm. 芯片边缘和缩进 - 晶片中不完整的边缘部分超过0.25毫米。 Edge Exclusion Area - The area located between the fixed quality area and the periphery of a wafer. (This varies according to the dimensions of the wafer.) 边缘排除区域 - 位于质量保证区和晶圆片外围之间的区域。(根据晶圆片的尺寸不同而有所不同。) Edge Exclusion, Nominal (EE) - The distance between the fixed quality area and the periphery of a wafer. 名义上边缘排除(EE) - 质量保证区和晶圆片外围之间的距离。 Edge Profile - The edges of two bonded wafers that have been shaped either chemically or mechanically. 边缘轮廓 - 通过化学或机械方法连接起来的两个晶圆片边缘。 Etch - A process of chemical reactions or physical removal to rid the wafer of excess materials. 蚀刻 - 通过化学反应或物理方法去除晶圆片的多余物质。 Fixed Quality Area (FQA) - The area that is most central on a wafer surface. 质量保证区(FQA) - 晶圆片表面中央的大部分。 Flat - A section of the perimeter of a wafer that has been removed for wafer orientation purposes. 平边 - 晶圆片圆周上的一个小平面,作为晶向定位的依据。 Flat Diameter - The measurement from the center of the flat through the center of the wafer to the opposite edge of the wafer. (Perpendicular to the flat) 平口直径 - 由小平面的中心通过晶圆片中心到对面边缘的直线距离。 Four-Point Probe - Test equipment used to test resistivity of wafers. 四探针 - 测量半导体晶片表面电阻的设备。 Furnace and Thermal Processes - Equipment with a temperature gauge used for processing wafers. A constant temperature is required for the process. 炉管和热处理 - 温度测量的工艺设备,具有恒定的处理温度。 Front Side - The top side of a silicon wafer. (This term is not preferred; use front surface instead.) 正面 - 晶圆片的顶部表面(此术语不推荐,建议使用“前部表面”)。 Goniometer - An instrument used in measuring angles.